"TMS416809高速DRAM芯片规格及性能综述"

需积分: 0 170 浏览量

更新于2023-12-14

4

收藏 398KB PDF 举报

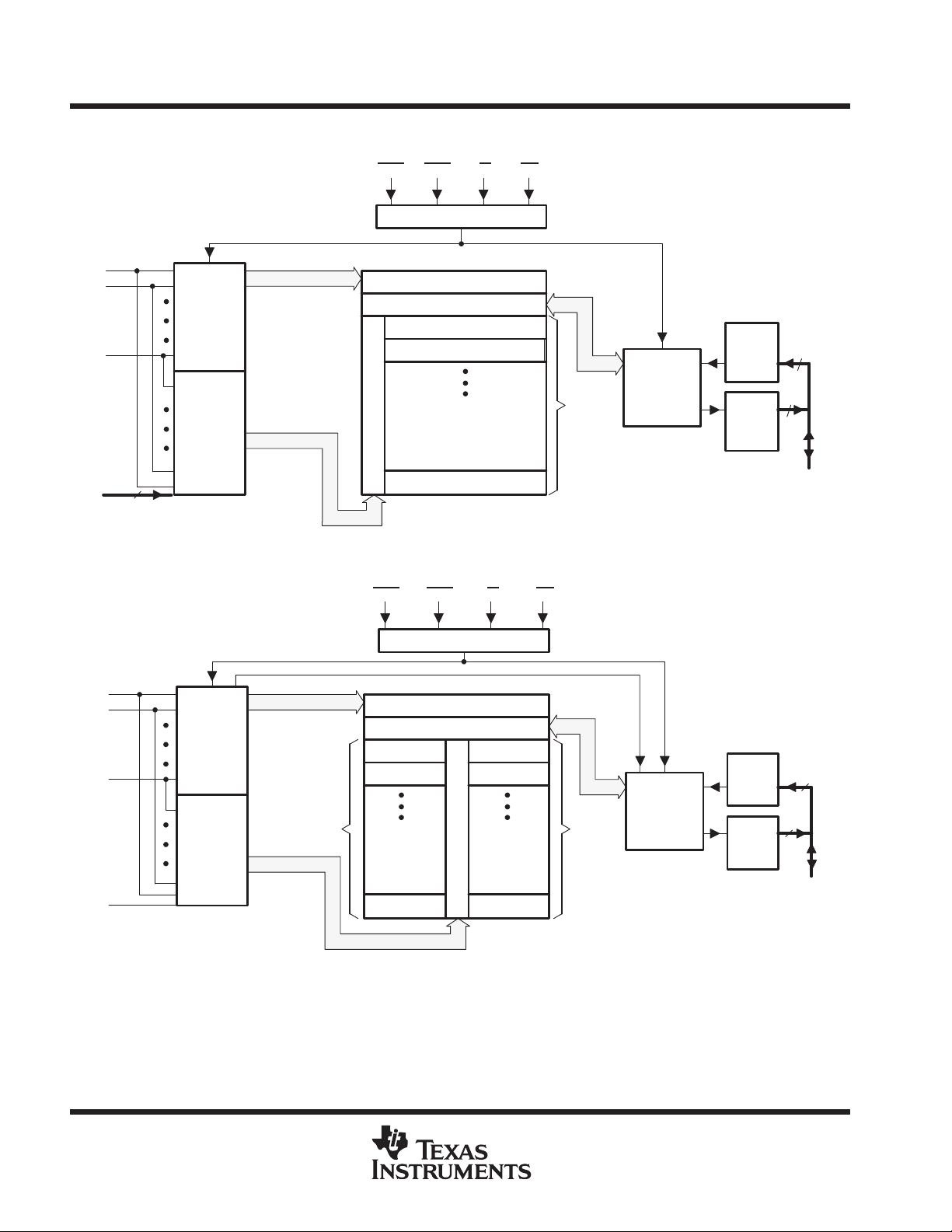

TI-TMS416809.pdf is a document detailing the specifications of the TMS416809 and TMS4178092097152-WORD BY 8-BIT HIGH-SPEED DRAMs. The document was first published in December 1995 and revised in March 1996 by Texas Instruments. The organization of the DRAM is 2097152 × 8, and it operates on a single 5V power supply with a ±10% tolerance.

The performance ranges of the DRAM are as follows:

- Access time for the TMS416809-60: 60ns, tRAC = 15ns, tCAC = 30ns, tAA = 25ns, tHPC = 30ns

- Access time for the TMS416809-70: 70ns, tRAC = 18ns, tCAC = 35ns, tAA = 30ns, tHPC = 35ns

- Access time for the TMS416809-80: 80ns, tRAC = 20ns, tCAC = 40ns, tAA = 35ns, tHPC = 35ns

The DRAM also supports Extended Data Out (EDO) operation, CAS-Before-RAS (CBR) refresh, and a high-impedance state Unlatc.

Overall, the TI-TMS416809.pdf provides detailed information on the specifications and performance of the TMS416809 and TMS4178092097152-WORD BY 8-BIT HIGH-SPEED DRAMs, making it a valuable resource for engineers and designers working with high-speed memory solutions.

2022-12-15 上传

2022-12-15 上传

2022-12-10 上传

2022-12-10 上传

2022-12-10 上传

2022-12-10 上传

2022-12-10 上传

不觉明了

- 粉丝: 3998

- 资源: 5759

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载