Modelsim入门教程:从代码仿真到时序验证

需积分: 9 62 浏览量

更新于2024-09-14

1

收藏 288KB DOC 举报

"Modelsim使用简明指南,涵盖了代码仿真、门级仿真和时序验证的基础操作,适合初学者入门。"

ModelSim是一款强大的逻辑仿真工具,被广泛应用于数字电路设计领域,尤其对于VHDL和Verilog HDL代码的验证。本指南将帮助你快速了解如何使用ModelSim进行仿真。

1. **代码仿真**

代码仿真是验证设计功能的第一步,它直接基于源代码进行,便于早期发现设计问题。进行代码仿真,你需要以下文件:

- 设计的HDL源代码(VHDL或Verilog)

- 测试激励代码,用于模拟设计输入输出

- 仿真模型/库,包含设计中使用的特定器件模块

2.1 **代码仿真步骤**

- **建立工程**:在ModelSim中创建项目,填写项目名称,选择工作目录,并设置默认库为`work`。

- **添加文件**:将源代码和测试激励文件添加到项目中。

- **编译**:编译所有源代码和库文件,确保没有语法错误和逻辑问题。

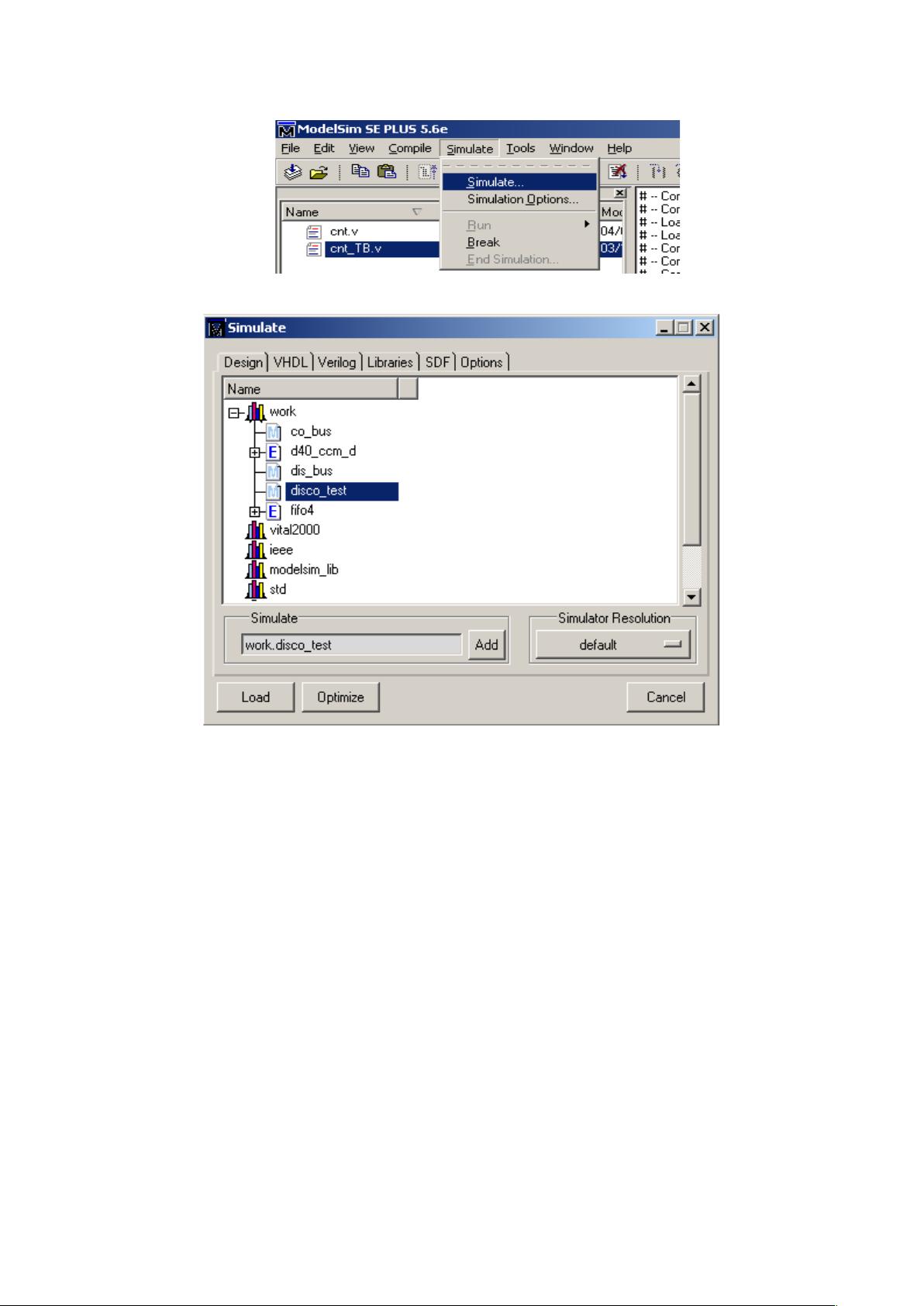

- **装载文件**:在Simulate菜单中选择要仿真运行的顶层文件。

- **开始仿真**:打开Structure、Signals和Wave窗口,进行仿真运行和结果查看。

2. **门级仿真**

门级仿真是在代码经过综合后的层次,它使用实际门级表示来验证设计,更接近实际硬件行为。在这个阶段,设计已经被转换成逻辑门和触发器的网络,速度通常比代码仿真慢,但提供了更准确的性能估计。

- 首先,你需要综合后的网表文件。

- 然后,类似代码仿真,加载网表并进行仿真。

- 结果分析同样通过Structure、Signals和Wave窗口进行。

3. **时序验证**

时序验证关注设计的时序特性,例如时钟周期、延迟和同步问题。它通过专门的时序分析工具进行,确保设计满足时序约束。

- 使用ModelSim的时序分析功能,设置时钟和边沿触发条件。

- 运行仿真,观察关键路径和时序违例。

- 调整设计参数或时序约束以优化时序性能。

在ModelSim中,你可以利用波形窗口(Wave)观察信号变化,结构窗口(Structure)查看设计层次,信号窗口(Signals)监控特定信号状态。通过这些工具,可以深入理解设计行为并进行问题定位。

ModelSim提供了一个集成的环境,使得设计者能够方便地进行HDL代码的验证和优化,从而在设计流程的早期发现和修复问题,提高设计质量。通过熟悉和掌握这些基本操作,你将在数字系统设计中更加得心应手。

2010-03-18 上传

2010-02-09 上传

134 浏览量

2012-01-03 上传

144 浏览量

324 浏览量

122 浏览量

133 浏览量

2011-06-17 上传

topgunal

- 粉丝: 0

最新资源

- Realm实时地图视图集群ABFRealmMapView解析

- 全面详尽软件工程课件,自学软考必备资料

- VB编写的多班次企业轮值日历查询系统

- Upptime:自托管的开源正常运行时间监控与状态页面解决方案

- 浙江大学数据结构MOOC课件下载指南

- 乐鑫ESP射频测试及认证指南详解

- Python客户端简化Atlassian Stash REST API操作

- DWZShareKit:iOS端实现主流社交平台分享功能

- HTML基础与网页制作教程全解析

- 掌握GAWK:第4.2版AWK编程指南

- InsPro Disk:小巧实用的虚拟磁盘学习工具

- ASP网站注册自动生成二维码解决方案

- 打造电影数据库API:简化电影数据管理

- WN821N V4无线网卡驱动下载指南

- C#实现的双行显示简易计算器

- 晨风星号密码查看器:Windows平台下的密码恢复神器