优化时钟偏移提升同步电路性能:非零CLOCK+SKEW策略

需积分: 11 27 浏览量

更新于2024-08-29

收藏 90KB PDF 举报

在现代数字集成电路设计中,时钟同步(Clocks and Skew, CLK-SKEW)是一个至关重要的考虑因素。同步电路的设计质量直接影响着系统的性能、可靠性和速度。本文《同步电路设计中CLOCKSKEW的分析》由康军、黄克勤和张嗣忠撰写,着重探讨了在同步电路设计过程中,零时钟偏移(Clock Skew = 0)与非零时钟偏移两种情况下,时钟分布对电路性能的影响。

首先,作者强调了时钟偏移在电路设计中的作用,它指的是在系统中,由于制造过程、布局布线等因素导致的不同部分接收到时钟信号的时间差异。这种差异如果不加控制,可能会引起数据包的错误接收,降低系统稳定性,甚至限制最大工作频率。

在对比分析中,他们发现零时钟偏移的情况理论上提供了一种理想的同步状态,但在实际应用中,由于制造过程的不确定性,实现零时钟偏移往往是困难的。相比之下,非零时钟偏移虽然会引入一定程度的性能损失,但通过优化时钟树结构、调整延迟路径以及采用先进的补偿技术,可以有效地管理并减小这种影响。

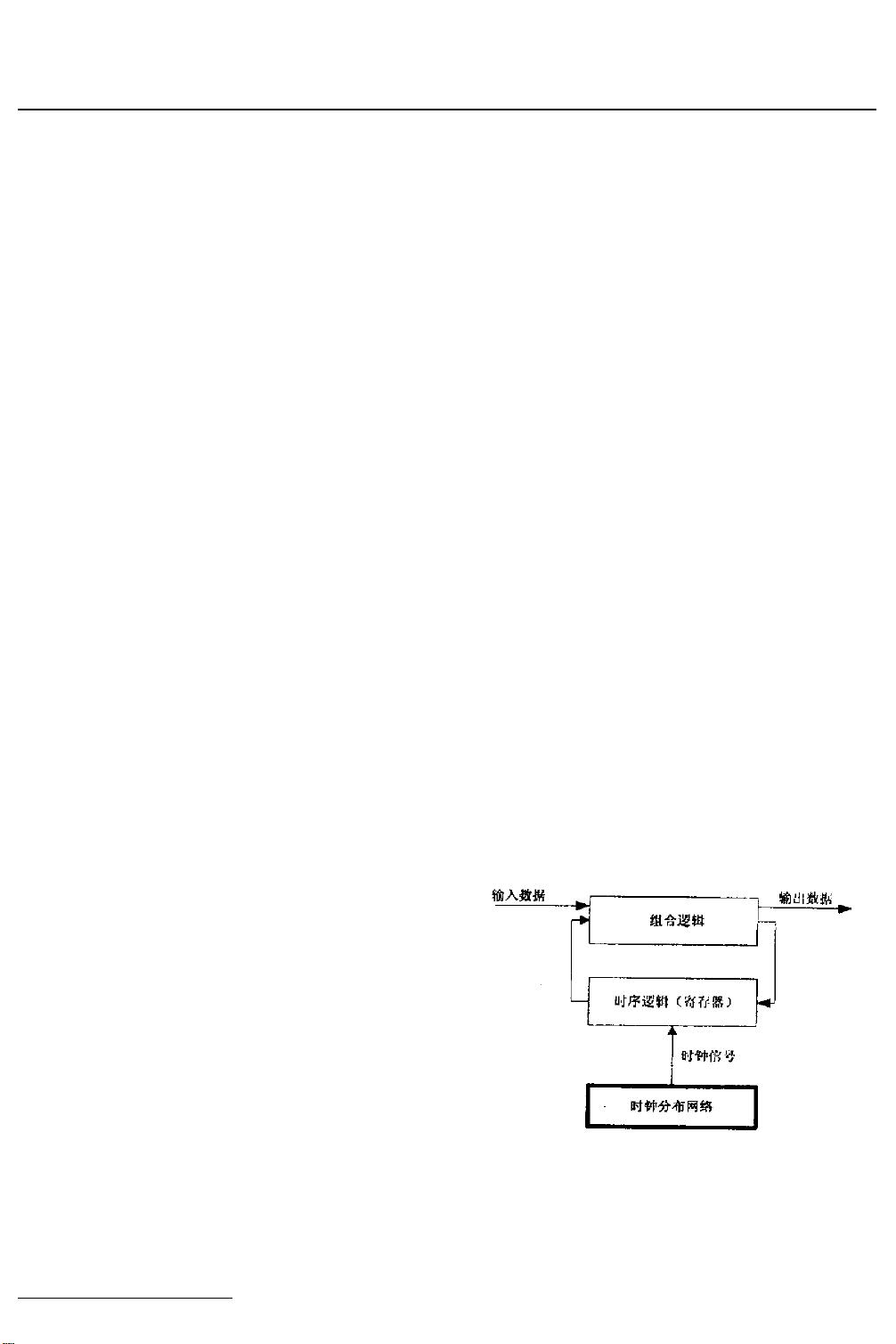

文章深入探讨了如何通过调节时钟树内的CLOCKSKEW来提升电路性能。时钟树是一种分发时钟信号的网络,通过层次结构将时钟信号从时钟源均匀地分配到各个模块。通过精心设计时钟树,可以确保时钟偏移在整个电路中的分布更加均衡,从而提高整体性能。这可能包括选择合适的负载均衡策略,或者利用反馈机制实时调整时钟速度,以适应不同模块的需求。

此外,文中还提到了针对时钟偏移问题的几种方法,例如时钟校准(Clock Calibration)、时钟缓冲器(Clock Buffer)的使用,以及高级的自适应逻辑设计,这些都可以帮助电路在非零时钟偏移条件下保持稳定且高效运行。通过优化时钟偏移管理,设计者能够在保证系统可靠性的前提下,提升电路的时钟频率,从而达到提高系统性能的目的。

该文对同步电路设计中的CLOCKSKEW分析具有实用价值,对于理解并解决时钟偏移带来的挑战,以及优化同步电路设计以适应高频率、高可靠性的需求具有重要意义。这对于从事FPGA和ASIC设计的工程师来说,提供了宝贵的参考和指导。通过学习和应用这些技术,设计师可以在保证电路性能的同时,避免因时钟偏移引发的问题,提升整个系统的效能。

2010-04-20 上传

Coffee-Or-Tea

- 粉丝: 6

- 资源: 2

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍