VHDL设计的定时器原理与实现

版权申诉

定时器VHDL设计

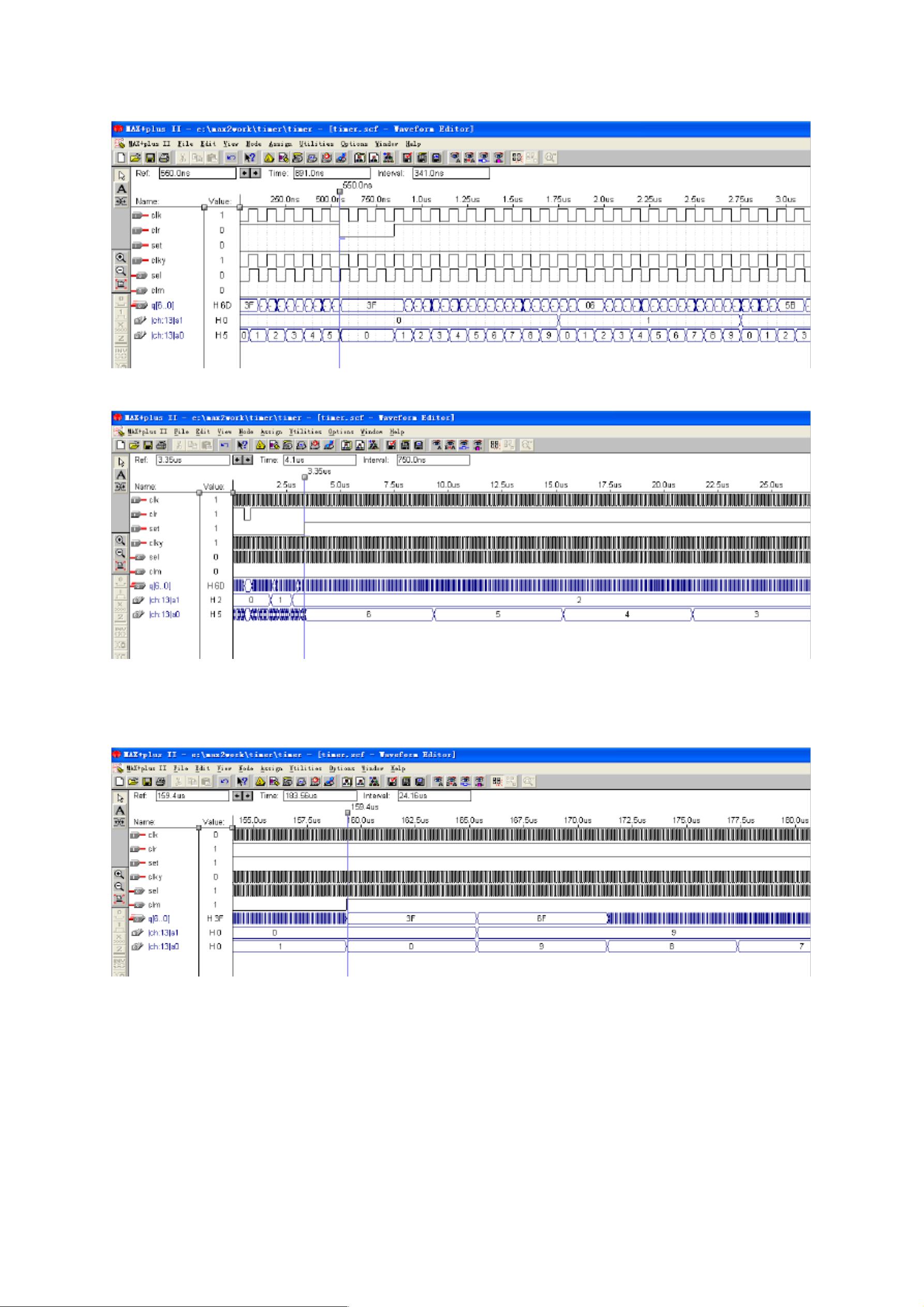

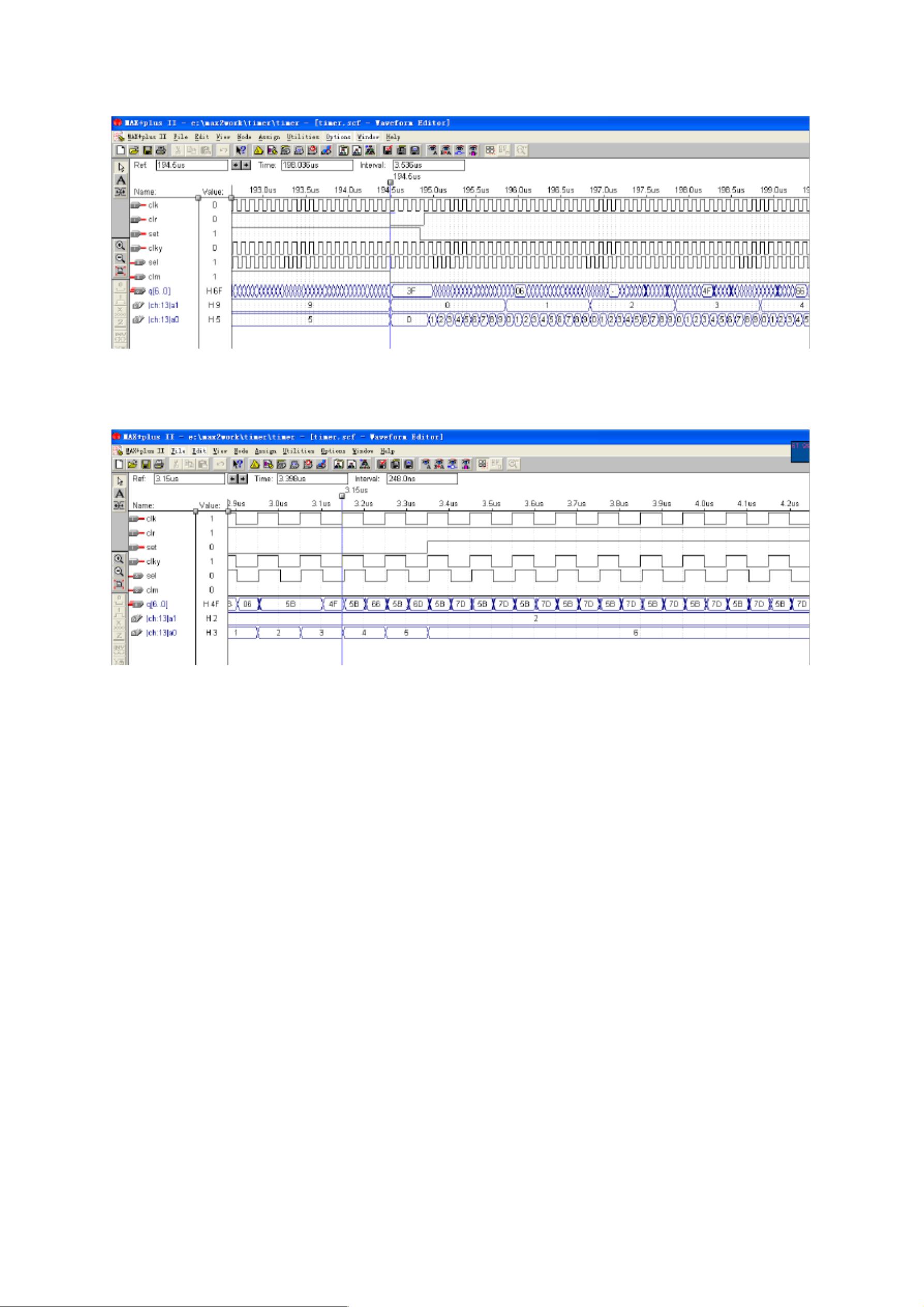

定时器是数字系统中的重要组成部分,用于实现特定时间间隔的延迟或计数功能。在VHDL(Very High-Speed Integrated Circuit Hardware Description Language)中,定时器的设计涉及到逻辑门电路的描述和行为建模。本设计中,我们将探讨一个基于VHDL的定时器,其主要功能包括整体清零、定时至最大99分钟,以及通过不同的计数模式进行递增和递减。

1. 实验任务与设计要求:

- 整体清零:通过clr输入信号,可以将定时器的计数值复位为零。

- 定时范围:最高可达99分钟,以秒为单位递增,以分递减至零。

- 输出信号:clky提供用于扫描和显示的信号,频率大于50Hz;set信号用于启动定时,低电平时开始递增,高电平时开始递减;alm输出高电平时,表示定时结束,可用于触发其他电路或报警。

- 显示:时间变化通过数码管显示,采用十进制数表示。

2. 模块与功能:

- 核心模块AAA:此模块负责实现定时器的逻辑功能,包括计数和状态控制。输入信号有clk(秒信号,1Hz,仿真中为10MHz),clr(复位信号),set(启动/停止信号),输出alm(定时结束信号)和两个4位二进制数q1和q0(用于表示分钟和秒)。

- VHDL代码段:

```vhdl

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY aaa IS

PORT (

clk, clr, set: IN std_logic;

alm: OUT std_logic;

q1, q0: OUT std_logic_vector(3 DOWNTO 0)

);

END aaa;

ARCHITECTURE aaa_arc OF aaa IS

VARIABLE cnt1, cnt0: std_logic_vector(3 DOWNTO 0);

VARIABLE cnt: INTEGER RANGE 0 TO 59;

BEGIN

-- 进行过程处理

PROCESS (clk, clr)

BEGIN

IF clr = '0' THEN

-- 整体复位

alm <= '0';

cnt := 0;

cnt1 := "0000";

cnt0 := "0000";

ELSIF clk'EVENT AND clk = '1' THEN

-- 设计数初值

IF set = '0' THEN

cnt := 0;

-- 递增计数逻辑

...

ELSE

-- 递减计数逻辑

...

END IF;

END IF;

END PROCESS;

END aaa_arc;

```

- 代码中,process语句用于描述时序逻辑,当clr为低电平时,定时器被复位;当clk上升沿到来且set为低电平时,开始递增计数。在仿真中,clk的频率设为10MHz,这允许每秒计数10,000,000次,以实现1Hz的秒信号。

3. 计数逻辑:

- 在计数过程中,cnt0和cnt1分别用于存储秒和分钟的值,它们都是4位二进制数。在递增模式下,当秒达到9(二进制的"1001")时,会重置并递增分钟计数;同样,当分钟达到9(二进制的"1001")时,也会进行相应的重置和递增。在递减模式下,当分钟不为零时,分钟计数递减,当分钟归零后,秒计数递减。

4. 时钟信号:

- clk是主时钟,用于驱动计数器;clky是一个扫描信号,频率大于50Hz,用于驱动数码管显示;set信号在低电平时启动递增计数,在高电平时启动递减计数。

5. 输出信号:

- alm信号在定时结束时变为高电平,用于指示定时已到达设定值。

- q1和q0是输出的分钟和秒的二进制表示,它们将根据cnt1和cnt0的值动态更新。

这个VHDL设计的定时器通过精确的时序逻辑实现了定时、复位、启动/停止和显示等功能,适用于数字系统中的各种定时需求。通过VHDL的建模和仿真,我们可以对这个定时器进行全面的功能验证和性能测试。

143 浏览量

2021-10-12 上传

2023-06-01 上传

130 浏览量

2021-12-10 上传

183 浏览量

hhappy0123456789

- 粉丝: 77

- 资源: 5万+