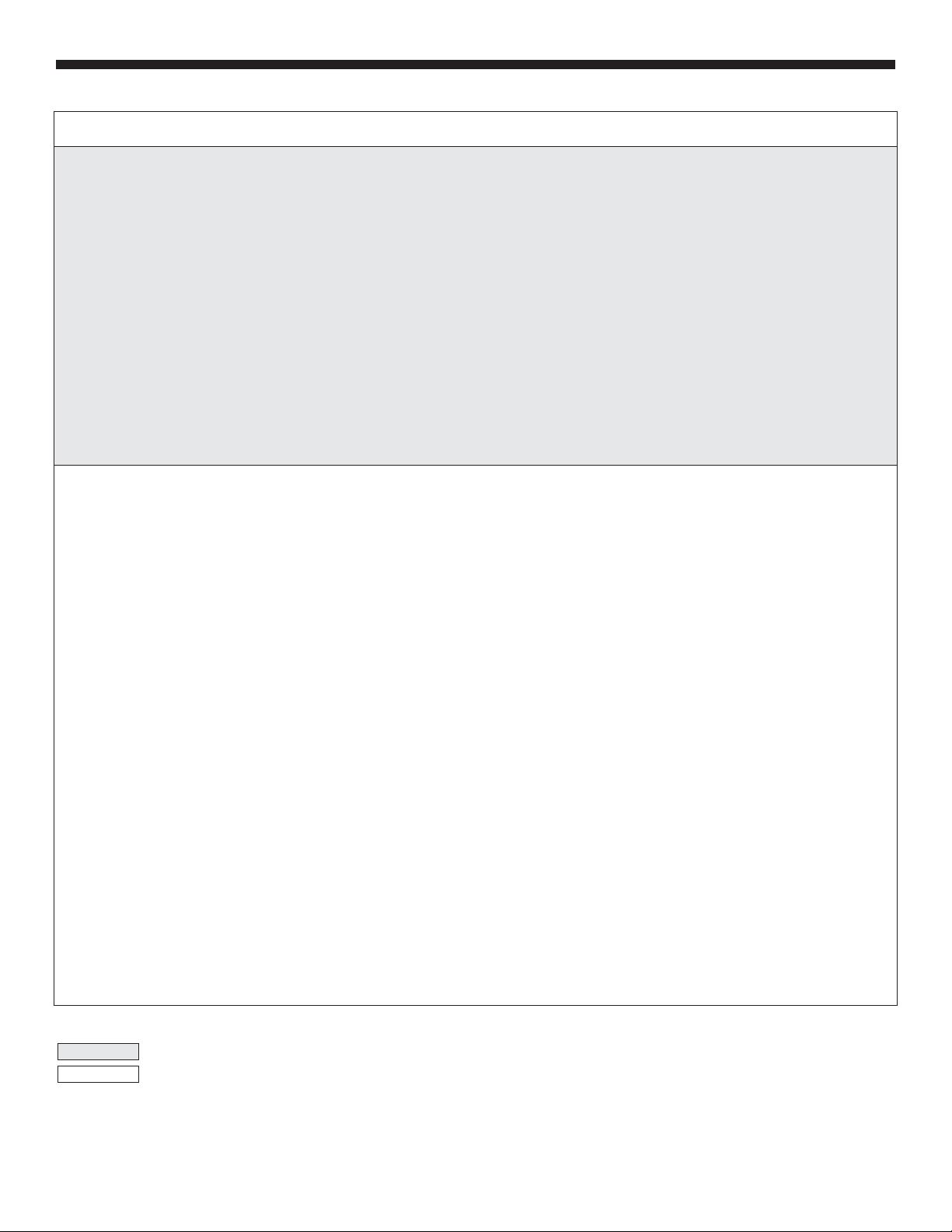

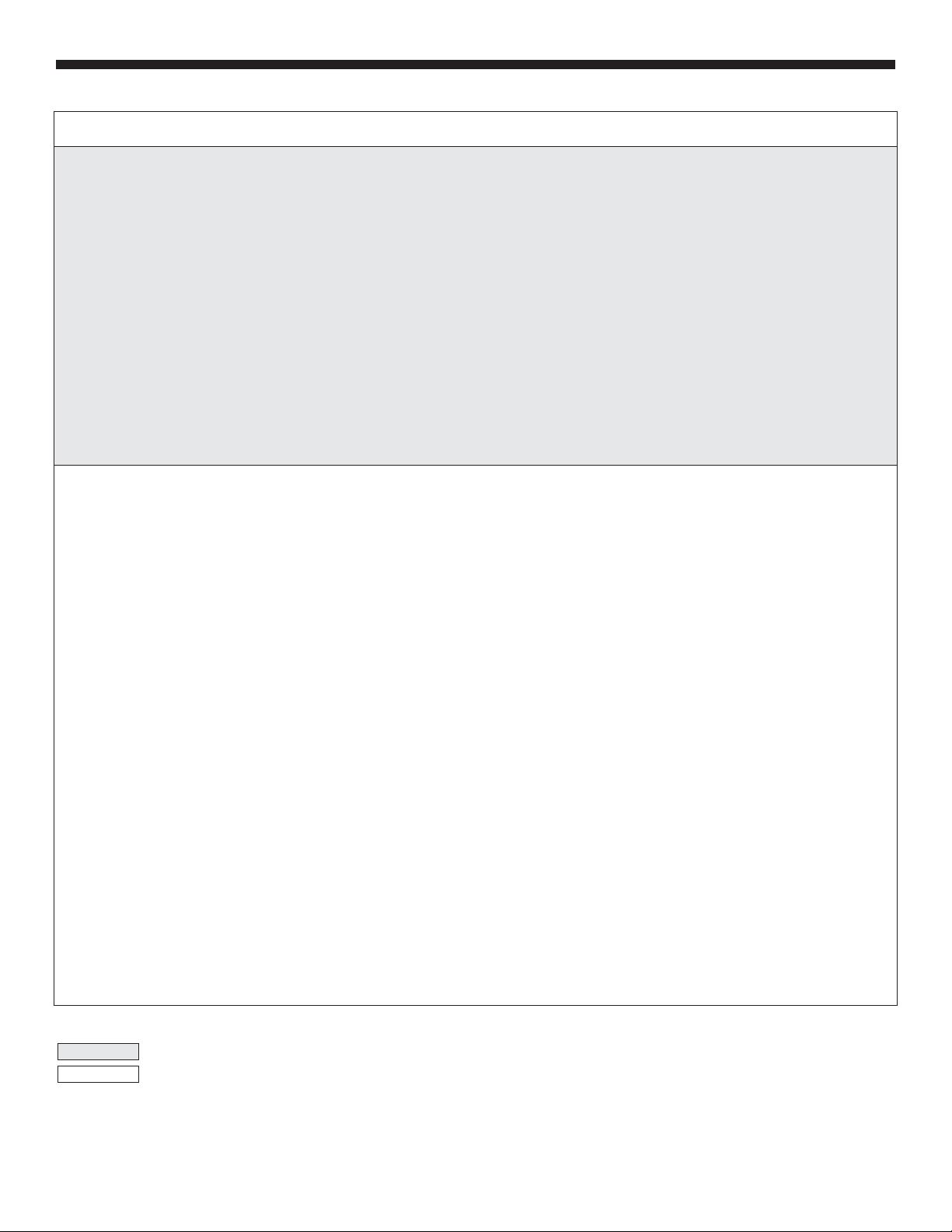

HI-3210 REGISTER MAP

ADDRESS R/W REGISTER MNEMONIC DESCRIPTION

0x8000 R* ARINC 429 Rx PENDING INTERRUPT APIR Defines channel(s) with pending Interrupt

0x8001 R ARINC 429 Rx INTERRUPT ADDRESS 0 AIAR0 ARINC 429 Interrupt Vector channel 0

0x8002 R ARINC 429 Rx INTERRUPT ADDRESS 1 AIAR1 ARINC 429 Interrupt Vector channel 1

0x8003 R ARINC 429 Rx INTERRUPT ADDRESS 2 AIAR2 ARINC 429 Interrupt Vector channel 2

0x8004 R ARINC 429 Rx INTERRUPT ADDRESS 3 AIAR3 ARINC 429 Interrupt Vector channel 3

0x8005 R ARINC 429 Rx INTERRUPT ADDRESS 4 AIAR4 ARINC 429 Interrupt Vector channel 4

0x8006 R ARINC 429 Rx INTERRUPT ADDRESS 5 AIAR5 ARINC 429 Interrupt Vector channel 5

0x8007 R ARINC 429 Rx INTERRUPT ADDRESS 6 AIAR6 ARINC 429 Interrupt Vector channel 6

0x8008 R ARINC 429 Rx INTERRUPT ADDRESS 7 AIAR7 ARINC 429 Interrupt Vector channel 7

0x8009 - RESERVED

0x800A R* PENDING INTERRUPT REGISTER PIR Indicates Interrupt type

0x800B R RESERVED

0x800C R MUXED FIFO FLAGS AMFF ARINC 429 Multiplexed FIFO flags

0x800D R ARINC 429 TX READY BITS ATRB ARINC 429 Transmitter Ready flags

0x800E R MASTER STATUS REGISTER MSR Indicates HI-3200 current status

0x800F R/W MASTER CONTROL REGISTER MCR HI-3200 global configuration

0x8010 R/W ARINC 429 RX CONTROL REGISTER 0 ARXC0 Configures ARINC 429 receive channel 0

0x8011 R/W ARINC 429 RX CONTROL REGISTER 1 ARXC1 Configures ARINC 429 receive channel 1

0x8012 R/W ARINC 429 RX CONTROL REGISTER 2 ARXC2 Configures ARINC 429 receive channel 2

0x8013 R/W ARINC 429 RX CONTROL REGISTER 3 ARXC3 Configures ARINC 429 receive channel 3

0x8014 R/W ARINC 429 RX CONTROL REGISTER 4 ARXC4 Configures ARINC 429 receive channel 4

0x8015 R/W ARINC 429 RX CONTROL REGISTER 5 ARXC5 Configures ARINC 429 receive channel 5

0x8016 R/W ARINC 429 RX CONTROL REGISTER 6 ARXC6 Configures ARINC 429 receive channel 6

0x8017 R/W ARINC 429 RX CONTROL REGISTER 7 ARXC7 Configures ARINC 429 receive channel 7

0x8018 R/W ARINC 429 TX CONTROL REGISTER 0 ATXC0 Configures ARINC 429 transmit channel 0

0x8019 R/W ARINC 429 TX CONTROL REGISTER 1 ATXC1 Configures ARINC 429 transmit channel 1

0x801A R/W ARINC 429 TX CONTROL REGISTER 2 ATXC2 Configures ARINC 429 transmit channel 2

0x801B R/W ARINC 429 TX CONTROL REGISTER 3 ATXC3 Configures ARINC 429 transmit channel 3

0x801C R/W ARINC 429 TX REPETITION RATE 0 ATXRR0 Sets sequence repeat time for ARINC TX0

0x801D R/W ARINC 429 TX REPETITION RATE 1 ATXRR1 Sets sequence repeat time for ARINC TX1

0x801E R/W ARINC 429 TX REPETITION RATE 2 ATXRR2 Sets sequence repeat time for ARINC TX2

0x801F R/W ARINC 429 TX REPETITION RATE 3 ATXRR3 Sets sequence repeat time for ARINC TX3

0x8020 R/W ARINC 429 Rx INTERRUPT MASK AIMR Enables Interrupts on AINT pin

0x8021 R/W ARINC 429 Rx FIFO THRESHOLD VALUE AFTV Sets flag value for ARINC 429 Receive FIFO

0x8022 R/W ARINC 429 LOOPBACK ALOOP Sets loop-back self-test mode

0x8029 R ARINC 429 Rx FIFO FULL FLAG AFFF Indicates which FIFOs are full

0x802A R ARINC 429 Rx FIFO THRESHOLD FLAG AFTF Indicates which FIFOs hold > (thresh) messages

0x802B R ARINC 429 Rx FIFO NOT EMPTY FLAG FFNE Indicates which receive FIFOs hold data

0x802C R ARINC 429 TX SEQUENCE POINTER 0 ATXSP0 Current address of ARINC transmit sequence 0

0x802D R ARINC 429 TX SEQUENCE POINTER 1 ATXSP1 Current address of ARINC transmit sequence 1

0x802E R ARINC 429 TX SEQUENCE POINTER 2 ATXSP2 Current address of ARINC transmit sequence 2

0x802F R ARINC 429 TX SEQUENCE POINTER 3 ATXSP3 Current address of ARINC transmit sequence 3

0x8034 R/W PENDING INTERRUPT ENABLE REGISTER IMR Enables Interrupts on INT pin

0x8035 R/W ARINC 429 TX READY INT ENABLE ATRIE Enables ARINC 429 TX Ready Interrupts

Fast Access Registers * Register is cleared when read (auto clear)

Memory mapped register access only

HOLT INTEGRATED CIRCUITS

8

HI-3210