大唐电信:FPGA-CPLD时序设计实战与优化策略

需积分: 9 30 浏览量

更新于2024-07-23

1

收藏 951KB PDF 举报

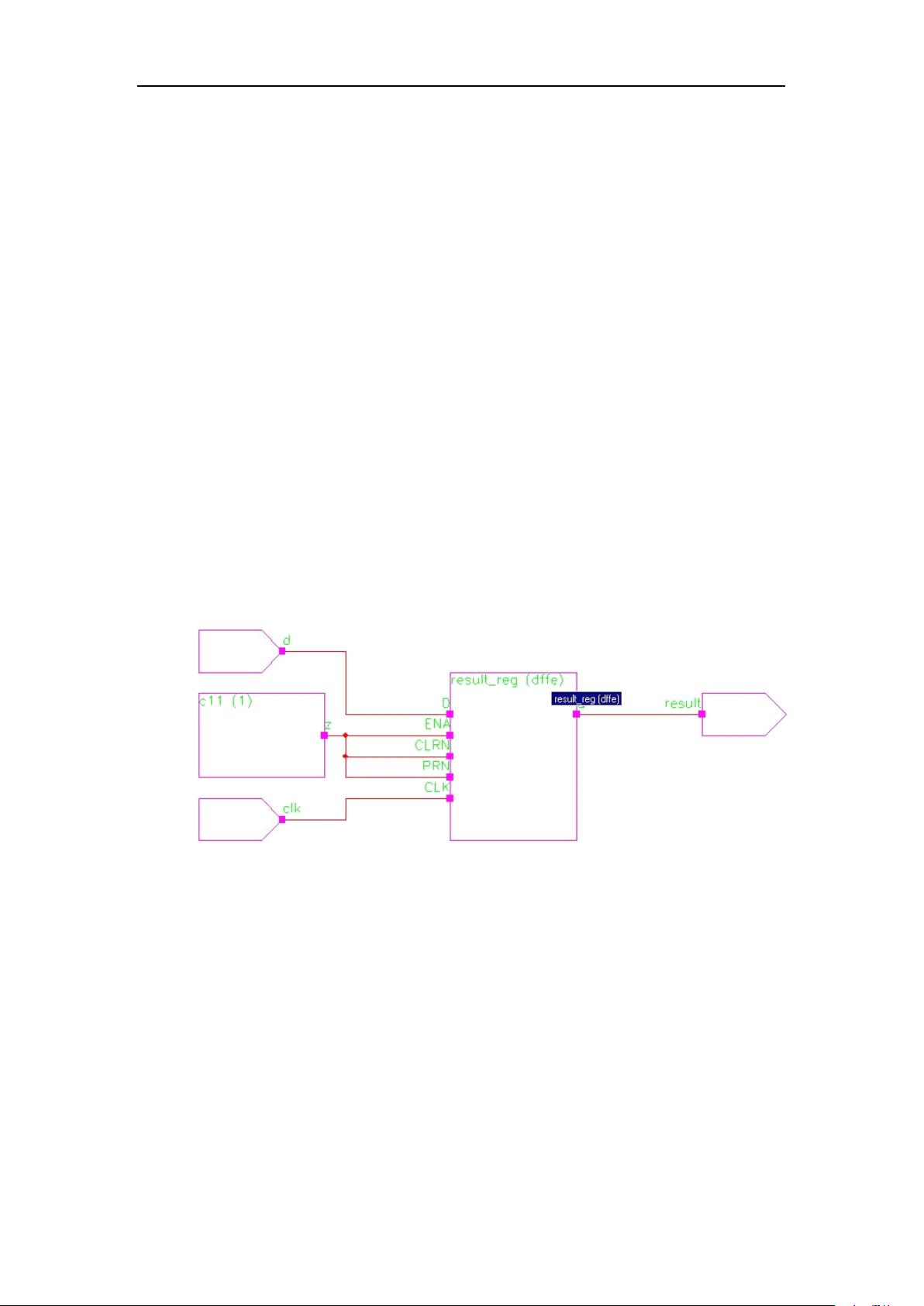

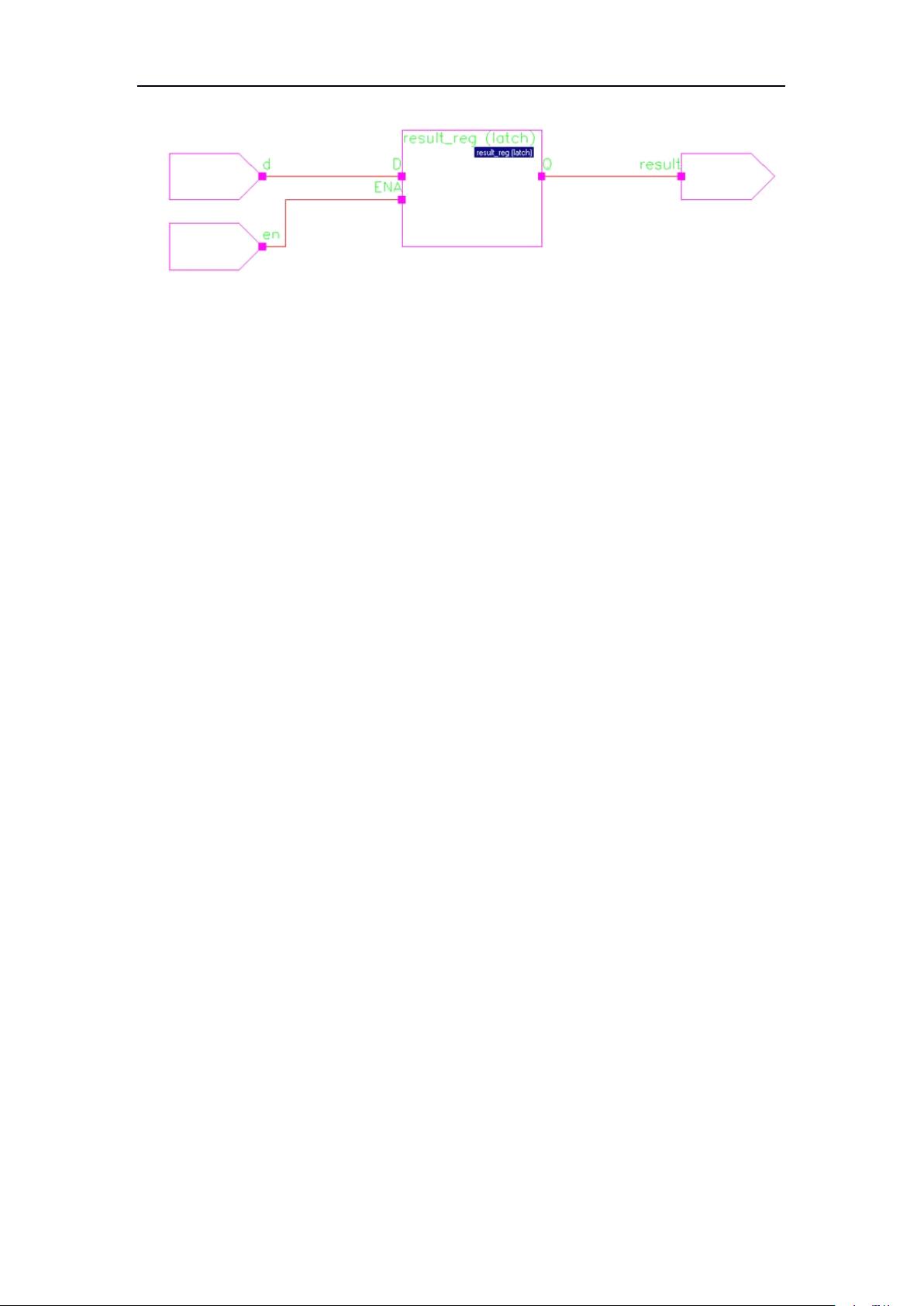

在"大唐电信FPGA-CPLD数字电路设计经验分享"这篇文章中,作者详细探讨了在数字电路设计特别是FPGA/CPLD领域的重要实践经验。首先,时序设计被强调为数字电路性能的关键指标,随着高层次设计方法的发展,对时序控制的抽象度提升,这对设计者提出了更高的挑战。然而,通过理解RTL电路的时序模型并采用合适的策略,如在设计过程中确保建立时间和保持时间的满足,可以显著提高电路的后仿真成功率,使得系统能够运行在较高的工作频率。

建立时间和保持时间是数字电路设计的基础概念,分别指数据在触发器时钟上升沿前后的稳定期。如果这两个参数不足,数据可能无法正确存储或传输。在考虑这些参数时,设计师需注意时钟树的偏斜,建立时间受时钟周期影响,而保持时间则独立于时钟周期。在高速系统中,当系统无法在高频率下工作时,可以通过降低时钟频率来解决问题,但保持时间的问题往往需要通过优化设计来解决,否则即使调整频率也无法满足要求,这将严重影响设计效率。

文章特别关注FPGA技术的应用,因为其灵活性使得时钟树偏斜在可编程器件中可以忽略,但保持时间仍然是关键。FPGA/CPLD的设计实践中,合理设置时序约束,包括计算和验证输入的建立和保持时间,是提高设计质量和效率的关键步骤。

通过实例分享,作者证明了如何通过精心设计,不仅提升了电路的性能,还提高了设计的成功率,这对于从事FPGA-CPLD数字电路设计的工程师来说,是一份实用且富有价值的经验分享。掌握这些基本原则和技术,将有助于在实际项目中实现高效、稳定的数字电路设计。

213 浏览量

191 浏览量

120 浏览量

197 浏览量

340 浏览量

192 浏览量

132 浏览量

180 浏览量

268 浏览量

haoranzhao

- 粉丝: 0

- 资源: 1

最新资源

- GEN32“创世纪32“监控组态软件.rar

- valle-input:很棒的valle输入元素-使用Polymer 3x的Web组件

- Simple Picture Puzzle Game in JavaScript Free Source Code.zip

- ssm高考志愿填报系统设计毕业设计程序

- MyApplication:组件化、

- wc-core:Mofon Design的Web组件核心

- odrViewer.zip_odrViewer_opendrive_opendrive viewer_opendrive可视化_

- Simple Table Tennis Game using JavaScript

- 同步安装文件2.rar

- GalaxyFighters-开源

- STM32+W5500 Modbus-TCP协议功能实现

- Excel做为数据库登录的三层实现_dotnet整站程序.rar

- konsave:Konsave允许使用保存您的KDE Plasma自定义设置并非常轻松地还原它们!

- make-element:创建没有样板的自定义元素

- MachineLearning

- Simple Platformer Game using JavaScript