失效感知ECC提升STT-MRAM性能:成品率、面积与能量优化

190 浏览量

更新于2024-06-18

收藏 792KB PDF 举报

"本文主要探讨了STT-MRAM(自旋转移扭矩磁阻随机存取内存)技术在新兴计算系统中的应用,以及如何通过引入失效感知ECC(Error Correction Code)来优化其成品率、面积和能量效率。作者Zoha Pajouhi, Xuanyao Fong, Anand RAGHUNATHAN 和 Kaushik Roy来自普渡大学,他们在2016年的《ACM Journal on Emerging Technologies in Computing Systems》中发表了这一研究成果。"

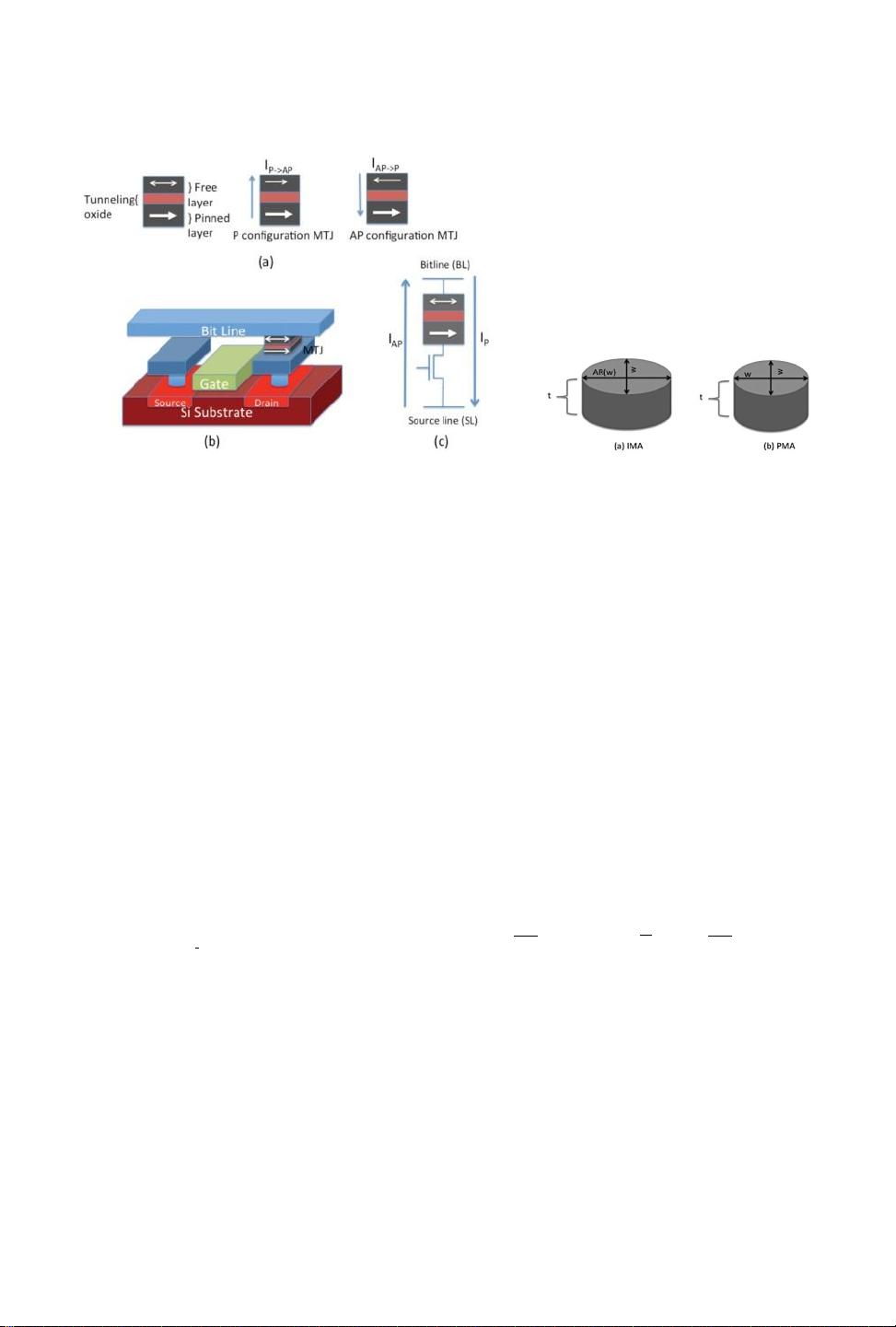

STT-MRAM作为一种先进的存储技术,拥有非挥发性(数据在断电后仍能保留)、高存储密度和几乎无泄漏电流的特性,使其成为未来嵌入式存储器的理想选择。然而,STT-MRAM面临的主要挑战是由于读写路径共享导致的可靠性问题,以及由数据保持和可写性需求之间的矛盾所引起的复杂性。这些矛盾与存储单元的能量势垒高度密切相关,而能量势垒高度又受制于存储单元的几何形状变化。

为解决STT-MRAM的可靠性问题,通常采用ECC技术来纠正错误。但是,对于STT-MRAM,由于需要在低写入功率下保证高良率,所以需要更为强大的ECC,这可能导致编码位数增加,从而降低存储器的容量。为了解决这一问题,文章提出了故障感知ECC(FaECC)策略。FaECC旨在隐藏永久性故障,同时保持原有的软错误纠正能力,而无需增加编码位数,从而避免了存储容量的减少。

作者通过建立一个跨层次的仿真框架,涵盖了器件、电路和阵列级别的分析,对STT-MRAM存储器阵列进行了深入研究。他们的研究结果显示,应用FaECC可以放宽对能量势垒高度的要求,从而降低写入能量。这不仅有利于提高写入效率,还能减小访问晶体管的尺寸,进一步缩小存储器阵列的面积。

本文的贡献在于提出了一种新的ECC策略,它在不牺牲存储性能的情况下,提高了STT-MRAM的可靠性和能效。这一成果对优化嵌入式存储器系统,特别是在低功耗和高性能需求的场景下,具有重要的理论和实际意义。

关键词:STT-MRAM,新兴技术,自旋电子学,磁性技术,嵌入式存储器,故障感知ECC,能量效率,阵列设计,工艺变化,可靠性分析。

2021-02-21 上传

2021-01-12 上传

2021-07-13 上传

2020-10-15 上传

2021-04-14 上传

2022-12-01 上传

2022-12-01 上传

cpongm

- 粉丝: 5

- 资源: 2万+

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍