LPC1768_66_65_64_2 © NXP B.V. 2009. All rights reserved.

Objective data sheet Rev. 02 — 11 February 2009 14 of 72

NXP Semiconductors

LPC1768/66/65/64

32-bit ARM Cortex-M3 microcontroller

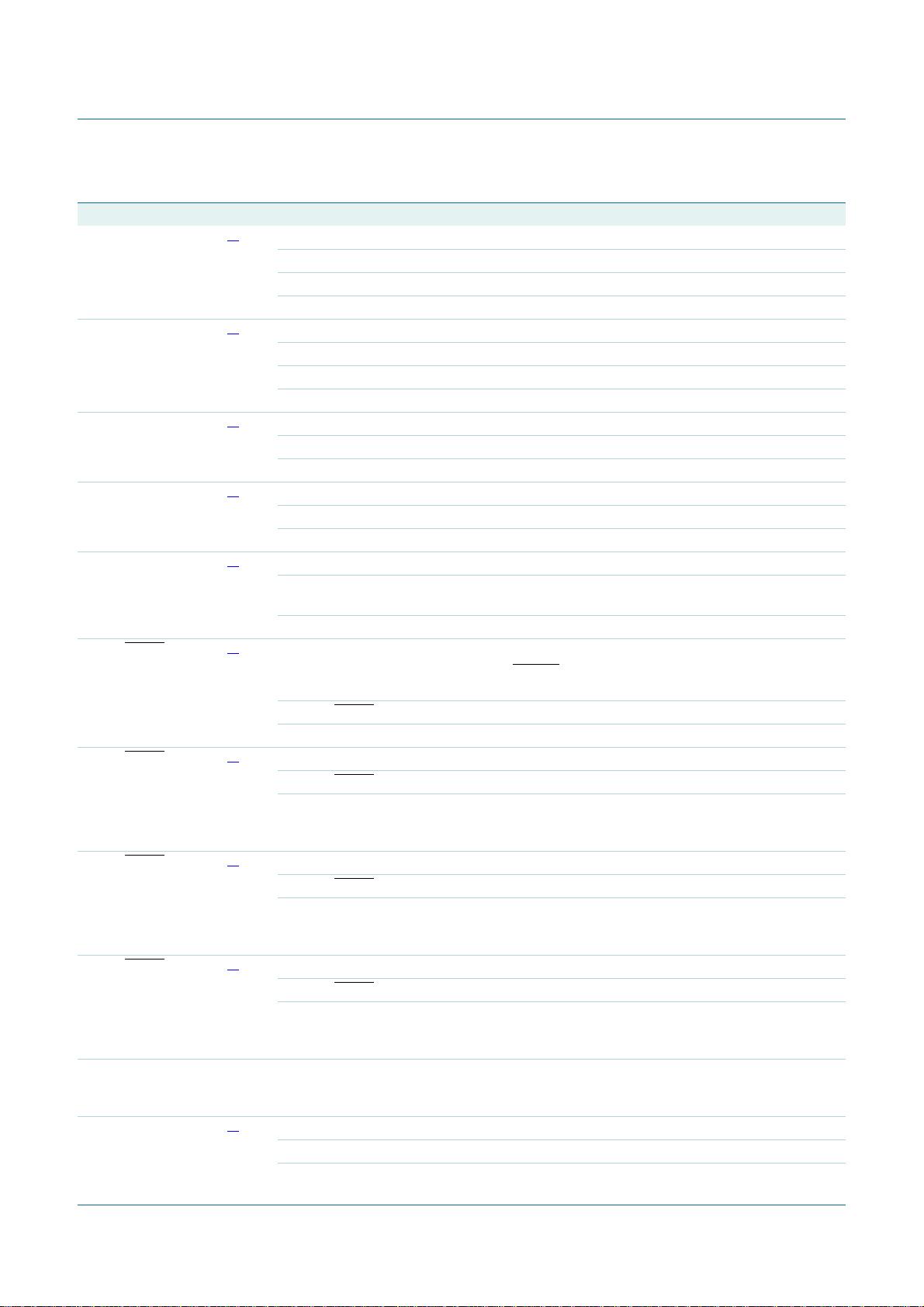

[1] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis.

[2] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input. When configured as a ADC input,

digital section of the pad is disabled.

[3] 5 V tolerant pad providing digital I/O with TTL levels and hysteresis and analog output function. When configured as the DAC output,

digital section of the pad is disabled.

[4] Open-drain 5 V tolerant digital I/O pad, compatible with I

2

C-bus 400 kHz specification. This pad requires an external pull-up to provide

output functionality. When power is switched off, this pin connected to the I

2

C-bus is floating and does not disturb the I

2

C lines.

Open-drain configuration applies to all functions on this pin.

[5] Pad provides digital I/O and USB functions. It is designed in accordance with the

USB specification, revision 2.0

(Full-speed and

Low-speed mode only).

[6] 5 V tolerant pad with 5 ns glitch filter providing digital I/O functions with TTL levels and hysteresis.

[7] 5 V tolerant pad with 20 ns glitch filter providing digital I/O function with TTL levels and hysteresis.

[8] Pad provides special analog functionality.

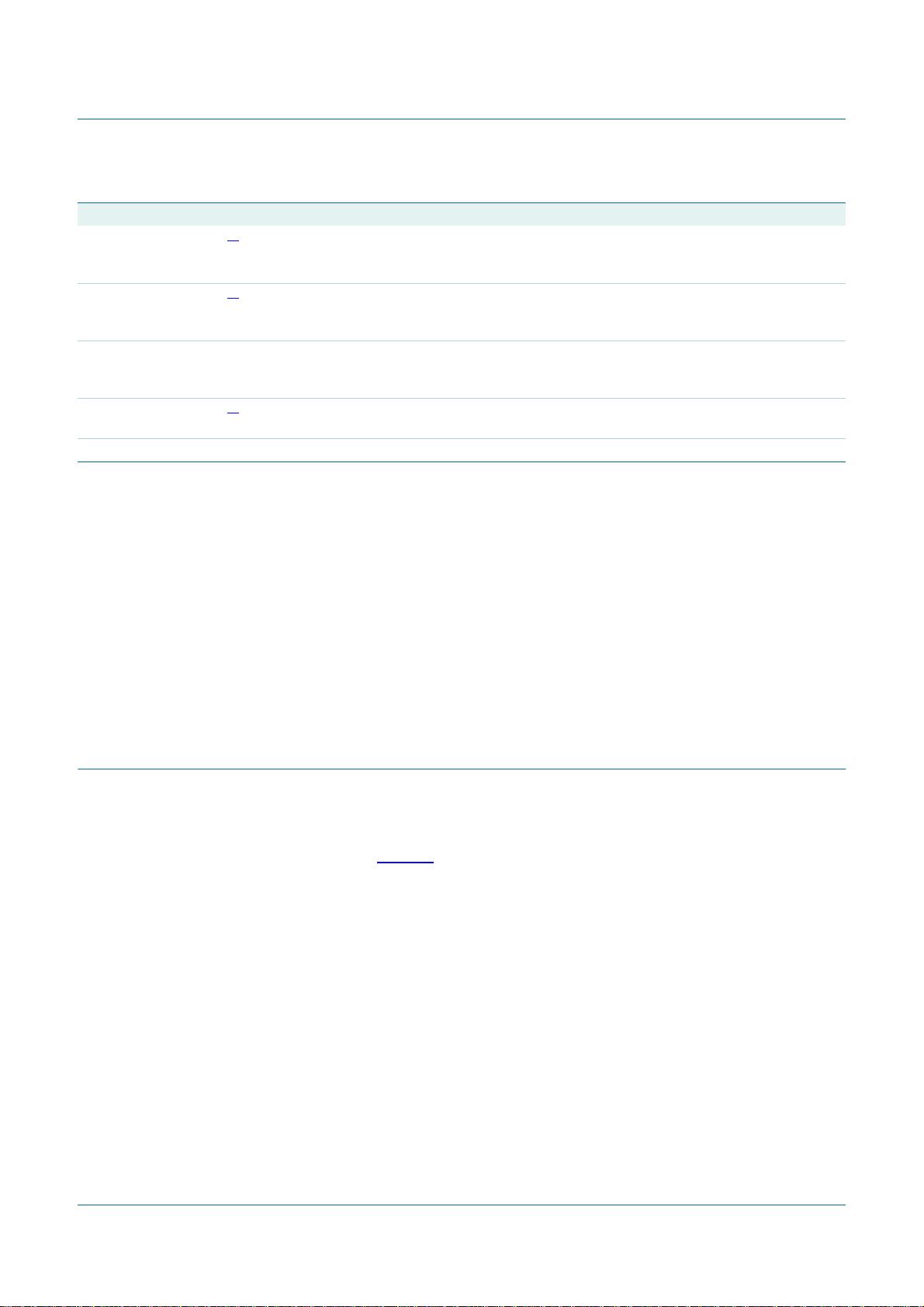

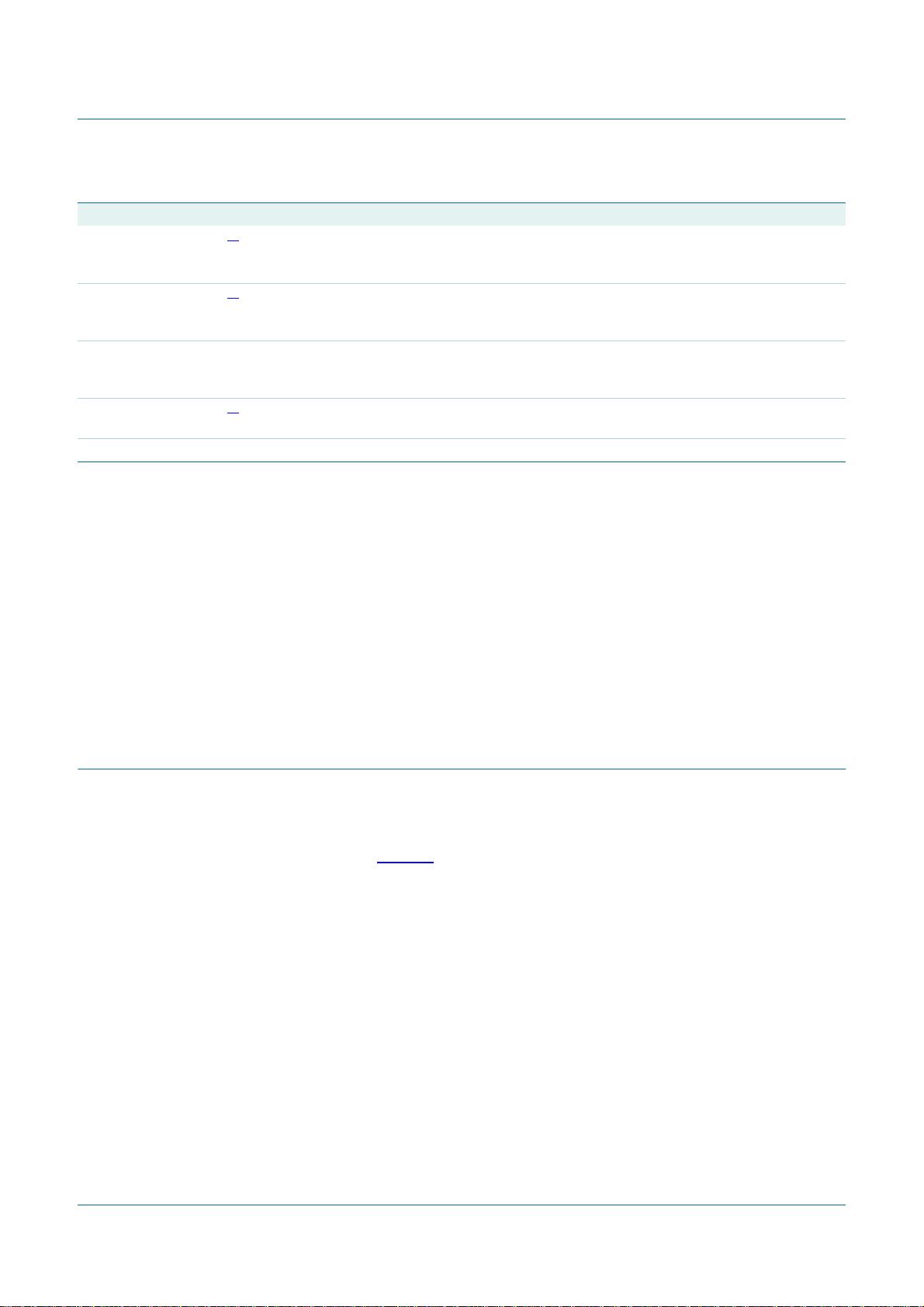

7. Functional description

7.1 Architectural overview

The ARM Cortex-M3 includes three AHB-Lite buses: the system bus, the I-code bus, and

the D-code bus (see Figure 1). The I-code and D-code core buses are faster than the

system bus and are used similarly to TCM interfaces: one bus dedicated for instruction

fetch (I-code) and one bus for data access (D-code). The use of two core buses allows for

simultaneous operations if concurrent operations target different devices.

The LPC1768/66/65/64 use a multi-layer AHB matrix to connect the ARM Cortex-M3

buses and other bus masters to peripherals in a flexible manner that optimizes

performance by allowing peripherals that are on different slaves ports of the matrix to be

accessed simultaneously by different bus masters.

7.2 ARM Cortex-M3 processor

The ARM Cortex-M3 is a general purpose, 32-bit microprocessor, which offers high

performance and very low power consumption. The ARM Cortex-M3 offers many new

features, including a Thumb-2 instruction set, low interrupt latency, hardware divide,

interruptable/continuable multiple load and store instructions, automatic state save and

restore for interrupts, tightly integrated interrupt controller with wakeup interrupt controller,

and multiple core buses capable of simultaneous accesses.

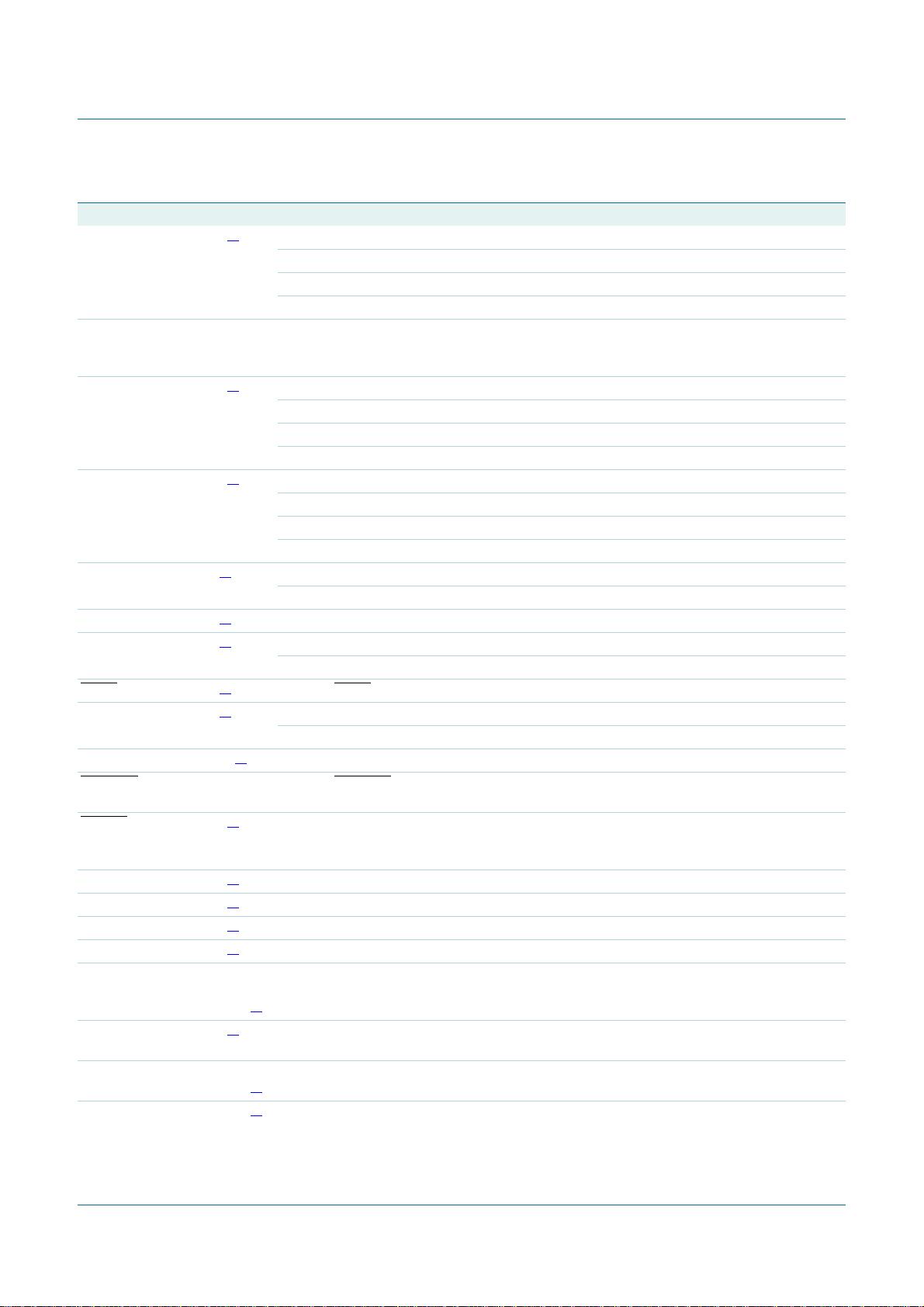

V

DDA

10

[8]

I analog 3.3 V pad supply voltage: This should be nominally the same voltage as

V

DD(3V3)

but should be isolated to minimize noise and error. This voltage is used to

power the ADC and DAC.

VREFP 12

[8]

I ADC positive reference voltage: This should be nominally the same voltage as

V

DDA

but should be isolated to minimize noise and error. Level on this pin is used

as a reference for ADC and DAC.

VREFN 15 I ADC negative reference voltage: This should be nominally the same voltage as

V

SS

but should be isolated to minimize noise and error. Level on this pin is used as

a reference for ADC and DAC.

VBAT 19

[8]

I RTC pin power supply: 3.3 V on this pin supplies the power to the RTC

peripheral.

n.c. 13 - not connected

Table 3. Pin description

…continued

Symbol Pin Type Description

元器件交易网www.cecb2b.com