"数字后端流程简介及工具应用指南"

需积分: 5 78 浏览量

更新于2024-01-09

1

收藏 2.52MB PDF 举报

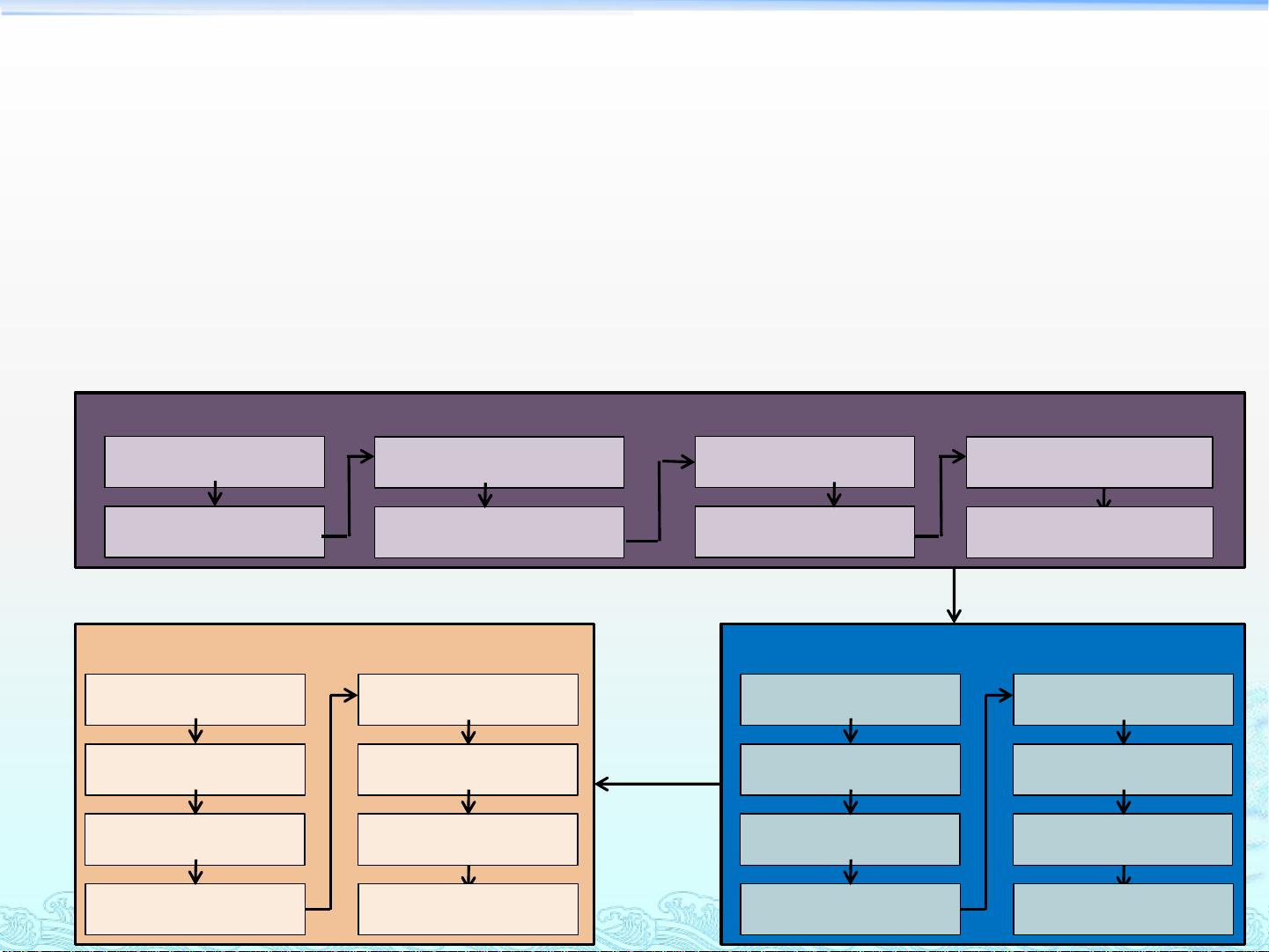

数字后端流程是指将前端设计的电路转化为可制造、可验证的物理布局的过程。下面将对数字后端流程进行详细介绍。

数字后端流程的第一步是数据准备,其中包括设计准备和数据准备。设计准备阶段主要工作包括对设计需求的分析和定义、设计约束的制定以及功能和性能的验证等。数据准备阶段则包括对设计所需的相关数据进行整理和准备,如设计文件、资源文件和工具链等。

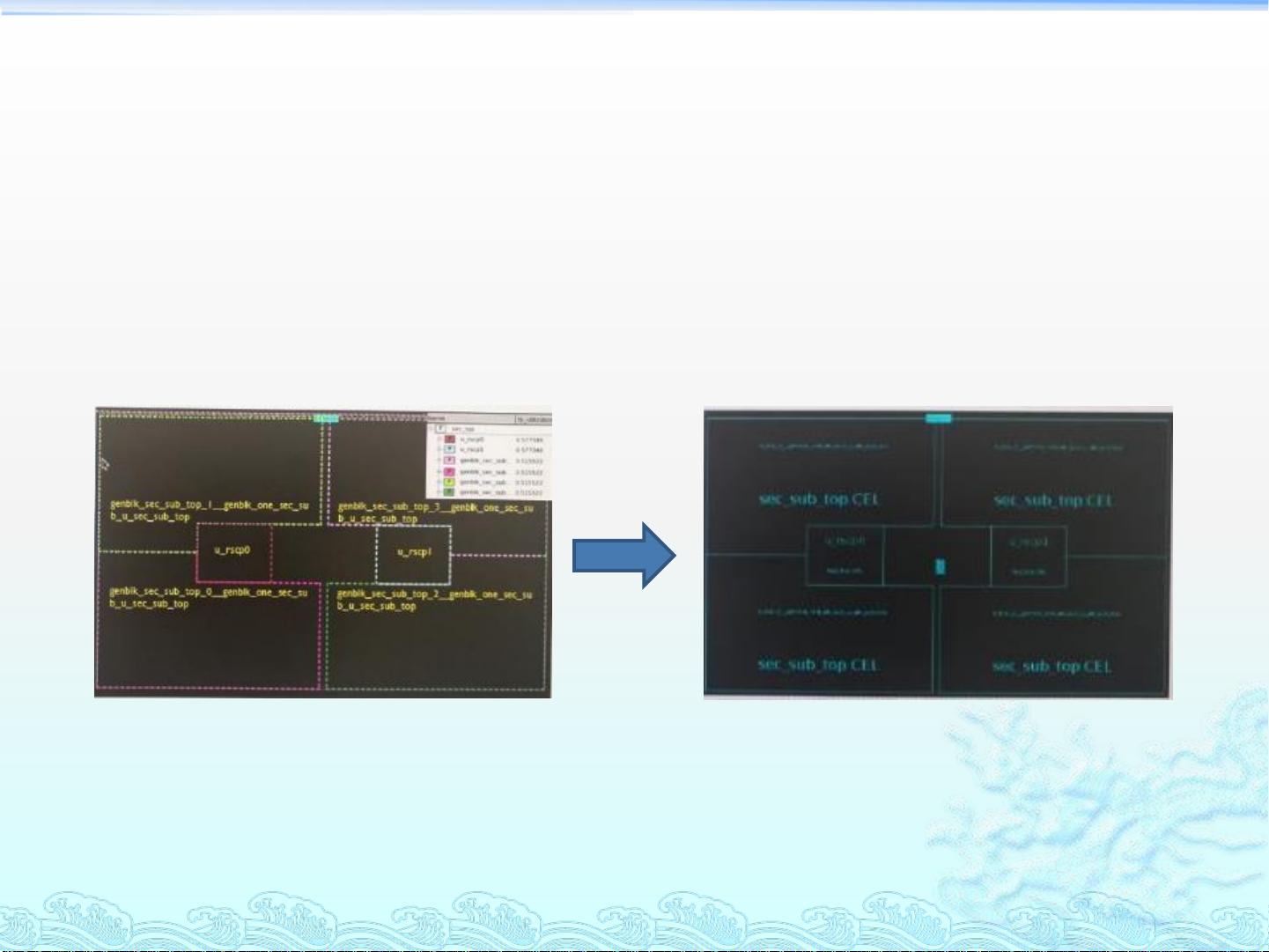

接下来是平面布置图的制作。平面布置图是指对电路中各个模块的相对位置进行规划和布置,以满足电路性能和芯片面积的要求。这一步需要考虑电路的空间布局、功耗和信号传输等方面的需求,以及避免电路中出现较高的信号干扰和功耗热点等问题。

在平面布置图制作完成后,接下来是进行时序分析和静态时序分析。时序分析是通过建立时序模型和约束来检查电路的时序特性是否满足设计要求。静态时序分析则是通过对电路中的路径进行优化和修复,以确保信号在电路中传输的时间窗口内。

完成时序分析后,接下来是针对物理验证的处理。物理验证是指对电路的物理结构进行检查,以确保电路的正确性和可制造性。包括对电路布局进行规范和合理性的检查,如电路的连线规则、组件间的间距等。同时还会对电路中的功耗、电压降等进行分析和优化,以确保电路的稳定性和可靠性。

在物理验证完成后,还需要对电路进行Gds merge处理。Gds merge是指将电路中的各个模块进行合并,以减少电路面积并提高芯片的集成度。这一步还可能包括对电路中的连线进行优化和修复,以提高电路的性能和可靠性。

最后是添加引线垫和提取RC文件。添加引线垫是为了将电路连接到芯片外部,以实现与其他电路或系统的连接。而提取RC文件则是为了获得电路中各个节点的电阻和电容等参数,并用于后续的电路仿真和分析。

综上所述,数字后端流程是将前端设计的电路转化为可制造、可验证的物理布局的过程。它涵盖了数据准备、平面布置图制作、时序分析、物理验证、Gds merge处理、引线垫添加和RC文件提取等多个环节。这些环节相互衔接,共同为电路设计的成功实现和生产提供了保障。

664 浏览量

546 浏览量

2024-02-29 上传

584 浏览量

滕杰

- 粉丝: 8

最新资源

- Actionscript3.0动画基础教程:从概念到实践

- 有限样本下的统计学习与核方法:支持向量机简介

- 中国联通Vasp接口技术详解:ParlayX与第三方协作指南

- Oracle9i查询优化深度解析:提升性能的关键技术

- 中国联通SP接口规范v1.3详解:业务订购与取消

- Nutch学习教程:从入门到精通

- C#实用教程:掌握正则表达式

- CMM1.1:提升软件开发能力的关键模型

- MyEclipse快捷键大全:提升编程效率的秘籍

- 使用load()或reload()加载数据库连接脚本

- CSS初学者指南:掌握基本知识与技巧

- C++设计新思维:泛型编程与设计模式应用

- 提升网站速度与美感:高手实战 Yahoo! 绩效优化策略

- PCIExpress深度解析:下一代高速I/O接口

- SQL Server 2005 Reporting Services 中文教程:创建报表服务器项目

- R语言数据导入导出指南