Published SFF-8436 Rev 4.2

QSFP+ 10 Gbs 4X Pluggable Transceiver Page 18

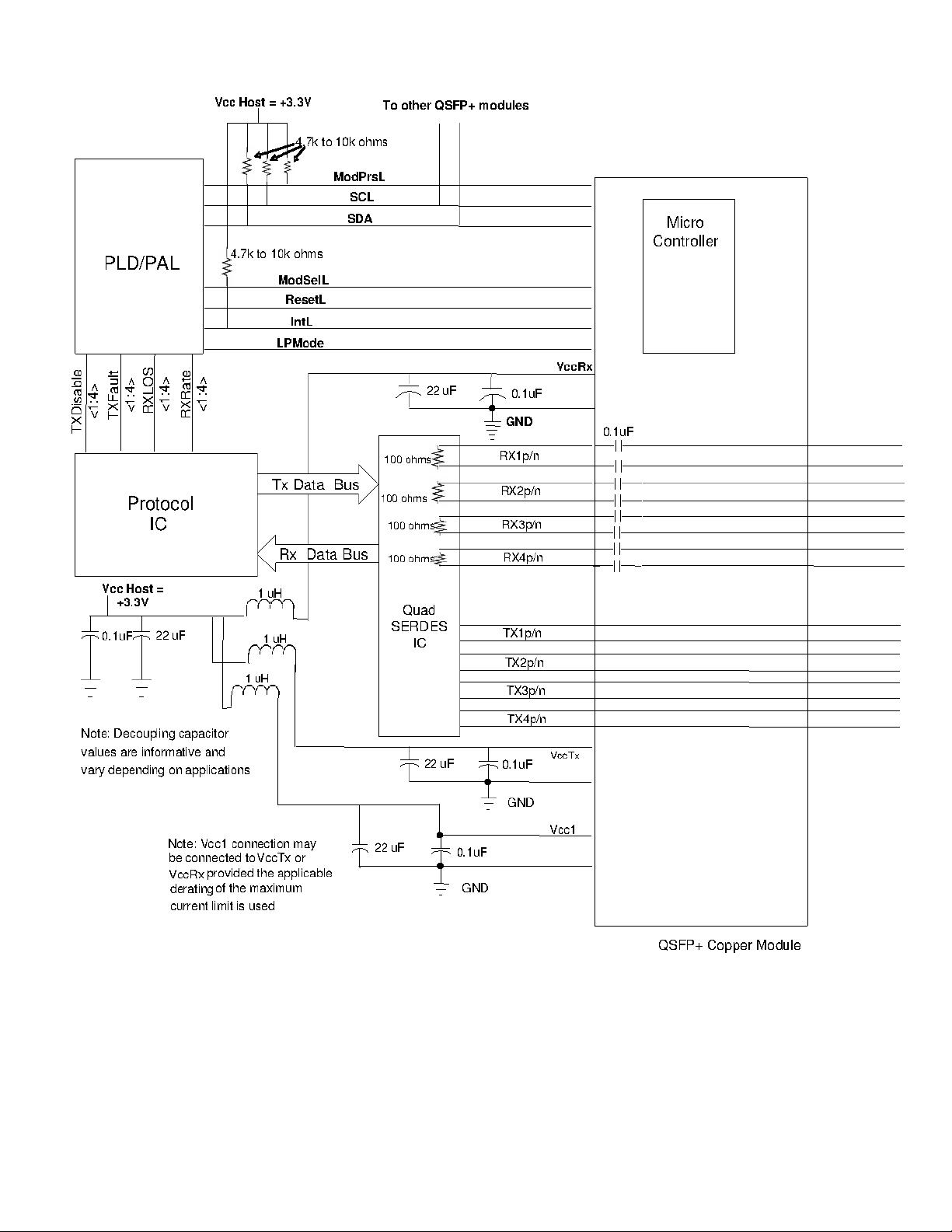

ModPrsL

IntL

4.1.1.1 ModSelL

The ModSelL is an input pin. When held low by the host, the module responds to 2-wire

serial communication commands. The ModSelL allows the use of multiple QSFP+ modules on a

single 2-wire interface bus. When the ModSelL is “High”, the module shall not respond to

or acknowledge any 2-wire interface communication from the host. ModSelL signal input

node must be biased to the “High” state in the module.

In order to avoid conflicts, the host system shall not attempt 2-wire interface

communications within the ModSelL de-assert time after any QSFP+ modules are deselected.

Similarly, the host must wait at least for the period of the ModSelL assert time before

communicating with the newly selected module. The assertion and de-asserting periods of

different modules may overlap as long as the above timing requirements are met.

4.1.1.2 ResetL

The ResetL pin must be pulled to Vcc in the QSFP+ module. A low level on the ResetL pin

for longer than the minimum pulse length (t_Reset_init) initiates a complete module

reset, returning all user module settings to their default state. Module Reset Assert

Time (t_init) starts on the rising edge after the low level on the ResetL pin is

released. During the execution of a reset (t_init) the host shall disregard all status

bits until the module indicates a completion of the reset interrupt. The module indicates

this by asserting “low” an IntL signal with the Data_Not_Ready bit negated. Note that on

power up (including hot insertion) the module should post this completion of reset

interrupt without requiring a reset.

4.1.1.3 LPMode

The LPMode pin shall be pulled up to Vcc in the QSFP+ module. This function is affected

by the LPMode pin and the combination of the Power_over-ride and Power_set software

control bits (Address A0h, byte 93 bits 0,1).

The module has two modes a low power mode and a high power mode. The high power mode

operates in one of the four power classes.

When the module is in a low power mode it has a maximum power consumption of 1.5W. This

protects hosts that are not capable of cooling higher power modules, should such modules

be accidentally inserted.

The modules 2-wire serial interface and all laser safety functions must be fully

operational in this low power mode. The module shall still support the completion of

reset interrupt in this low power mode.

If the Extended Identifier bits (Page 00h, byte 129 bits 6-7) indicate a power

consumption greater than 1.5W and the module is in low power mode it must reduce its

power consumption to less than 1.5W while still maintaining the functionality above. The

exact method of accomplishing low power is not specified, however it is likely that

either the Tx or Rx or both will not be operational in this state.

If the Extended Identifier bits (Page 00h, byte 129 bits 6-7) indicate that its power

consumption is less than 1.5W then the module shall be fully functional independent of

whether it is in low power or high power mode.

The Module should be in low power mode if the LPMode pin is in the high state, or if the

Power_ override bit is in the high state and the Power_set bit is also high. The

module should be in high power mode if the LPMode pin is in the low state, or the

Power_override bit is high and the Power_set bit is low. Note that the default state

for the Power_override bit is low.