ISE与Modelsim协同:提升FPGA开发效率的仿真教程

需积分: 10 201 浏览量

更新于2024-07-19

收藏 3.03MB PDF 举报

在使用Xilinx ISE进行FPGA开发过程中,与Modelsim的集成仿真是提升效率的关键步骤。以下是关于如何结合ISE和Modelsim进行有效仿真的详细指南:

1. ISE的工程建立:

- 创建新项目时,需确保工程名和文件夹路径均为英文,避免编译错误。

- 选择芯片类型可以在后续编辑阶段调整,无需在此时指定。

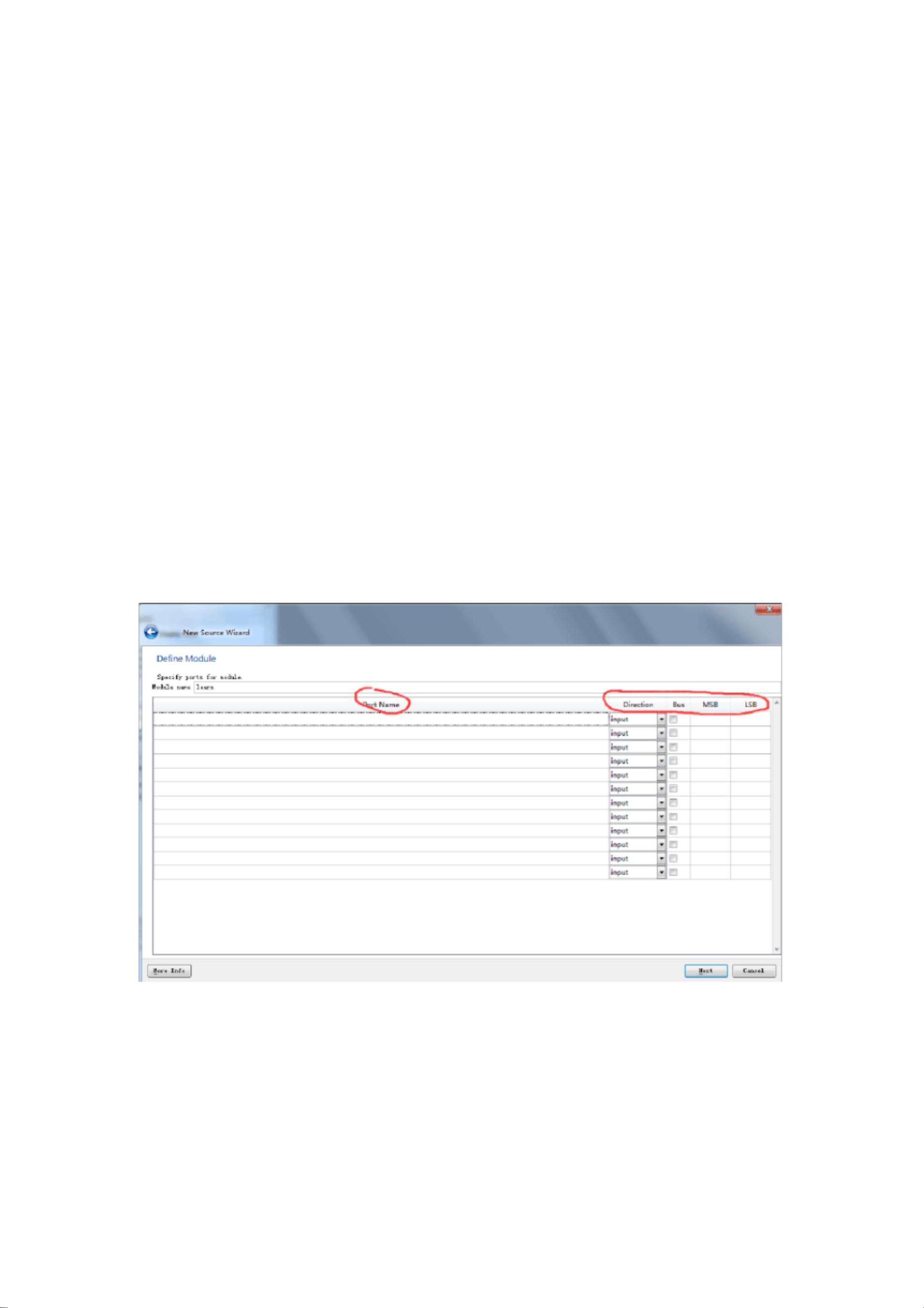

2. 添加Verilog模块:

- 在工程中添加Verilog模块,选择`Newsource`,并指定文件类型为`verilogmodule`。

- 文件命名应与工程名一致,便于后期仿真引用。

- 设置输入和输出端口,包括单个端口的方向(input或output),以及总线形式的配置。

3. 处理IP核:

- 为简化设计,可以利用预封装的IP核,如一个并串转换器。这些IP核类似于Matlab中的内置函数,只需设定参数并实例化调用。

- IP核的添加需要在Verilog文件内进行,因为它们属于该文件的组成部分。

4. Modelsim仿真:

- 使用Modelsim进行仿真前,需确保ISE已经根据设置完成了基础配置。

- 调用Modelsim仿真功能,通常是在Verilog文件中右键选择`Newsource`,然后选择所需的IP核进行模型的搭建和仿真。

5. 仿真流程:

- 将Verilog模块和IP核连接起来,形成完整的系统模型。

- 在Modelsim环境中,加载工程并设置仿真配置,如时钟周期、初始条件等。

- 运行仿真,观察波形和信号行为,验证设计的功能性和正确性。

- 如有需要,可以使用Modelsim提供的调试工具进行深入分析,如逻辑查看、逻辑比较等。

通过这种联合使用方式,开发者能够有效地利用ISE的工程管理功能和Modelsim的强大仿真能力,提升FPGA设计的开发效率和准确性。理解并掌握这两者之间的协同工作,对于FPGA项目的成功至关重要。

2021-03-06 上传

196 浏览量

124 浏览量

129 浏览量

226 浏览量

2024-11-02 上传

179 浏览量

222 浏览量

wywjzdl

- 粉丝: 0

- 资源: 3

最新资源

- servo-example-0.5.2.zip

- net.tsinghua:针对清华学生的跨平台自动登录实用程序

- 49个苹果app图标 .sketch素材下载

- 基于HTML实现的仿享客零食网触屏版html5手机wap购物网站模板下载(css+html+js+图样).zip

- 单片机太阳能路灯控制系统仿真protues

- node-simple-deploy

- HWHelpNow:hwhelpnow.com官方GitHub Repo

- yii2-widgets:Yii Framework 2.0有用的小部件集合

- 易语言复制组件到选择夹子夹

- MDB_3.0,999玫瑰c语言表白源码,c语言

- dotfiles:每天使用.dotfiles

- storemate-backend-leveldb-0.9.23.zip

- 基于ASP.net数据存储与交换系统设计(源代码+论文).rar

- Javascript-30-WesBos

- 夸克:离线时保持快乐| 世界上第一个离线搜索引擎

- Recipes