深度解析:静态时序分析在IC设计中的关键应用

需积分: 9 106 浏览量

更新于2024-07-21

收藏 834KB PDF 举报

静态时序分析(STA)是现代集成电路(IC)设计过程中不可或缺的关键技术,特别是在深度亚微米工艺时代,随着芯片复杂性和系统单芯片(SOC)设计的发展,保证IC性能和功能的稳定运行变得尤为重要。本文旨在深入解读静态时序分析的基础概念及其在IC设计流程中的应用。

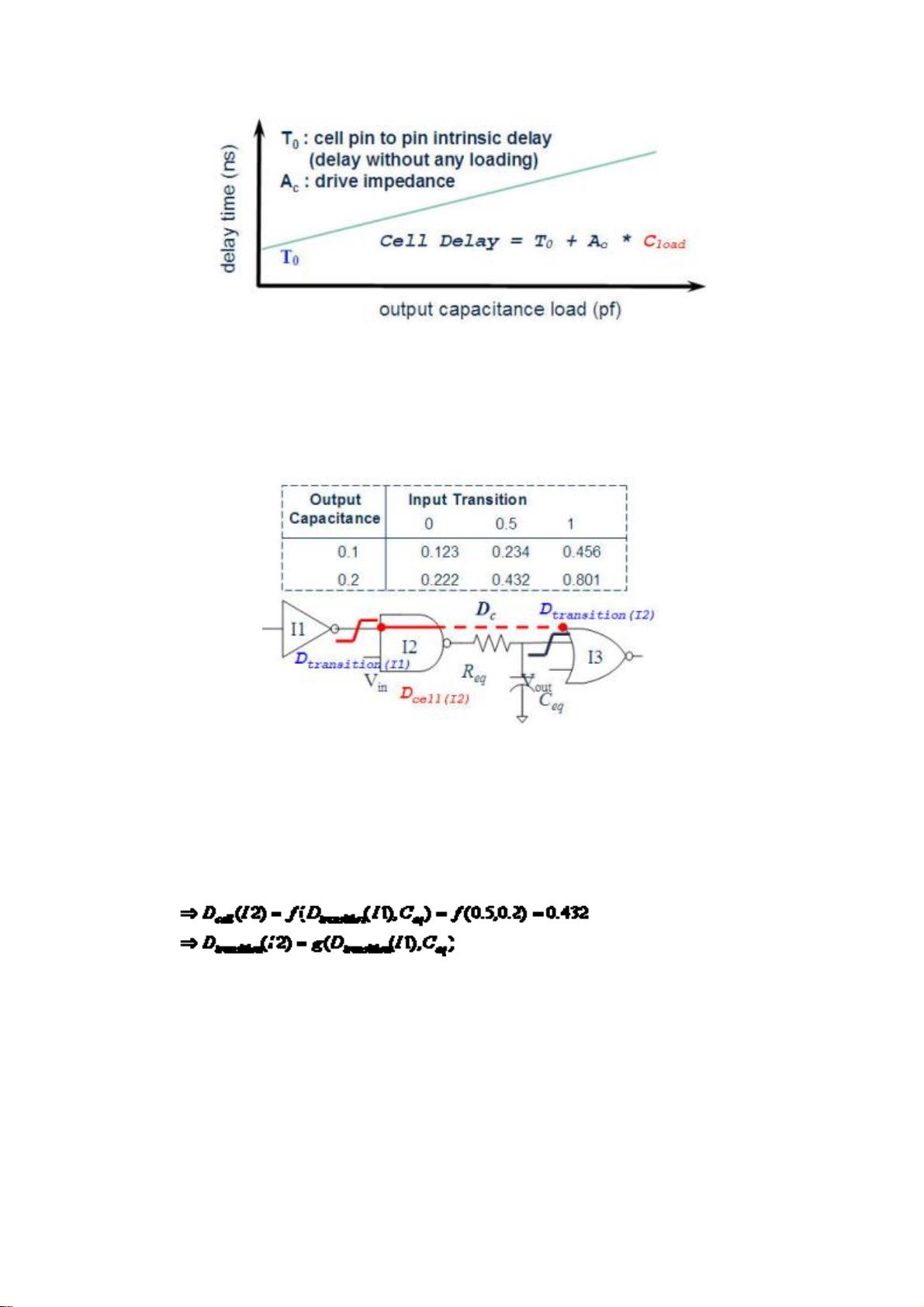

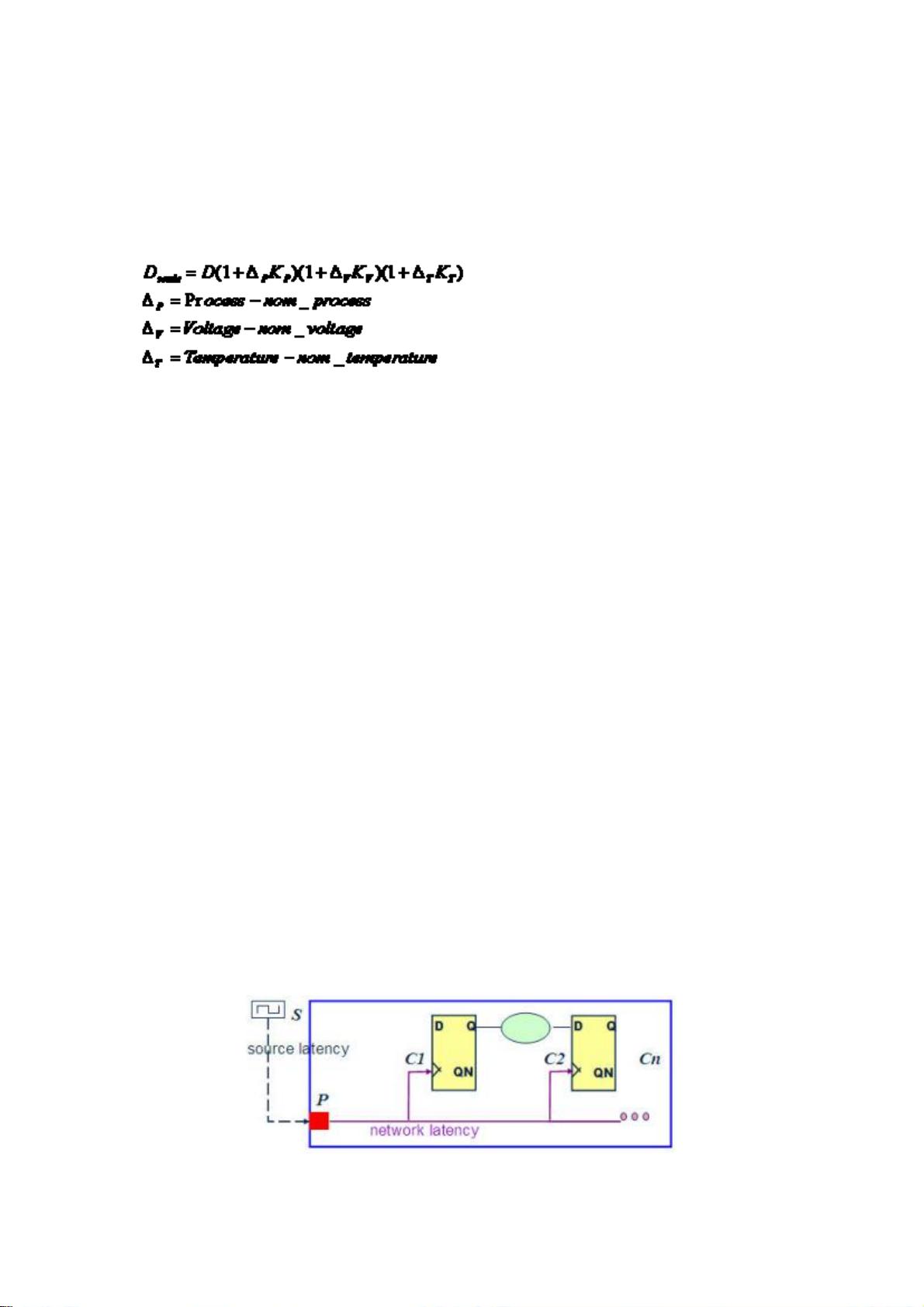

首先,我们需要理解什么是STA。它是一种通过套用预定义的时序模型来评估电路在给定时序约束下的行为。模型会考虑每个逻辑门或路径的延迟特性,以及信号从输入到输出所需的时间。STA主要分为两类分析方法:Path-Based(路径基于)和Block-Based(块基于)。

Path-Based分析法以信号路径为核心,如图一所示,信号A和B分别在不同时间到达电路输入端,然后通过一系列逻辑门,最终到达输出Y。在分析过程中,设计者会设定信号到达输入的时间(AT)和到达输出所需的最小时间(RT)。例如,信号A需要在AT=2时到达,信号B在AT=5,且所有信号需在RT=10前输出。通过计算每条路径的实际延迟时间,对比RT,可以判断路径是否满足时序要求。在这个例子中,P1路径满足时序条件,而P2路径则不满足。

Block-Based方法则关注整个电路单元或模块的时序行为,它会汇总各个路径的延迟,并根据整体性能进行评估。这种方法有助于设计师在设计初期就考虑到全局时序问题,而不是孤立地看待每个路径。

在实际的IC设计流程中,STA通常在以下阶段被应用:

1. 设计初期:作为设计验证的一部分,帮助优化设计,确保电路符合预定的性能指标。

2. 布局与布线阶段:在物理设计过程中,通过STA进行详细布局和布线后的时间分析,确保电路不会因为信号路径过长或信号质量问题导致性能下降。

3. 版图验证:完成物理实现后,再次进行STA,确保版图满足设计规范和时序要求。

4. 仿真与调试:在测试和调试阶段,STA能够及时发现并修复可能因设计更改而产生的时序问题。

静态时序分析是保证IC质量、提升设计效率和降低成本的重要工具。理解和掌握STA的基础原理和实践技巧,对于任何从事IC设计的工程师来说都是至关重要的技能。通过结合理论知识和实际案例,设计师可以更好地应对复杂电路的挑战,确保产品的性能稳定和可靠性。

2009-02-19 上传

252 浏览量

2021-10-26 上传

2021-10-26 上传

2021-10-26 上传

2012-09-02 上传

点击了解资源详情

2021-09-29 上传

2008-03-13 上传

bin_ge_ge

- 粉丝: 0

- 资源: 8

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常