1 2 3 4 5 6 7 8

A

B

C

D

87654321

D

C

B

A

Title

Number RevisionSize

A3

Date: 18-Feb-2002 Sheet of

File: D:\文档资料\吴忠仪表\FOURLAYER_01.ddbDrawn By:

A0R

48

A1R

47

A2R

46

A3R

45

A4R

44

A5R

43

A6R

42

A7R

41

A8R

40

A9R

39

A10R

38

A11R

37

A12R

36

A0L

55

A1L

56

A2L

57

A3L

58

A4L

59

A5L

60

A6L

61

A7L

62

A8L

63

A9L

64

A10L

65

A11L

66

A12L

67

I/O0L

8

I/O1L

9

I/O2L

10

I/O3L

11

I/O4L

12

I/O5L

13

I/O6L

15

I/O7L

16

I/O0R

19

I/O1R

20

I/O2R

21

I/O3R

23

I/O4R

24

I/O5R

25

I/O6R

26

I/O7R

27

CER

32

OER

29

R/WR

30

INTR

49

BUSYR

50

SEMR

31

CEL

3

OEL

6

R/WL

5

INTL

54

BUSYL

53

SEML

4

N/C

7

N/C

1

N/C

2

N/C

28

N/C

33

N/C

34

VCC

17

VCC

22

GND

14

GND

18

VCC

68

GND

35

GND

52

M/S

51

U1

IDT7005

EA/VP

31

XTAL1

19

XTAL2

18

RST

9

RD

17

WR

16

INT0/P3.2

12

INT1/P3.3

13

T0/P3.4

14

T1/P3.5

15

P1.0

1

P1.1

2

P1.2

3

P1.3

4

P1.4

5

P1.5

6

P1.6

7

P1.7

8

P0.0

39

P0.1

38

P0.2

37

P0.3

36

P0.4

35

P0.5

34

P0.6

33

P0.7

32

P2.0

21

P2.1

22

P2.2

23

P2.3

24

P2.4

25

P2.5

26

P2.6

27

P2.7

28

PSEN

29

ALE/P

30

TXD/P3.1

11

RXD/P3.0

10

VCC

40

GND

20

U3

W78E58

D0

3

Q0

2

D1

4

Q1

5

D2

7

Q2

6

D3

8

Q3

9

D4

13

Q4

12

D5

14

Q5

15

D6

17

Q6

16

D7

18

Q7

19

OE

1

LE

11

VCC

20

GND

10

U4

74LS373

A

1

B

2

C

3

E1

4

E2

5

E3

6

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

VCC

16

GND

8

U6

74LS138

D1

3

Q1

2

D2

4

Q2

5

D3

7

Q3

6

D4

8

Q4

9

D5

13

Q5

12

D6

14

Q6

15

D7

17

Q7

16

D8

18

Q8

19

CLK

11

CLR

1

VCC

20

GND

10

U9

74LS273

AD0

23

AD1

24

AD2

25

AD3

26

AD4

27

AD5

28

AD6

1

AD7

2

CS

4

ALE

3

RD

5

WR

6

INT

16

CLK OUT

7

RST

17

TX0

13

TX1

14

RX0

19

RX1

20

MODE

11

VDD1

22

VSS1

8

VDD2

18

VSS2

21

VDD3

12

VSS3

15

XTL1

9

XTL2

10

U10

SJA1000

MR

1

VCC

2

GND

3

PFI

4

PFO

5

WDI

6

RESET

7

WDO

8

U11

MAX706

1

2

3

GND

7

VCC

14

U12A

74LS32

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LA10

LA11

LA12

LAD0

LAD1

LAD2

LAD3

LAD4

LAD5

LAD6

LAD7

LINT0

LRD

LWR

C4

VCC

C5

1 2

XTAL2

C23

C24

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

C6

VCC

PSEN

ALE

ALE

MA13

MA14

MA15

CS7005

CSS JA1000

CS273

RDRD

WR

RD

WR

C9

VCC

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

C10

VCC

C11

C12

C13

VCC

1 2

XTAL3

C25

C26

DRAIN

3

V+

5

V-

1

CANH

4

CANL

2

J1

CONNECTOR

TXD

1

RXD

4

Vref

5

Rs

8

CANH

7

CANL

6

VCC

3

GND

2

U14 PCA82C251

Vin

1

GND

2

+5V

3

U15 MC7805T

1

3

42

Q1

C27

R8

R9

12

E2

10V TANT

VCC

R10

C28

C14

VCC

PHILIPS C AN

TR ANSCEIVER

11-25VDC

A K

D1

TXD

TXD

RXD

RXD

CS7005

C15

VCC

ALE

CSS JA1000

RD

WR

INT0

INT1

INT0

INT1

R2

VCC

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

M1 DIP-16

1 2

F1A

1 3

F1B

1 4

F1C

1 5

F1D

1 6

F1E

1 7

F1F

1 8

F1G

1 9

F1H

DIN1

DIN2

DIN3

DIN4

DIN5

DIN6

DIN7

VCC

DIN8

DIN8

DIN1

DIN7

DIN2

DIN6

DIN3

DIN5

DIN4

DIN1

DIN2

DIN3

DIN4

DIN5

DIN6

DIN7

WDI

DIN8

WDI

R11

R12

C16

VCC

S2

SWITCH

AK

D2

AK

D3

V+

V+

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

C17

VCC

CS273

WR

CLK

CLK

C18

VCC

2

1

3

L1

LED1

2

1

3

L2

LED2

R4

R5

R6

R7

DeviceNet Node Controller

1

Zhang Ji

Zhang Ji

NOTES:

G

SD

RST

RST

RST 1 2

GND

7

VCC

14

U16A

C19

VCC

RST

TO SJA1000

TO 8031RIGHT

FROM 74LS04

FROM 80 31RIG HT

PHILIP S STAN D-ALON E

CAN CONTROLLER

1

HIGH-SP PE D

8K×8 DUA L-PO RT

STATIC RAM

INTERNATIONA L RECTIFIER

HEXFET P OWE R MOSFET

DeviceNet

DUAL-CL OUR L ED

DUAL-CO LOU R LE D

μ-P SUP ERVISOR

C20

CHASSIS

R13

1

2

J2

JUMPER

CABLE TERMINATION

+5v SU PP LY

GND-B

2

+5V-B

1

NC.

3

NC.

4

+5V-P

5

GND

6

NC.

7

A12

8

A0

9

A1

10

A2

11

A3

12

A4

13

A5

14

A6

15

A7

16

A8

17

A9

18

D0

19

D1

20

D2

21

D3

22

D4

23

D5

24

D6

25

D7

26

BUSY

27

IRQ

28

RD

29

WR

30

CE

31

RESET

32

NULL

33

NULL

34

PIN1

PIN

LA0

LA1

LA2

LA3

LA4

LA5

LA6

LA7

LA8

LA9

LAD0

LAD1

LAD2

LAD3

LAD4

LAD5

LAD6

LAD7

LINT0

LRD

LWR

ACE

VCC

ACE

R14

R15

R16

VCC

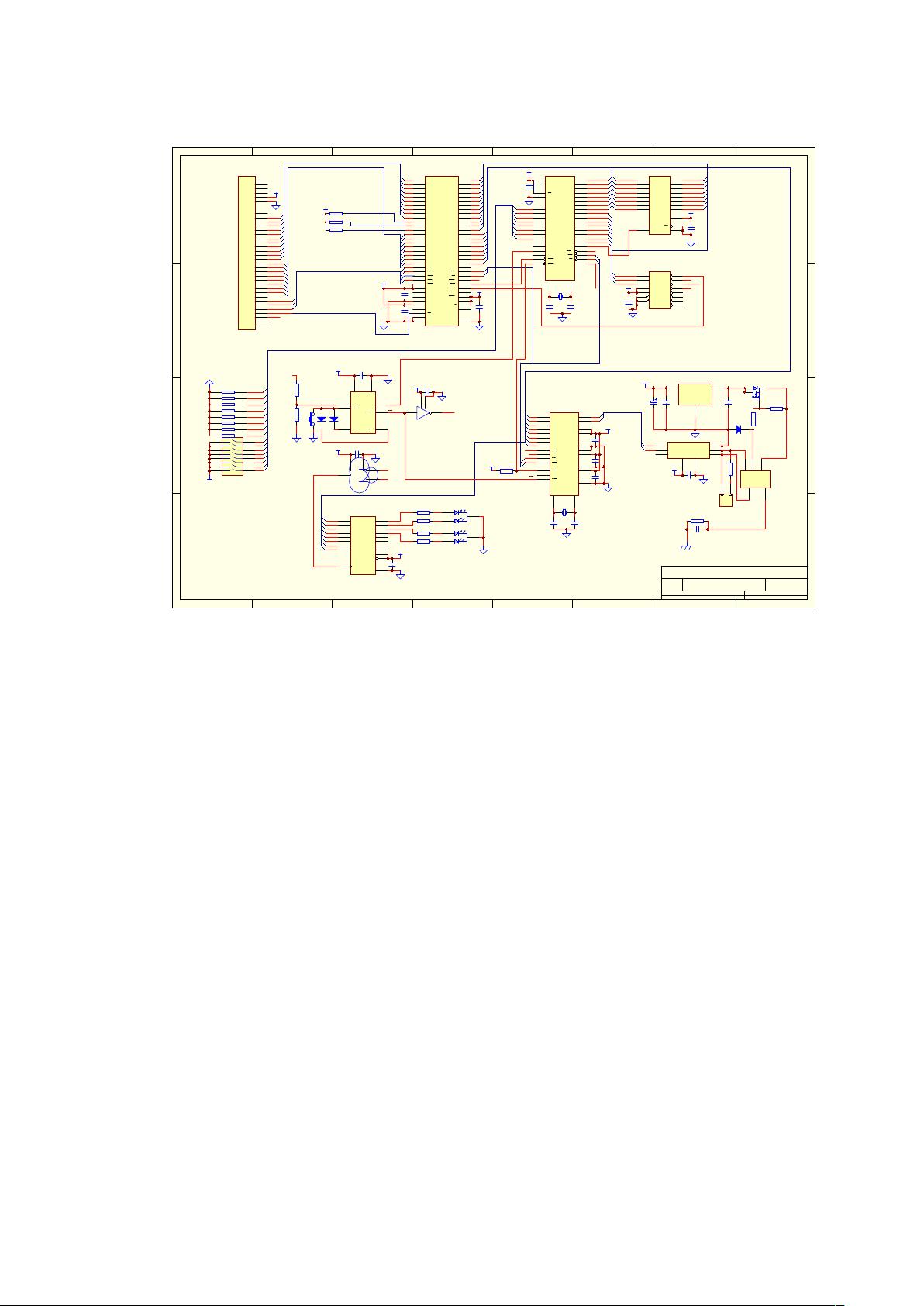

硬件设计原理图

CAN收发器82C251

CAN收发器82C251(Transceiver)的主要作用是收发CAN总线上的信号,即,一方面

将总线信号转换为CAN控制器所需的信号,另一方面,将CAN控制器的输出信号转化为CAN

总线信号。DeviceNet通信节点选用PHILIPS PCA82C251收发器,其TXD、RXD引脚分别与

SJA1000的TXD和RXD引脚相连,CANL、CANH引脚分别连接到DeviceNet Connector的2、

4端。

拨码开关及状态LED显示

DeviceNet适配器通过一组拨码开关和两个双色二极管实现节点的MAC地址、波特率设

置以及节点和网络状态显示。由于DeviceNet最多支持64个从节点,并且只有三种波特率可

供选择,因此只需一个八位的DIP开关便可实现MAC地址和波特率的设置(其中六位用以设

置MAC地址,两位用来选择波特率)。对节点和网络状态分别采用一个双色二极管进行指示。

由于单片机接口的限制,硬件中通过一片74HC273锁存器扩展了一个输出接口,从而驱动两

个双色二极管进行显示。

硬件中将DIP开关通过上拉电阻接到单片机的P1口,并将其中的高两位用作波特率设

置、低六位用于MAC地址选择。将138译码器的片选输出Y3与单片机的写信号相或后连到273

的CLK输入端,由此扩展一个输出口用以驱动双色二极管进行状态显示。

双口RAM IDT7005

DeviceNet适配器通过一个具有中断功能的双口RAM IDT7005提供与其它应用电路的通

讯接口。IDT7005具有两套完全独立的数据线、地址线、读写控制线,允许两个CPU对双口

RAM的的同一个单元在不同的时间进行读写。具有两套完全独立的中断逻辑,实现两个CPU

间的握手控制信号。IDT7005的最高两个字节1FFEH和1FFFH分别兼做两个断口的中断逻辑

单元。