Verilog实现的时序计数电路设计与验证

版权申诉

"该资源是一份关于基于Verilog的计数器时序电路设计的实验报告,涵盖了设计、仿真、综合、时序分析和形式化验证等步骤,旨在提升学生在数字IC设计领域的实践能力。"

这篇实验报告详细介绍了如何使用Verilog语言设计一个带有异步复位和使能控制的十进制计数器,并通过多种EDA工具进行验证和分析。首先,计数器的基本功能被定义为:在复位信号rst为低电平时,计数器清零,输出b设为0;在非复位且使能信号en为高电平时,计数从0递增,当计数到10时,输出b变为1。如果en保持高电平,计数器和输出将保持这一状态;en为低电平时,计数器和输出重置为0。

实验内容包括了几个关键步骤:

1. 设计与仿真:使用Verilog语言编写计数器的代码,然后在NCverilog或其他仿真工具(如Modelsim、Questasim)中进行功能仿真,确保计数器按照预期工作。

2. 综合:利用DesignCompiler将Verilog代码转换为适合特定工艺库(这里是smic18CMOS工艺库)的门级网表。

3. 门级仿真:在NCverilog中进行门级仿真,检查综合后的电路是否仍能正确执行计数功能。

4. 静态时序分析:通过PrimeTime进行静态时序分析,评估电路的延迟和时钟约束,确保满足时间的准确度要求。

5. 形式化验证:使用Formality进行形式化验证,证明Verilog代码的逻辑等价性,以避免潜在的逻辑错误。

实验环境要求包括了相应的软件工具,如仿真工具NCverilog、综合工具DesignCompiler、时序分析工具PrimeTime和形式化验证工具Formality,以及用于远程访问Linux服务器的Xmanager。硬件环境则需要Linux服务器来运行这些工具。

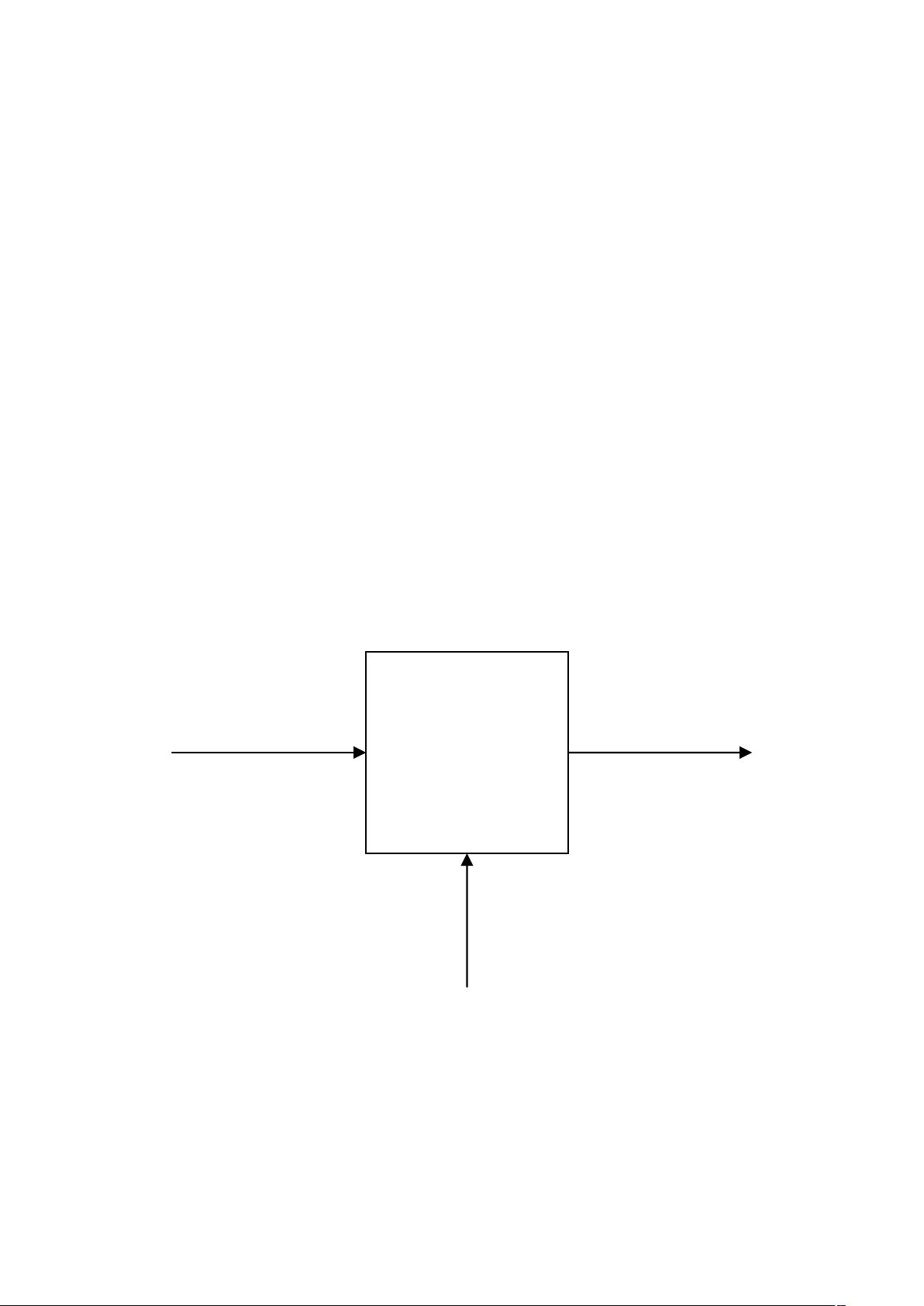

此外,报告还讨论了计数器在不同领域如工业生产、数字系统、交通信号控制等的应用,强调了计数器在统计和自动化过程中的重要作用。在设计方案部分,提到了顶层设计,即顶层模块作为整个系统的主体,包含了所有底层模块的实例化和连接关系,展示了计数电路的模块化设计思路。

这个实验旨在让学生掌握Verilog语言进行数字集成电路设计的基本流程,熟悉EDA工具的使用,同时锻炼其文档撰写能力。通过完成这一系列任务,学生能够深入理解时序电路的工作原理和设计方法,为今后的数字IC设计奠定基础。

2021-09-29 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

陆已十六

- 粉丝: 735

- 资源: 14

最新资源

- ghaction-publish-ghpages:将内容发布到GitHub Pages

- HTML5 Video Speed Control-crx插件

- 人工智能实验2020年秋季学期.zip

- PyPI 官网下载 | vector_quantize_pytorch-0.4.0-py3-none-any.whl

- form:将您的Angular2 +表单状态保留在Redux中

- Tensorflow_practice:딥러닝,머신러닝

- Dijkstra.rar_matlab例程_matlab_

- 任何点复选框

- 人工智能写诗.zip

- Parstagram:使用私有存储服务器模仿Instagram

- mod-1白板挑战牌卡片sgharms测试webdev资金

- Slack Panels-crx插件

- PyPI 官网下载 | vectorian-0.9.2-cp38-cp38-macosx_10_9_x86_64.whl

- react-card-component:React卡组件Libaray

- 人工智能与实践 bilibili.zip

- Architecture-Website