+3.3V

B35_IO0[10]

B35_IO25[10]

B35_L21_P[10]

B35_L21_N[10]

B35_L22_P[10]

B35_L22_N[10]

B35_L20_P[10]

B35_L20_N[10]

B35_L23_P[10]

B35_L23_N[10]

B35_L19_P[10]

B35_L19_N[10]

B35_L16_P[10]

B35_L16_N[10]

B35_L13_P[10]

B35_L13_N[10]

B35_L5_P[10]

B35_L5_N[10]

B35_L2_P[10]

B35_L2_N[10]

B35_L8_P[10]

B35_L8_N[10]

B35_L6_P [10]

B35_L6_N [10]

B35_L15_P [10]

B35_L15_N [10]

B35_L11_P [10]

B35_L11_N [10]

B35_L9_P [10]

B35_L9_N [10]

B35_L18_P [10]

B35_L18_N [10]

B35_L10_P [10]

B35_L10_N [10]

B35_L4_P [10]

B35_L4_N [10]

B35_L17_P [10]

B35_L17_N [10]

B35_L1_P [10]

B35_L1_N [10]

B35_L14_P [10]

B35_L14_N [10]

B35_L3_P [10]

B35_L3_N [10]

B35_L12_P [10]

B35_L12_N [10]

B35_L7_P [10]

B35_L7_N [10]

PL_LED [2]

B34_IO0[10]

B34_IO25[10]

B34_L21_P[10]

B34_L21_N[10]

B34_L23_P[10]

B34_L23_N[10]

B34_L3_P[10]

B34_L3_N[10]

B34_L24_P[10]

B34_L24_N[10]

B34_L4_P[10]

B34_L4_N[10]

B34_L2_P[10]

B34_L2_N[10]

B34_L16_P[10]

B34_L16_N[10]

B34_L5_P[10]

B34_L5_N[10]

B34_L14_P[10]

B34_L14_N[10]

B34_L22_P[10]

B34_L22_N[10]

B34_L11_P [10]

B34_L11_N [10]

B34_L12_N [10]

B34_L20_P [10]

B34_L20_N [10]

B34_L17_P [10]

B34_L17_N [10]

B34_L15_P [10]

B34_L15_N [10]

B34_L13_P [10]

B34_L13_N [10]

B34_L10_P [10]

B34_L10_N [10]

B34_L7_P [10]

B34_L7_N [10]

B34_L8_P [10]

B34_L8_N [10]

B34_L19_P [10]

B34_L19_N [10]

B34_L18_P [10]

B34_L18_N [10]

B34_L9_P [10]

B34_L9_N [10]

B34_L6_P [10]

B34_L6_N [10]

B34_L1_P [10]

B34_L1_N [10]

B35_L24_P [10]

Design Name

Size Page Name Rev

Date: Sheet

of

1.0

ZYNQ-CORE

A4

3 11Thursday, June 13, 2019

03_FPGA Bank13,Bank34,Bank35

Design Name

Size Page Name Rev

Date: Sheet

of

1.0

ZYNQ-CORE

A4

3 11Thursday, June 13, 2019

03_FPGA Bank13,Bank34,Bank35

Design Name

Size Page Name Rev

Date: Sheet

of

1.0

ZYNQ-CORE

A4

3 11Thursday, June 13, 2019

03_FPGA Bank13,Bank34,Bank35

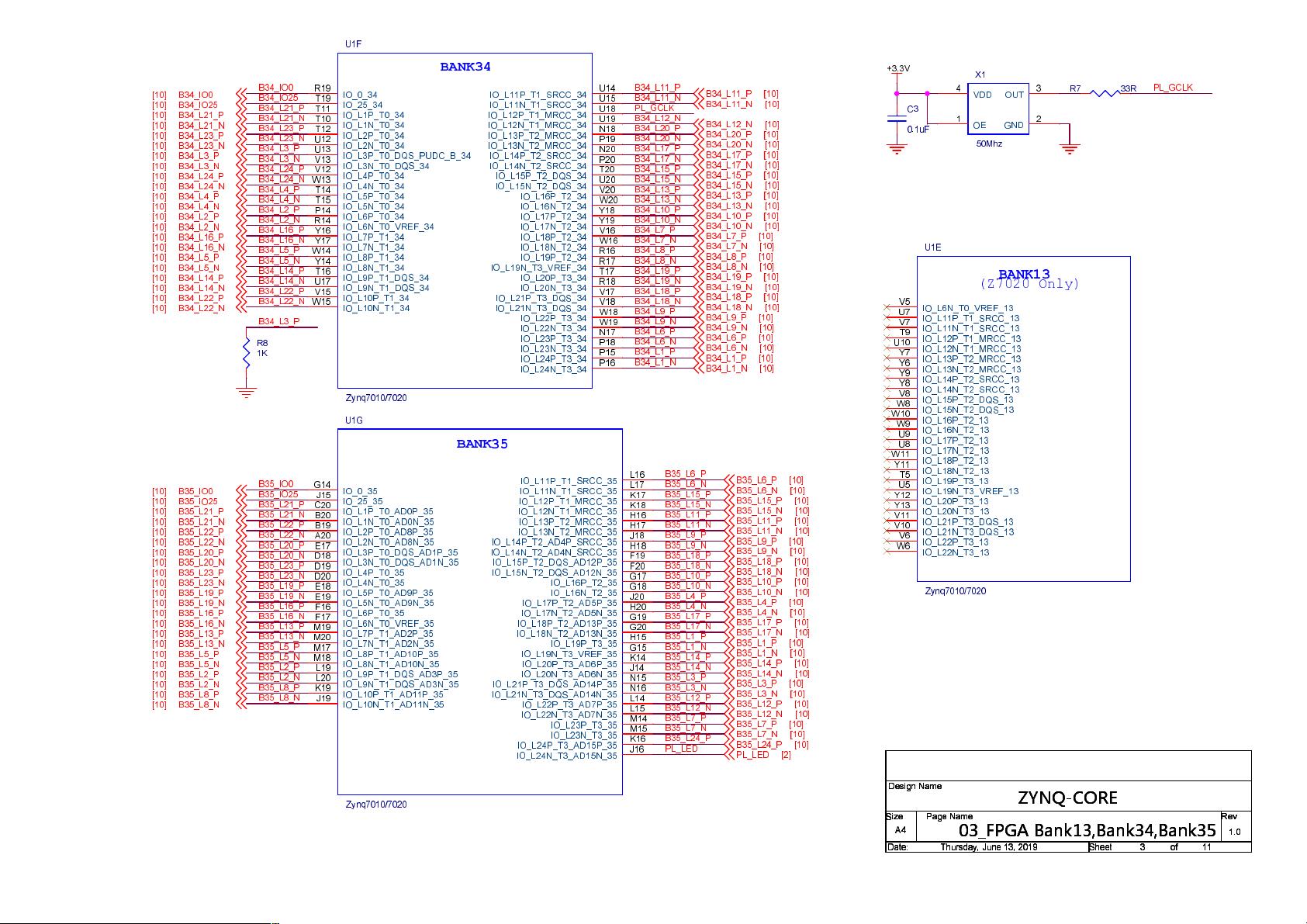

BANK35

U1G

Zynq7010/7020

IO_0_35

G14

IO_25_35

J15

IO_L1P_T0_AD0P_35

C20

IO_L1N_T0_AD0N_35

B20

IO_L2P_T0_AD8P_35

B19

IO_L2N_T0_AD8N_35

A20

IO_L3P_T0_DQS_AD1P_35

E17

IO_L3N_T0_DQS_AD1N_35

D18

IO_L4P_T0_35

D19

IO_L4N_T0_35

D20

IO_L5P_T0_AD9P_35

E18

IO_L5N_T0_AD9N_35

E19

IO_L6P_T0_35

F16

IO_L6N_T0_VREF_35

F17

IO_L7P_T1_AD2P_35

M19

IO_L7N_T1_AD2N_35

M20

IO_L8P_T1_AD10P_35

M17

IO_L8N_T1_AD10N_35

M18

IO_L9P_T1_DQS_AD3P_35

L19

IO_L9N_T1_DQS_AD3N_35

L20

IO_L10P_T1_AD11P_35

K19

IO_L10N_T1_AD11N_35

J19

IO_L11P_T1_SRCC_35

L16

IO_L11N_T1_SRCC_35

L17

IO_L12P_T1_MRCC_35

K17

IO_L12N_T1_MRCC_35

K18

IO_L13P_T2_MRCC_35

H16

IO_L13N_T2_MRCC_35

H17

IO_L14P_T2_AD4P_SRCC_35

J18

IO_L14N_T2_AD4N_SRCC_35

H18

IO_L15P_T2_DQS_AD12P_35

F19

IO_L15N_T2_DQS_AD12N_35

F20

IO_L16P_T2_35

G17

IO_L16N_T2_35

G18

IO_L17P_T2_AD5P_35

J20

IO_L17N_T2_AD5N_35

H20

IO_L18P_T2_AD13P_35

G19

IO_L18N_T2_AD13N_35

G20

IO_L19P_T3_35

H15

IO_L19N_T3_VREF_35

G15

IO_L20P_T3_AD6P_35

K14

IO_L20N_T3_AD6N_35

J14

IO_L21P_T3_DQS_AD14P_35

N15

IO_L21N_T3_DQS_AD14N_35

N16

IO_L22P_T3_AD7P_35

L14

IO_L22N_T3_AD7N_35

L15

IO_L23P_T3_35

M14

IO_L23N_T3_35

M15

IO_L24P_T3_AD15P_35

K16

IO_L24N_T3_AD15N_35

J16

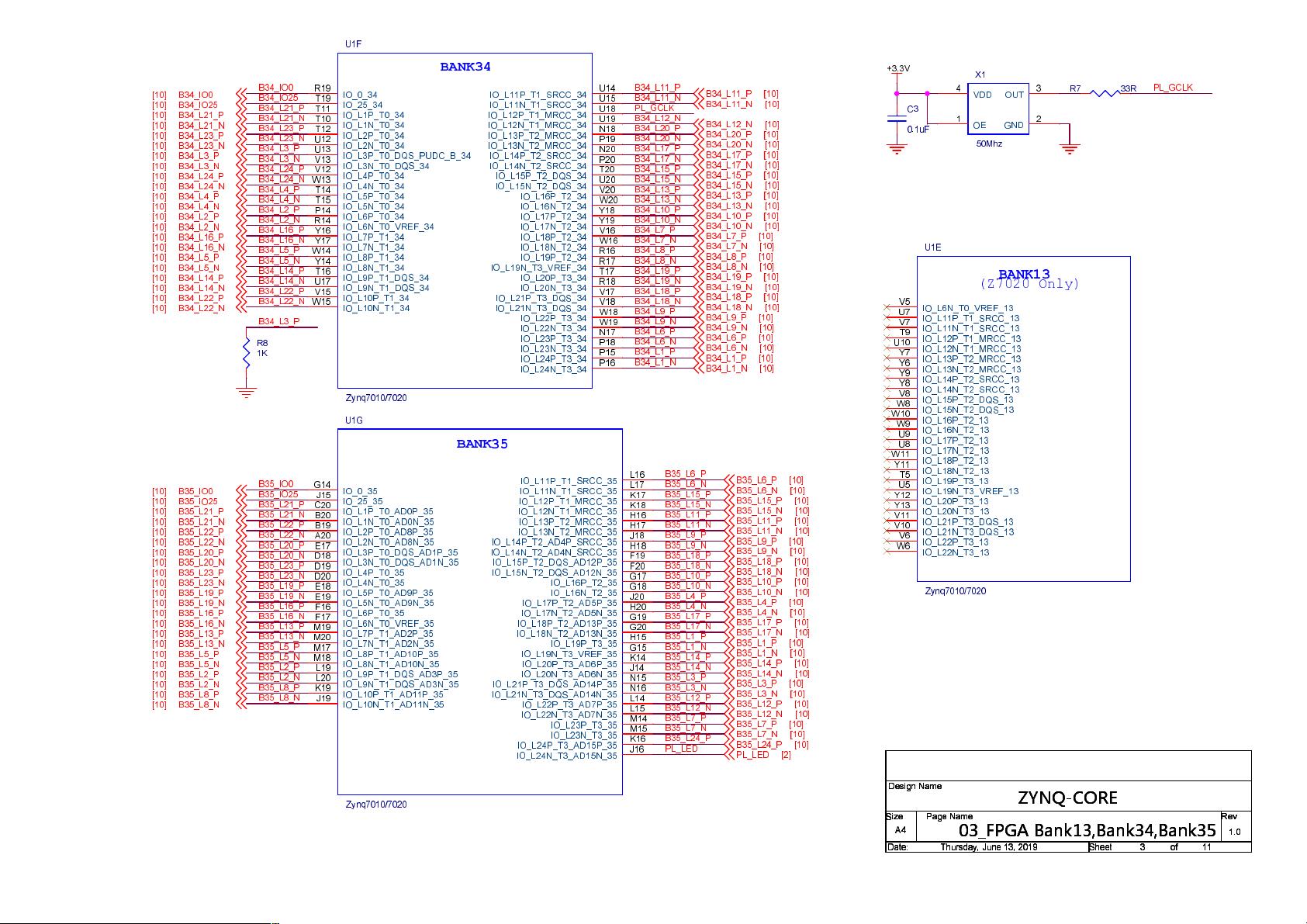

X1

50Mhz

OE

1

GND

2

OUT

3

VDD

4

BANK13

(Z7020 Only)

U1E

Zynq7010/7020

IO_L6N_T0_VREF_13

V5

IO_L11P_T1_SRCC_13

U7

IO_L11N_T1_SRCC_13

V7

IO_L12P_T1_MRCC_13

T9

IO_L12N_T1_MRCC_13

U10

IO_L13P_T2_MRCC_13

Y7

IO_L13N_T2_MRCC_13

Y6

IO_L14P_T2_SRCC_13

Y9

IO_L14N_T2_SRCC_13

Y8

IO_L15P_T2_DQS_13

V8

IO_L15N_T2_DQS_13

W8

IO_L16P_T2_13

W10

IO_L16N_T2_13

W9

IO_L17P_T2_13

U9

IO_L17N_T2_13

U8

IO_L18P_T2_13

W11

IO_L18N_T2_13

Y11

IO_L19P_T3_13

T5

IO_L19N_T3_VREF_13

U5

IO_L20P_T3_13

Y12

IO_L20N_T3_13

Y13

IO_L21P_T3_DQS_13

V11

IO_L21N_T3_DQS_13

V10

IO_L22P_T3_13

V6

IO_L22N_T3_13

W6

R8

1K

BANK34

U1F

Zynq7010/7020

IO_0_34

R19

IO_L1P_T0_34

T11

IO_L1N_T0_34

T10

IO_L2P_T0_34

T12

IO_L2N_T0_34

U12

IO_L3P_T0_DQS_PUDC_B_34

U13

IO_L3N_T0_DQS_34

V13

IO_L4P_T0_34

V12

IO_L4N_T0_34

W13

IO_L5P_T0_34

T14

IO_L5N_T0_34

T15

IO_L6P_T0_34

P14

IO_L6N_T0_VREF_34

R14

IO_L7P_T1_34

Y16

IO_L7N_T1_34

Y17

IO_L8P_T1_34

W14

IO_L8N_T1_34

Y14

IO_L9P_T1_DQS_34

T16

IO_L9N_T1_DQS_34

U17

IO_L10P_T1_34

V15

IO_L10N_T1_34

W15

IO_L11P_T1_SRCC_34

U14

IO_L11N_T1_SRCC_34

U15

IO_L12P_T1_MRCC_34

U18

IO_L12N_T1_MRCC_34

U19

IO_L13P_T2_MRCC_34

N18

IO_L13N_T2_MRCC_34

P19

IO_L14P_T2_SRCC_34

N20

IO_L14N_T2_SRCC_34

P20

IO_L15P_T2_DQS_34

T20

IO_L15N_T2_DQS_34

U20

IO_L16P_T2_34

V20

IO_L16N_T2_34

W20

IO_L17P_T2_34

Y18

IO_L17N_T2_34

Y19

IO_L18P_T2_34

V16

IO_L18N_T2_34

W16

IO_L19P_T2_34

R16

IO_L19N_T3_VREF_34

R17

IO_L20P_T3_34

T17

IO_L20N_T3_34

R18

IO_L21P_T3_DQS_34

V17

IO_L21N_T3_DQS_34

V18

IO_L22P_T3_34

W18

IO_L22N_T3_34

W19

IO_L23P_T3_34

N17

IO_L23N_T3_34

P18

IO_L24P_T3_34

P15

IO_L24N_T3_34

P16

IO_25_34

T19

R7 33R

C3

0.1uF

B35_IO0

B35_IO25

B35_L21_P

B35_L21_N

B35_L22_P

B35_L22_N

B35_L20_P

B35_L20_N

B35_L23_P

B35_L23_N

B35_L19_P

B35_L19_N

B35_L16_P

B35_L16_N

B35_L13_P

B35_L13_N

B35_L5_P

B35_L5_N

B35_L2_P

B35_L2_N

B35_L8_P

B35_L8_N

B35_L6_P

B35_L6_N

B35_L15_P

B35_L15_N

B35_L11_P

B35_L11_N

B35_L9_P

B35_L9_N

B35_L18_P

B35_L18_N

B35_L10_P

B35_L10_N

B35_L4_P

B35_L4_N

B35_L17_P

B35_L17_N

B35_L1_P

B35_L1_N

B35_L14_P

B35_L14_N

B35_L3_P

B35_L3_N

B35_L12_P

B35_L12_N

B35_L7_P

B35_L7_N

B35_L24_P

PL_LED

B34_IO0

B34_IO25

B34_L21_P

B34_L21_N

B34_L23_P

B34_L23_N

B34_L3_P

B34_L3_N

B34_L24_P

B34_L24_N

B34_L4_P

B34_L4_N

B34_L2_P

B34_L2_N

B34_L16_P

B34_L16_N

B34_L5_P

B34_L5_N

B34_L14_P

B34_L14_N

B34_L22_P

B34_L22_N

B34_L11_P

B34_L11_N

PL_GCLK

B34_L12_N

B34_L20_P

B34_L20_N

B34_L17_P

B34_L17_N

B34_L15_P

B34_L15_N

B34_L13_P

B34_L13_N

B34_L10_P

B34_L10_N

B34_L7_P

B34_L7_N

B34_L8_P

B34_L8_N

B34_L19_P

B34_L19_N

B34_L18_P

B34_L18_N

B34_L9_P

B34_L9_N

B34_L6_P

B34_L6_N

B34_L1_P

B34_L1_N

B34_L3_P

PL_GCLK