MAX7000A系列CPLD芯片特性与应用

需积分: 10 173 浏览量

更新于2024-07-27

1

收藏 874KB PDF 举报

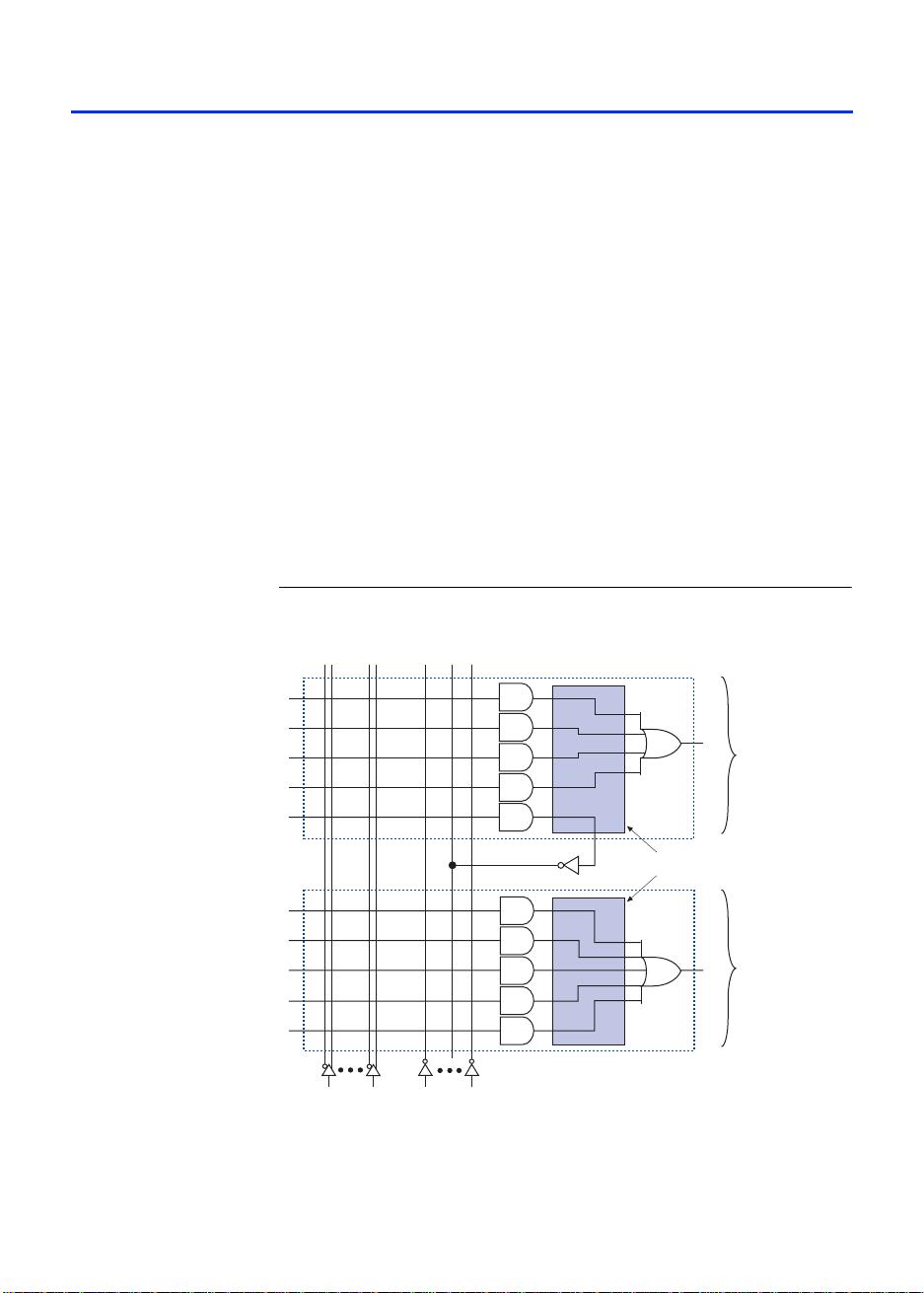

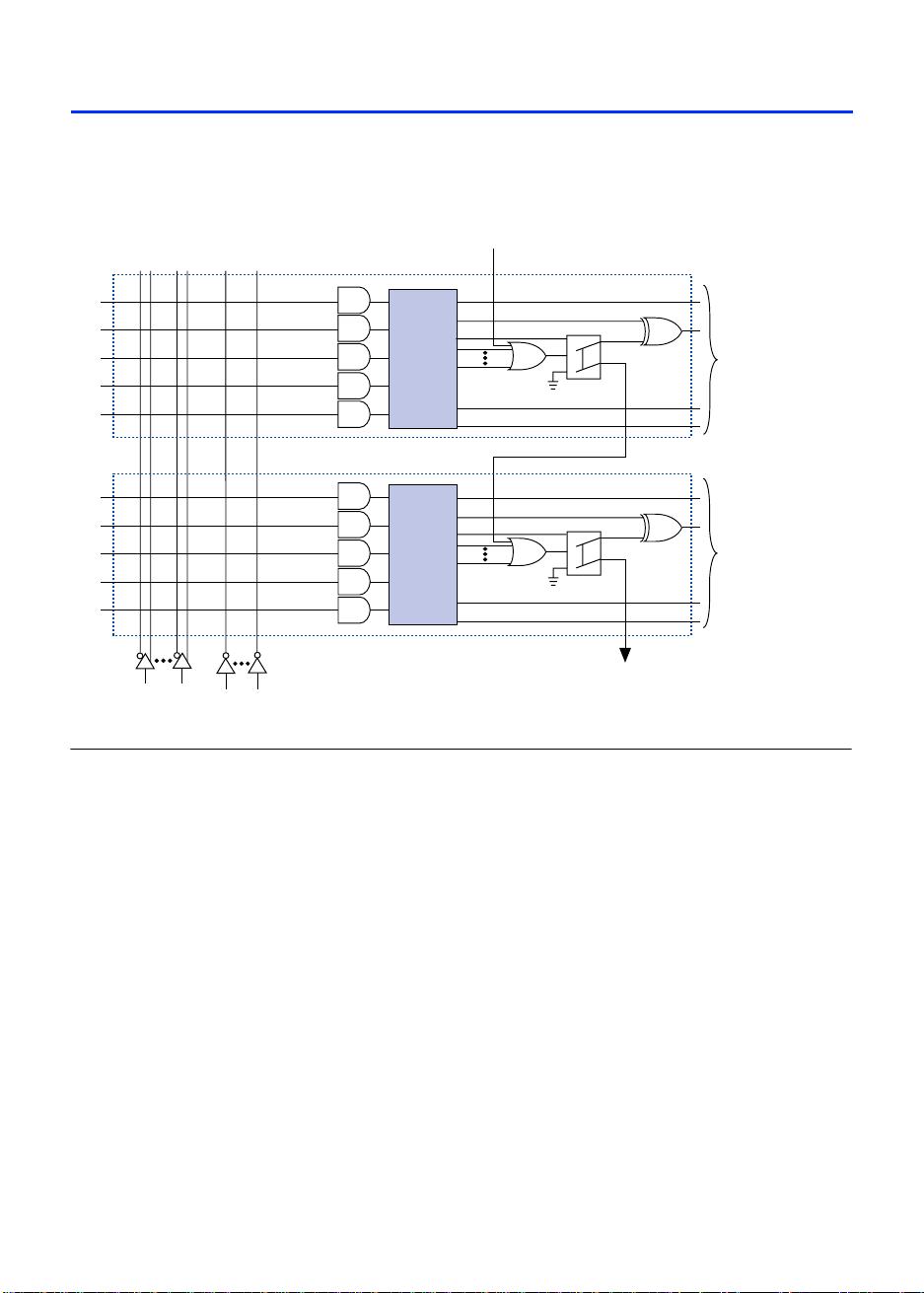

"EPM7512是一款CPLD(复杂可编程逻辑器件)芯片,主要应用于硬件开发,尤其在逻辑单元数据、宏单元的设计验证以及PCB布局布线时作为参考。该芯片具备3.3V的高性能EEPROM基础,采用第二代Multiple Array MatriX (MAX)架构。它支持在系统编程(ISP),并通过内置的IEEE Std.1149.1 JTAG接口实现,具有高级引脚锁定功能。EPM7512A系列的ISP电路符合IEEE Std.1532标准,而EPM7128A和EPM7256A系列则与IEEE Std.1532兼容。此外,该系列芯片内置边界扫描测试(BST)电路,遵循IEEE Std.1149.1标准,且支持JEDEC JAM Standard Test and Programming Language (STAPL) JESD-71标准。增强的ISP特性包括更快的编程算法(不适用于EPM7128A和EPM7256A设备)、ISP_Done位以确保完整编程(同样不适用于EPM7128A和EPM7256A设备)以及ISP期间I/O引脚上的上拉电阻。该芯片与5.0V的MAX7000S系列引脚兼容,提供了高密度的PLD解决方案。"

EPM7512芯片是Altera公司生产的一款CPLD,其核心特点是基于3.3V的EEPROM技术,能够在系统内进行编程,这极大地提高了设计的灵活性和便捷性。第二代MAX架构的采用使得EPM7512芯片在性能上有了显著提升,能够处理复杂的逻辑设计任务。通过集成的JTAG接口,该芯片可以按照IEEE Std.1149.1标准进行在系统编程,同时提供了一种高级的引脚锁定功能,以防止意外的编程更改。

在ISP特性方面,EPM7500A系列具有增强的ISP算法,可以加快编程速度,而ISP_Done位则保证了编程过程的完整性。在某些操作中,如EPM7128A和EPM7256A,这些特性可能不适用。在边界扫描测试方面,EPM7512符合IEEE Std.1149.1标准,允许对芯片的各个部分进行独立测试,增强了故障检测和诊断能力。

EPM7512还支持JEDEC的STAPL标准,这是一种用于测试和编程的标准化语言,简化了设备的测试流程。此外,为了保护I/O引脚在编程过程中不受影响,芯片在ISP期间会自动加上上拉电阻。

最后,引脚兼容性是EPM7512的一个重要优势,它可以直接替代5.0V的MAX7000S系列,这意味着用户可以在不改变硬件设计的情况下升级到这款更先进的3.3V芯片,从而获得更高的效率和更低的功耗。

EPM7512芯片是硬件开发者在逻辑设计和PCB布局中的理想选择,其高性能、在系统编程能力、测试兼容性和引脚兼容性使其成为现代电子系统设计中的重要组成部分。

2024-04-02 上传

2023-09-22 上传

2020-10-22 上传

2020-12-10 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-11-21 上传

ertert4we

- 粉丝: 0

- 资源: 1

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率