VHDL设计:2选1多路选择器与边沿触发器应用与仿真

需积分: 50 147 浏览量

更新于2024-09-15

收藏 80KB DOC 举报

在本篇关于多路选择器、边沿触发器和D锁存器的EDA实验中,主要探讨了如何使用VHDL语言设计并实现一个2选1多路选择器,这是一个基本的组合逻辑电路。实验的主要目标是让学生熟悉Quartus II工具的VHDL设计流程,包括文本输入、编译、仿真和硬件测试。

首先,实验要求设计者利用Quartus II创建一个2选1多路选择器,该选择器有两个输入端口a和b,一个选择信号s,以及一个输出端口y。选择器根据s的值决定从a或b信号中选择一个输出到y。设计时,应指定特定的引脚连接,例如,s0由键1(PIO0)控制,a、b和clock信号分别连接到特定的引脚。实验还涉及设置不同的时钟频率,如clock0接256Hz,clock2接8Hz,通过改变时钟频率实现不同的音调输出。

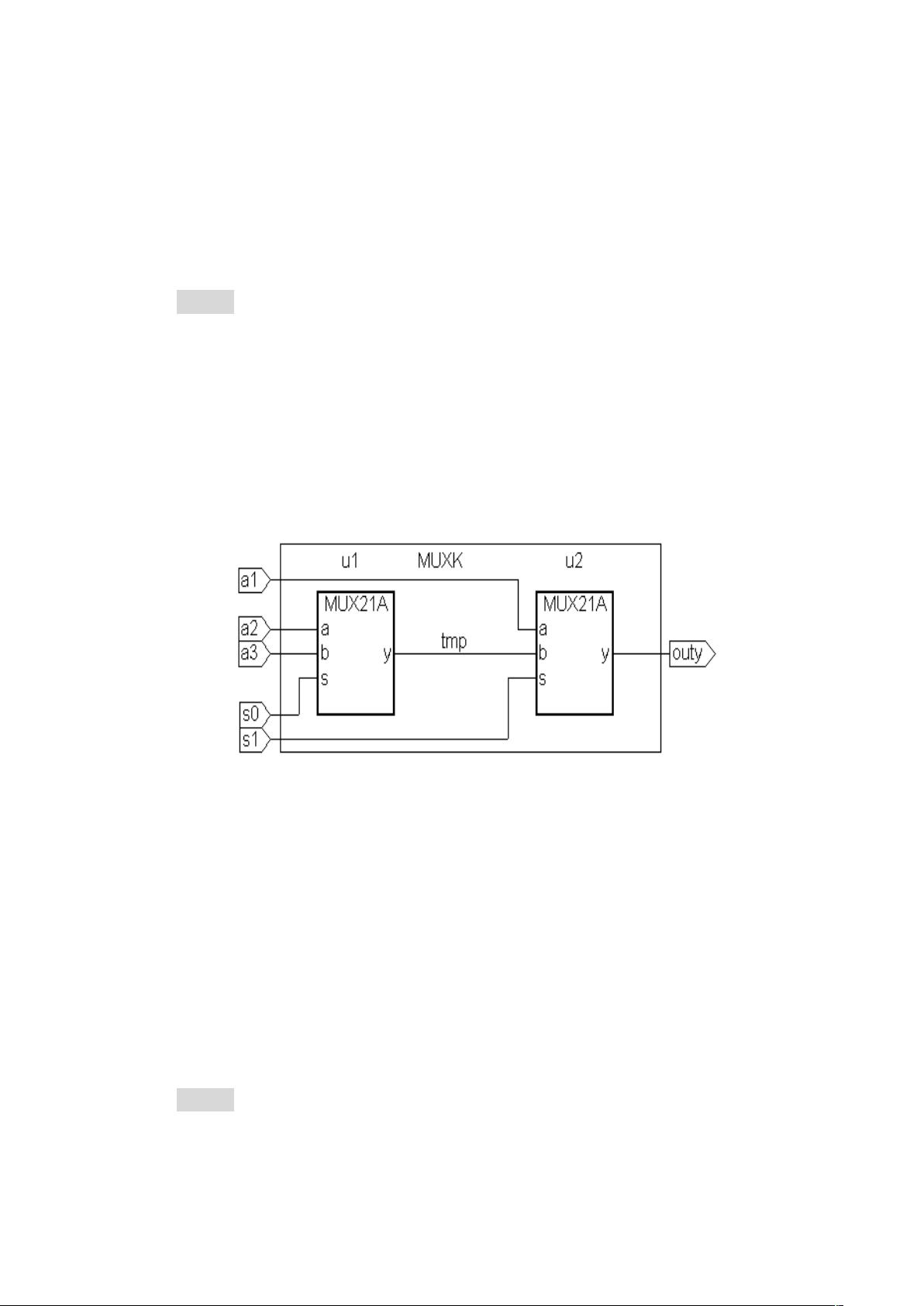

接着,实验要求将这个2选1多路选择器看作是一个名为MUX21A的独立元件,并使用元件例化语句将其嵌入到更大的电路设计中。图1展示了双2选1多路选择器的示意图,它包含两个独立的MUX21A实例u1和u2,它们通过输入a1、a2、a3和临时信号tmp进行连接。

在程序实现部分,给出了实体mux21a的定义,包括输入和输出端口的数据类型(这里为bit)。随后,描述了具体的引脚映射,如s0由键1控制,s1由键2控制,以及各时钟信号和扬声器的连接。

实验步骤包括:编写VHDL代码,进行文本编辑、编译、仿真,观察时序波形,确保电路功能正确;然后进行引脚锁定,将设计下载到目标器件EP1C3上,选择实验电路模式5;最后进行硬件测试,通过键操作验证不同选择条件下扬声器输出的不同音调。

这个实验不仅锻炼了学生的编程技能,还让他们理解了实际应用中多路选择器在音频处理中的作用,以及如何利用VHDL语言描述和实现硬件电路。通过这样的实践,学生能够加深对组合逻辑电路原理的理解,并提升其在电子设计自动化(EDA)工具中的应用能力。

2020-07-15 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2013-04-24 上传

2020-07-15 上传

uangfeineng53

- 粉丝: 1

- 资源: 20

最新资源

- iphone application progamming guide

- java笔试题(英文版有答案与讲解)

- 01_进销存管理系统

- 软件项目开发计划书样例.doc下载

- ORACLE 数据库WEB 控制台命令

- C/C++嵌入式编程

- ObjectARX开发实例教程-20070715.pdf

- Windows平台OracleRAC构建.

- MapXtreme2005 开发手册

- IBM AIX 虚拟IO服务器实现MPIO案例分析

- Oracle_RAC_For_Window

- GB-T 20158-2006 信息技术 软件生存周期过程 配置管理

- Ansi C standard

- 《ARM应用系统开发详解——基于S3C4510B的系统设计(第二版)》

- easyarm1138

- 数据库第四版答案数据库第四版答案