VHDL并行语句详解:潘松《EDA技术与VHDL第四版》第5章

需积分: 9 102 浏览量

更新于2024-07-24

1

收藏 530KB PDF 举报

"EDA技术与VHDL第四版课件,潘松——第5章 VHDL并行语句,深入讲解了VHDL中的并行信号赋值语句及其相关概念,包括简单信号赋值、条件赋值、选择赋值、块语句、元件例化、全加器设计实例、生成语句、GENERIC参数传递、数据类型定义以及信号属性和运算操作符等。"

在VHDL中,并行信号赋值语句是设计数字系统的关键部分,它们允许同时对多个信号进行操作,以实现硬件级别的并行处理。本章节详细介绍了以下几个知识点:

1. **简单信号赋值语句**:这是最基本的信号赋值方式,如`signal_name <= value;`,用于即时更新信号值。

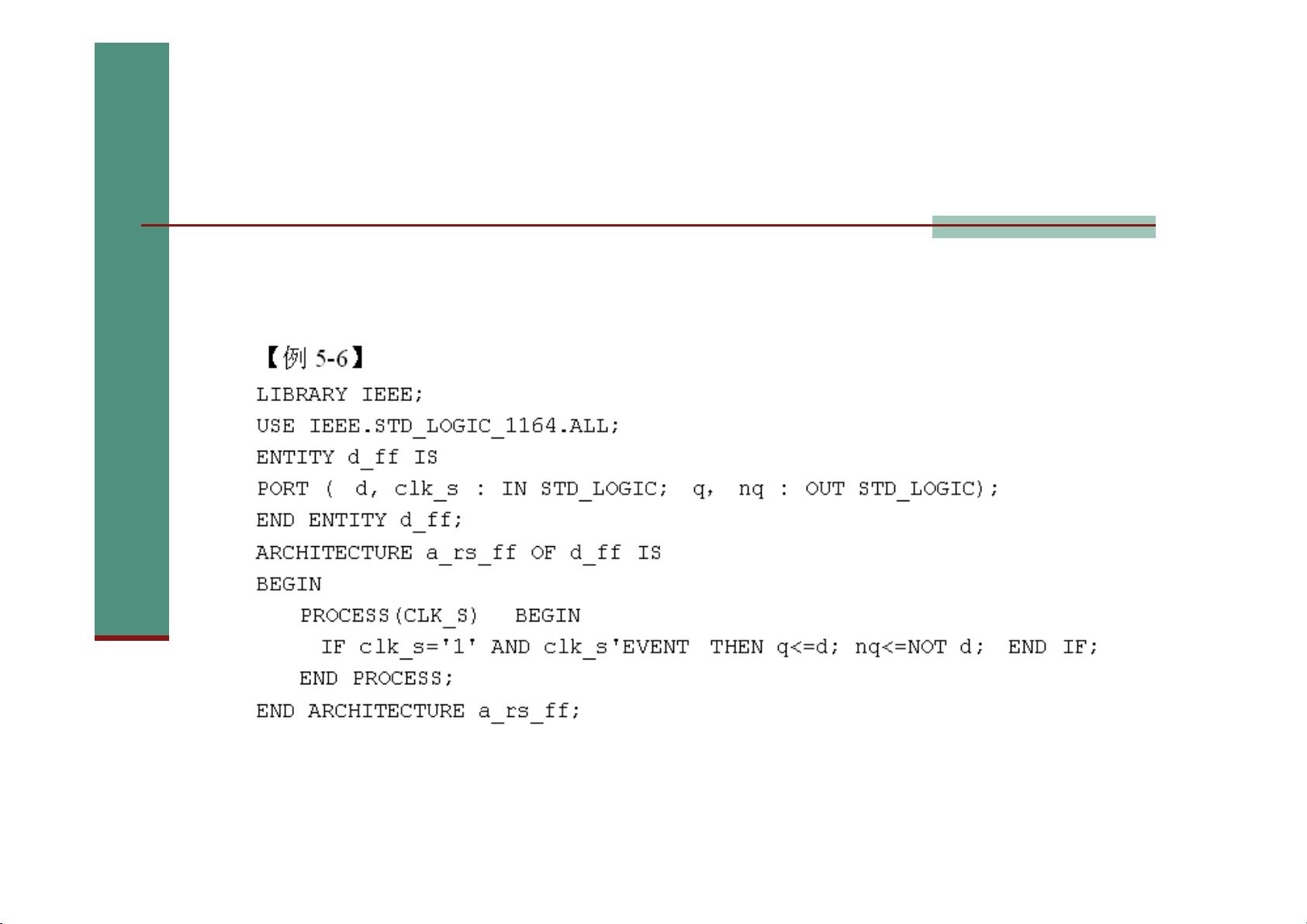

2. **条件信号赋值语句**:通过`if-else`结构,依据特定条件对信号进行赋值,例如`if condition then signal_name <= value1; else signal_name <= value2; end if;`。

3. **选择信号赋值语句**:利用`case`语句根据不同情况赋值,类似于C语言的switch语句,如`case expression is when ...`.

4. **块语句**:通过`begin-end`块将一组语句组合在一起,可以包含条件、选择赋值以及顺序执行的语句。

5. **元件例化语句**:用于实例化已定义的组件或IP核,将设计的模块实例化到设计中,如`component_name instance_name (port_map(...));`.

6. **全加器设计与例化语句应用**:展示了如何使用VHDL设计全加器并进行实例化,说明了硬件描述语言在实际电路设计中的应用。

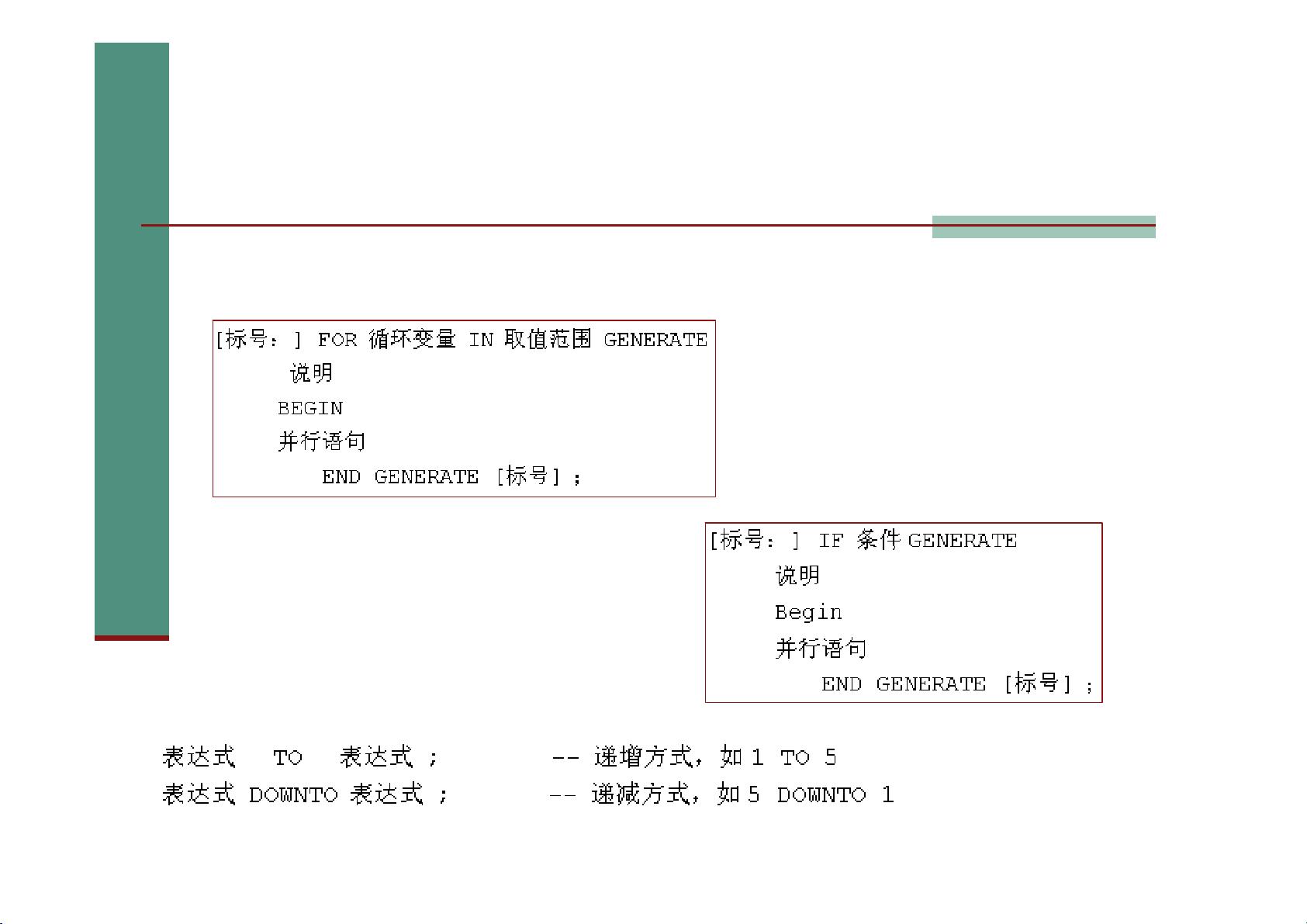

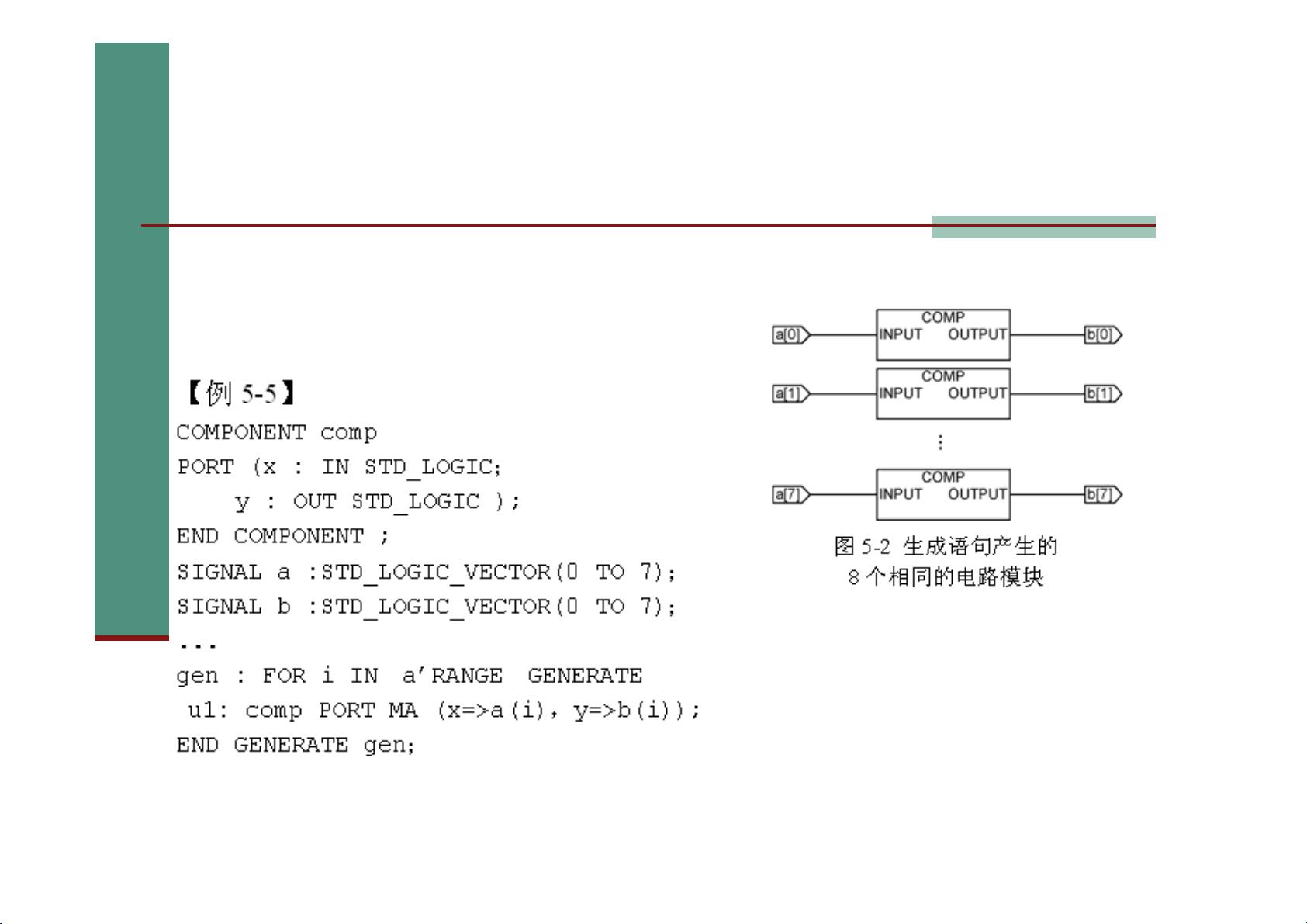

7. **生成语句**:`generate`语句用于根据参数或条件生成重复的结构,实现代码复用,例如`for genvar loop generate ... end generate;`.

8. **GENERIC参数传递映射语句**:在组件例化时,通过GENERIC关键字定义和传递参数,以适应不同的配置需求。

9. **数据类型定义语句**:涵盖限定性数组、非限定性数组、枚举型以及枚举型子类型,提供了丰富的自定义数据类型,增强了代码的可读性和可维护性。

10. **VHDL的存储器描述**:介绍如何使用VHDL描述存储器结构,如RAM、ROM等。

11. **信号属性及属性函数**:包括信号类属性(如‘READY’、‘STABLE’等)、数据区间类属性(如‘HIRESOLUTION’、‘LOWRESOLUTION’)和数值类属性(如‘VALUE’),这些属性提供了访问信号状态和行为的方法。

12. **VHDL运算操作符**:涵盖了逻辑操作符(如AND、OR、NOT)、关系操作符(如=、/=、<、>、<=、>=)、算术操作符(+、-、*、/、MOD)、符号操作符(+、-、&等)以及重载操作符,用于定义特定操作的优先级和行为。

以上内容是VHDL并行语句的重点,对于理解和使用VHDL进行数字系统设计至关重要。通过学习这一章,读者将能够编写更复杂的VHDL代码,实现高效的硬件描述。

2009-11-11 上传

2021-01-07 上传

134 浏览量

2010-10-27 上传

2009-04-17 上传

点击了解资源详情

2012-05-17 上传

nc21lym

- 粉丝: 1

- 资源: 25

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常