Cyclone III FPGA实现DDR2接口的设计与分析

119 浏览量

更新于2024-08-30

收藏 266KB PDF 举报

本文主要探讨了基于Cyclone III FPGA的DDR2接口设计,分析了DDR2内存的工作原理以及在FPGA中的实现细节。

DDR2内存是DDR内存的升级版本,它通过在时钟的上升沿和下降沿同时传输数据,从而在相同时钟频率下实现了比SDRAM更高的数据传输速率。DDR2相比DDR,其预读取系统命令数据的能力翻倍,提高了内存性能。在DDR2内存的设计中,关键在于如何有效地利用FPGA的接口资源来实现高效的信号传输。

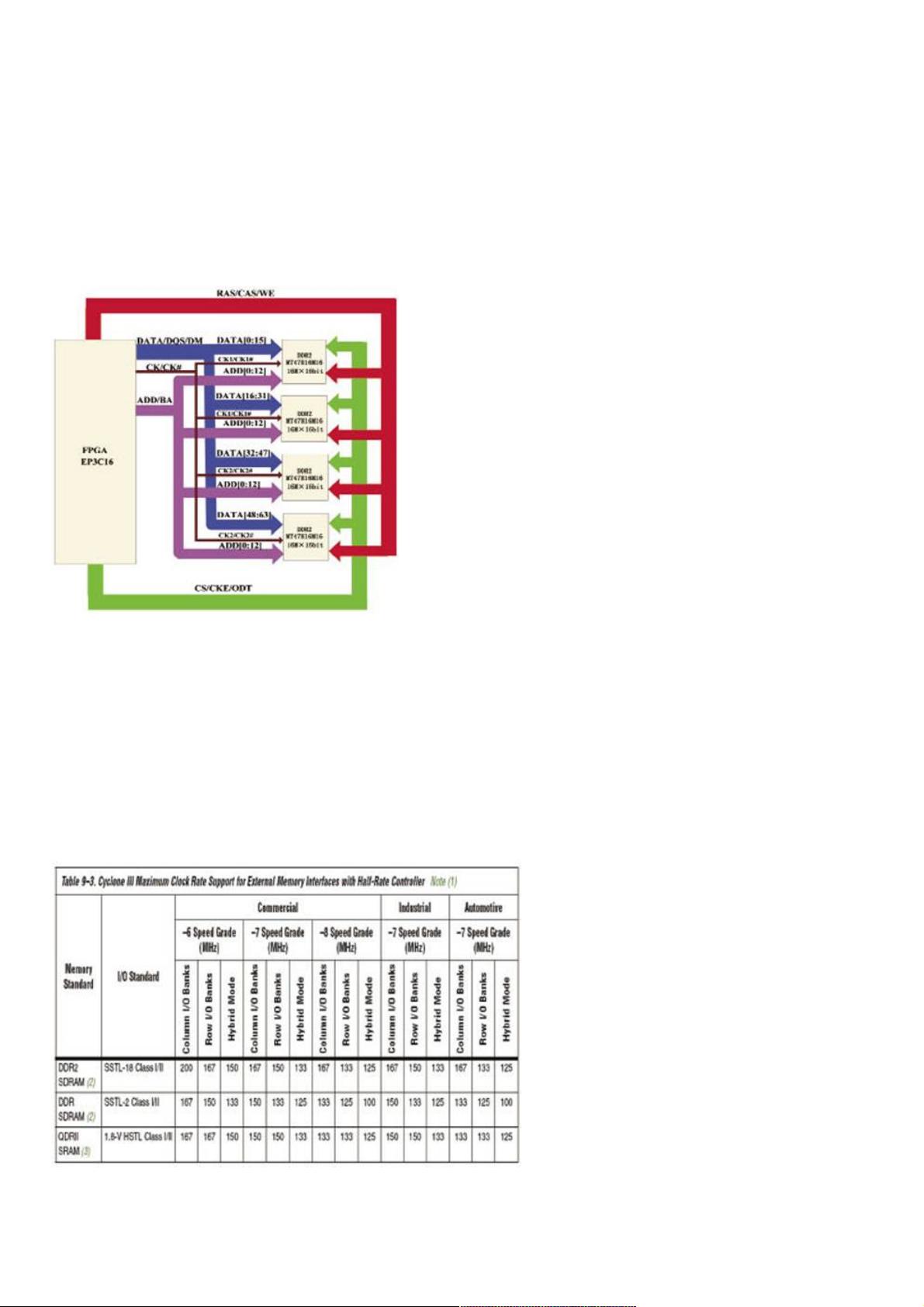

Altera公司的Cyclone III系列FPGA,如EP3C16F484C6N,被用于实现DDR2接口。需要注意的是,EP3C16F484C6N的TOP和BOTTOM边的BANK支持最高200MHz的DDR2接口,DQS、DQ和DM信号需要专用的FPGA管脚。根据表1,6系列的Cyclone III FPGA的Top和Bottom BANK是唯一支持200MHz DDR2频率的。因此,为了满足设计需求,通常会将4片DDR2内存分别连接到FPGA的这些BANK上。

表2显示了FPGA的DQS和DQ组的配置情况,DQs作为采样信号,与一组DQs一起工作,构成一个采样单元。例如,×8 Groups意味着每组有8个DQ,配有一个DQS。FPGA的每一侧都有两个Bank,每个Bank可以支持两个这样的DQS和DQ组。这种布局有助于优化信号路径,确保数据的准确传输。

在具体实施时,设计者必须考虑FPGA的管脚限制,尤其是在DQS和DQ的布局上。图2的DQS和DQ组分配图提供了更直观的参考,帮助理解如何在硬件层面连接DDR2内存和FPGA。在实际设计中,还需要考虑信号完整性、时序约束以及电源管理等方面,以确保整个系统的稳定运行和高性能。

基于Cyclone III FPGA的DDR2接口设计是一项复杂而细致的任务,需要深入理解DDR2内存的工作机制,熟悉FPGA的内部结构,并能有效地规划和利用FPGA的资源。通过合理的接口设计,能够充分利用DDR2内存的高速特性,提升系统性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-03-07 上传

2021-02-14 上传

2020-05-08 上传

2008-11-12 上传

2013-01-05 上传

2012-10-07 上传

weixin_38581777

- 粉丝: 4

- 资源: 917