UM10503 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 1.6 — 25 January 2013 17 of 1316

NXP Semiconductors

UM10503

Chapter 2: LPC43xx ARM Cortex-M0 co-processor and Inter- Process

It is the responsibility of the process writing to a queue making sure that the queue is not

filled completely; before loading a new item the process should confirm that the write

pointer will not be equal to, or overtake the read pointer and will leave at least one free

space. On the other hand the receiving side shall promptly process and remove items

from the queue.

No explicit error handling is performed. It is assumed that the ARM Cortex-M0 will always

respond to a ARM Cortex-M4 command.

2.5.2 Protocol

The ARM Cortex-M0 is used a co-processor to off-load the ARM Cortex-M4 and to

perform serial IO tasks. The ARM Cortex-M4 should be able to initialize tasks executed on

the ARM Cortex-M0. The ARM Cortex-M0 should be able to signal to the ARM Cortex-M4

when these tasks have completed or failed. This is done by issuing commands from ARM

Cortex-M4 to ARM Cortex-M0, where the ARM Cortex-M0 responds with messages. This

command and message interface resembles a hardware register level interface with

command and status registers.

The ARM Cortex-M4 issues 32-bit commands to the ARM Cortex-M0. Each command

starts with a 16-bit ID that defines which task is referred to. The LSBit indicates the

command type. A Write command is followed by a 32-bit operand. When a new command

is available, the ARM Cortex-M4 signals this to the ARM Cortex-M0 by raising an

interrupt.

The ARM Cortex-M0 return 32-bit messages to the ARM Cortex-M4. A messages starts

with a 16-bit ID that indicates which tasks the message refers to. The LSByte indicates the

message type. A Read response message is followed by the 32-bit read operand. When a

new message is available, the ARM Cortex-M0 signals this to the ARM Cortex-M4 by

raising an interrupt.

Small data transfers can be performed by the single 32-bit data read, CMD_RD_ID, and

write, CMD_WR_ID, commands. These commands use a 3-Byte addressing scheme to

support an argument space of 212 = 4096 32-bit words. Large data transfers can be more

efficiently handled using pointers.

Also higher level interfaces using API calls will typically use indirect, pointer based, reads

and writes.

When multiple tasks are running concurrently the ID is used to distinguish commands and

messages belonging to a certain task. A global command parser should be used to the

kick off commands to the tasks running on the ARM Cortex-M0.

The same holds true for the ARM Cortex-M4 side, a global message parser channels

back messages to the task dispatchers running on the ARM Cortex-M4 side.

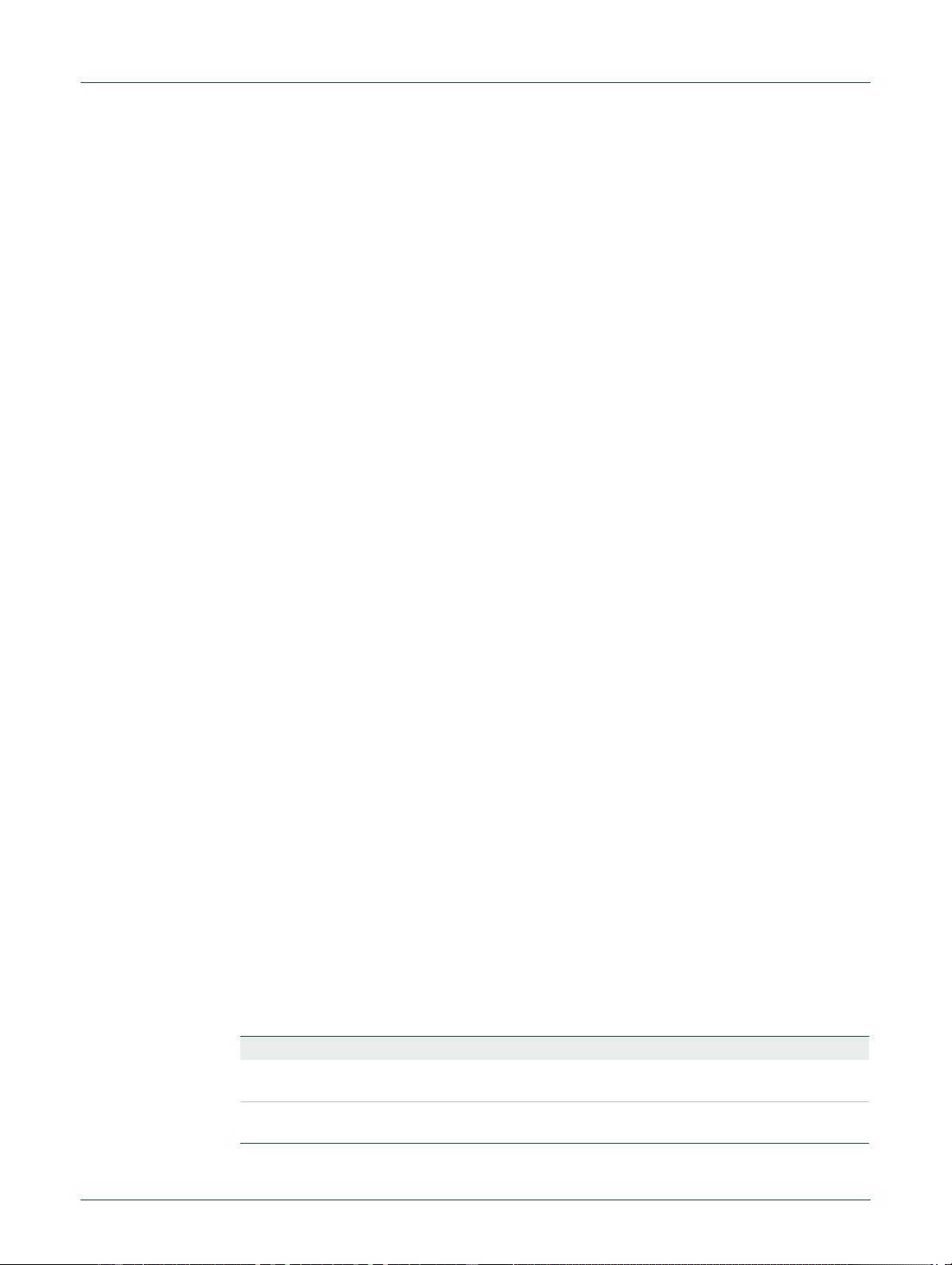

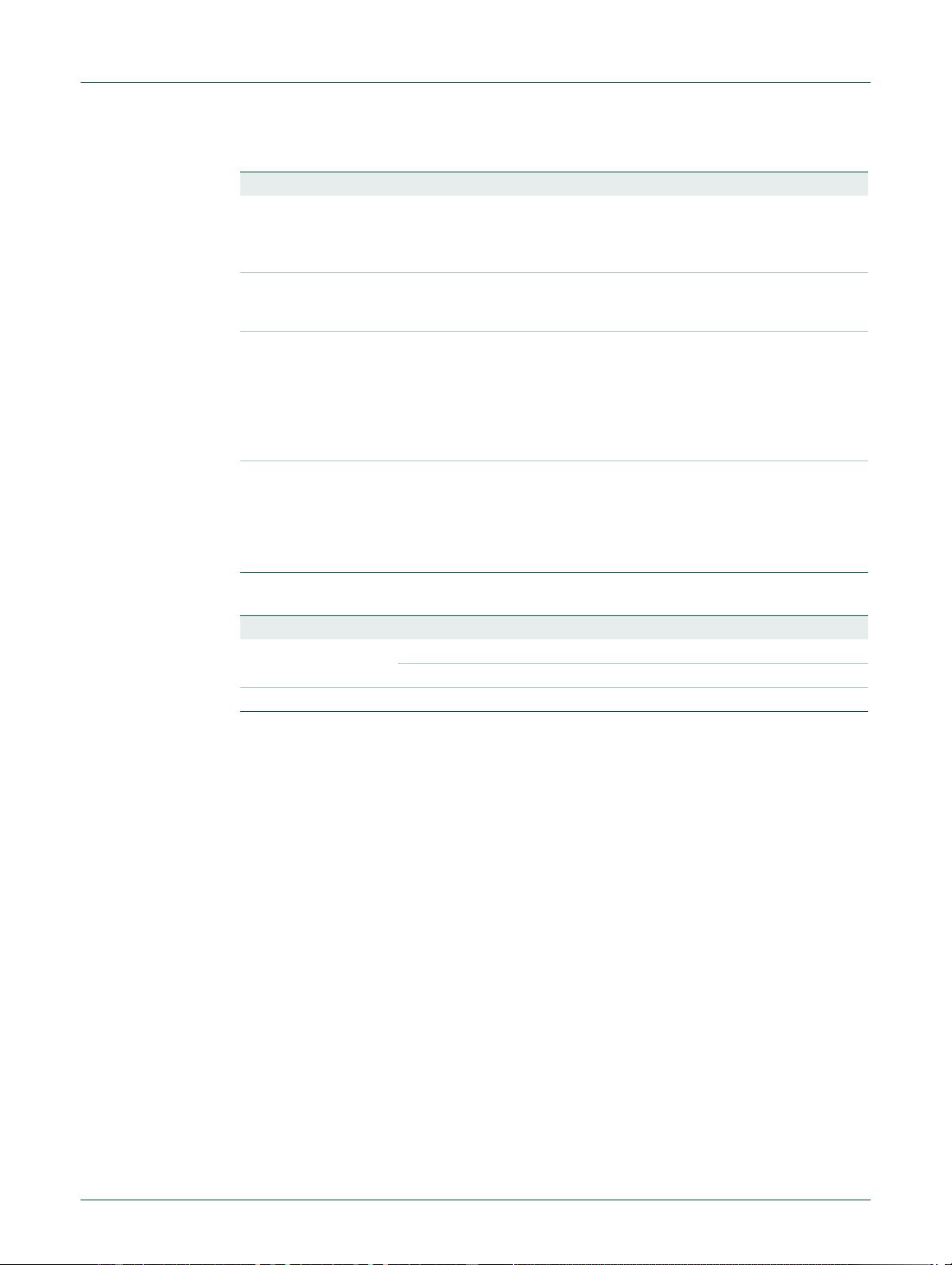

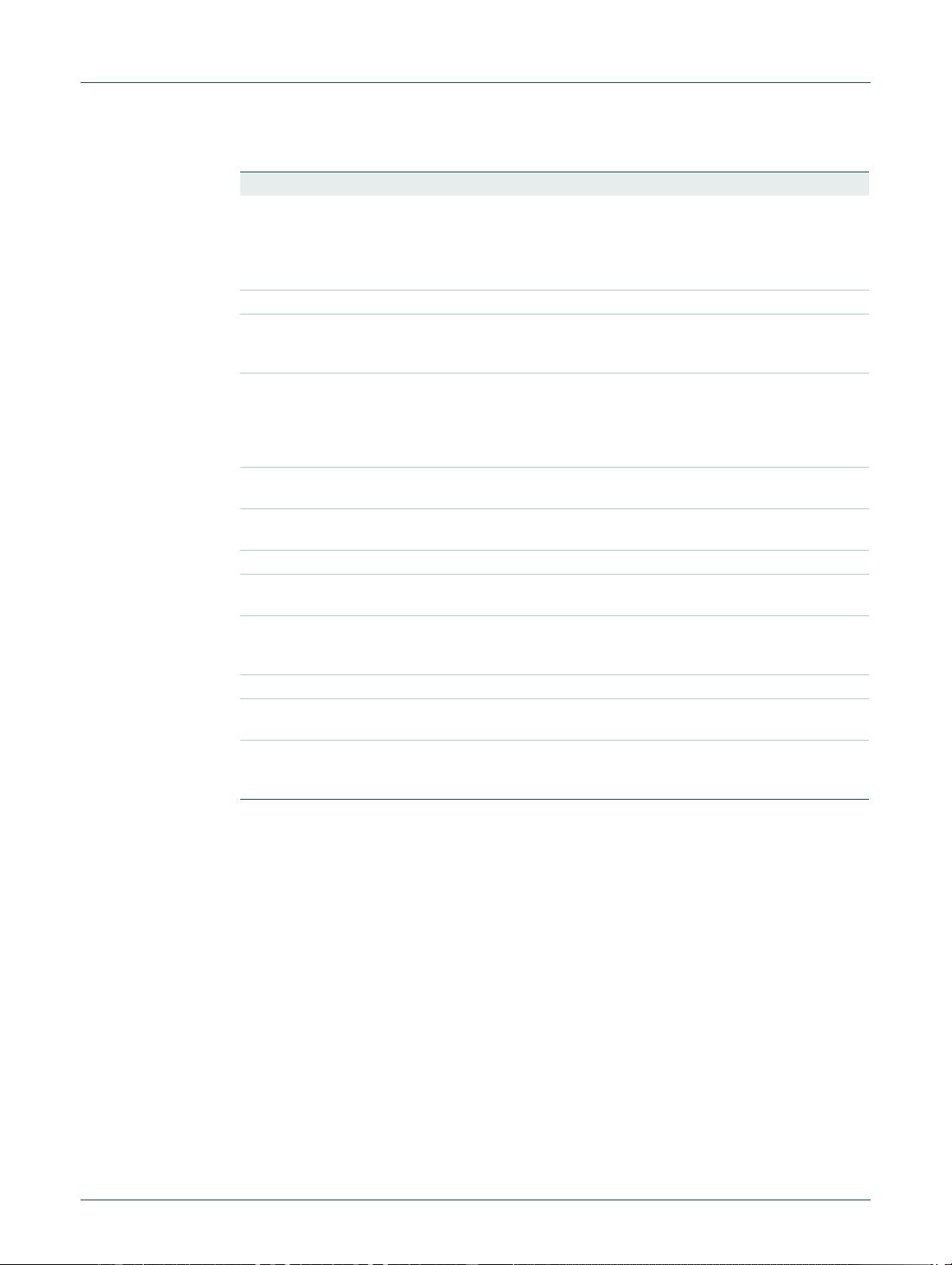

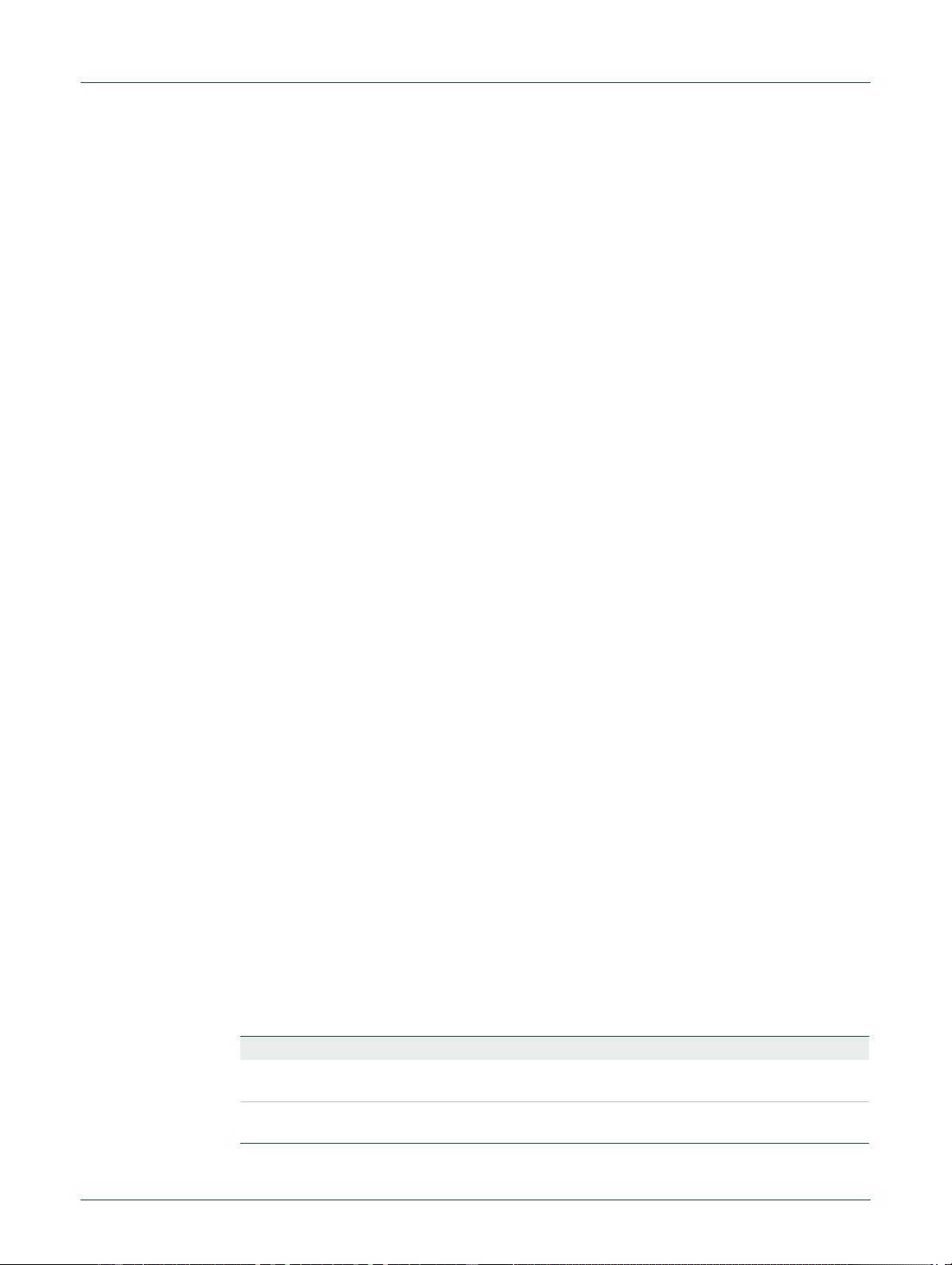

Table 5. Command list

Command Bit mask Description

CMD_RD_ID 0xTTTT.PPP0 read 32 bit WORD with argument ID=0xPPP

from the task with ID = 0xTTTT

CMD_WR_ID 0xTTTT.PPP1, WORD write 32 bit WORD with argument ID=0xPPP to

the task with ID = 0xTTTT