Vivado HLS在FPGA硬件设计中的效能评估

版权申诉

107 浏览量

更新于2024-06-27

收藏 1018KB DOCX 举报

"基于Vivado HLS的硬件设计效能评估"

本文主要探讨了使用Xilinx的Vivado HLS(High-Level Synthesis)工具在FPGA(Field-Programmable Gate Array)芯片设计中的性能表现。Vivado HLS是一款高层次综合工具,它允许开发者使用高级语言如C++来实现硬件设计,从而简化了传统的硬件描述语言(如Verilog或VHDL)的设计流程。

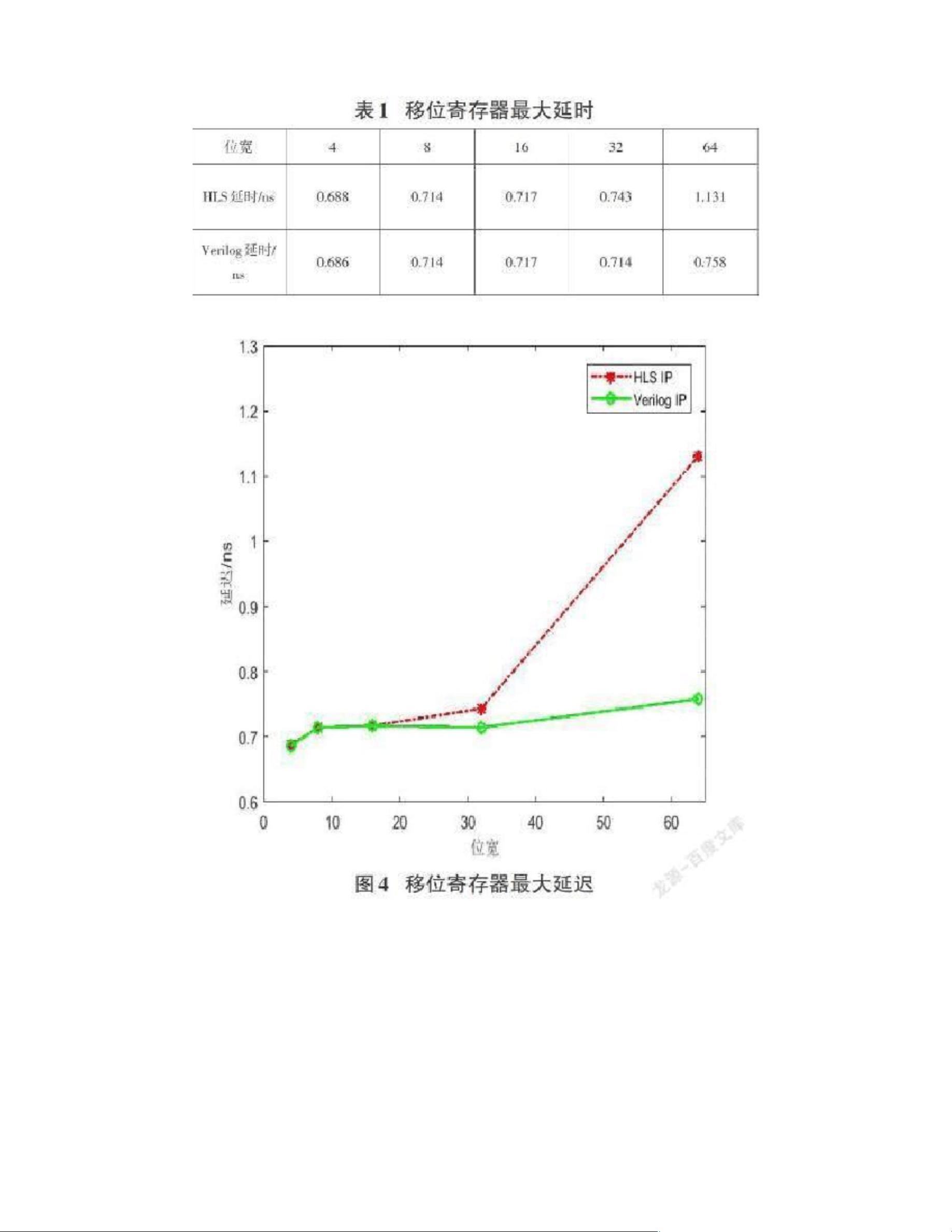

在研究中,作者通过设计移位寄存器并分别用C++语言和Verilog语言实现,来对比Vivado HLS工具在硬件电路设计中的效率和功能。他们通过比较不同输出位宽下两种设计方法的时序、功耗、面积(PDP,即Performance, Power, and Delay Product)以及资源利用率来评估Vivado HLS的优势和局限性。

实验结果显示,虽然Vivado HLS工具综合出的Verilog代码在性能上可能不如手工编写的Verilog代码,但其高阶语言输入的优势在于,开发者无需深入掌握硬件描述语言,也能利用FPGA加速算法的执行。这种方法降低了硬件设计的门槛,使得软件工程师可以更方便地参与到硬件设计中,提升了设计的效率。

此外,Vivado HLS支持的功能还包括代码优化,它可以自动调整设计以提高速度、降低功耗或减少资源使用。这在现代FPGA设计中是至关重要的,因为资源的有效利用直接影响到系统的整体性能和能效。

总结来说,Vivado HLS为FPGA设计提供了一种高效且用户友好的方法,尽管它可能在某些方面略逊于直接编写硬件描述语言,但其高层面的语言接口和自动优化能力为设计者提供了更大的灵活性和便利性。对于那些希望快速实现原型验证或者不熟悉硬件描述语言的开发团队来说,Vivado HLS是一个极具价值的工具。然而,为了达到最佳性能,开发者仍需要理解FPGA的工作原理,并能够适当地调整和优化HLS生成的硬件代码。

187 浏览量

232 浏览量

257 浏览量

171 浏览量

2024-08-21 上传

169 浏览量

312 浏览量

xxpr_ybgg

- 粉丝: 6836

最新资源

- Tailwind CSS多列实用插件:无需配置的快速多列布局解决方案

- C#与SQL打造高效学生成绩管理解决方案

- WPF中绘制非动态箭头线的代码实现

- asmCrashReport:为MinGW 32和macOS构建实现堆栈跟踪捕获

- 掌握Google发布商代码(GPT):实用代码示例解析

- 实现Zsh语法高亮功能,媲美Fishshell体验

- HDDREG最终版:DOS启动修复硬盘坏道利器

- 提升Android WebView性能:集成TBS X5内核应对H5活动界面问题

- VB银行代扣代发系统源码及毕设资源包

- Svelte 3结合POI和Prettier打造高效Web开发起动器

- Windows 7下VS2008试用版升级至正式版的补丁程序

- 51单片机交通灯系统完整设计资料

- 兼容各大浏览器的jquery弹出登录窗口插件

- 探索CCD总线:CCDBusTransceiver开发板不依赖CDP68HC68S1芯片

- Linux下的VimdiffGit合并工具改进版

- 详解SHA1数字签名算法的实现过程