Quartus II与GW48 SOPC系统实验教程

需积分: 1 123 浏览量

更新于2024-07-26

收藏 1.45MB DOC 举报

"该资源是一份关于SOPC(系统级可编程芯片)和EDA(电子设计自动化)的实验指导书,主要针对Quartus II软件的使用、GW48 SOPC系统(GW48-PK2)的操作以及Verilog HDL在数字电路设计中的应用。内容包括Quartus II的设计流程、设计输入方法、编译过程、仿真和编程下载,以及一系列基于Verilog HDL的数字电路实验,如多路选择器、加法器、移位寄存器、乘法器、计数器、分频器和控制系统的设计。"

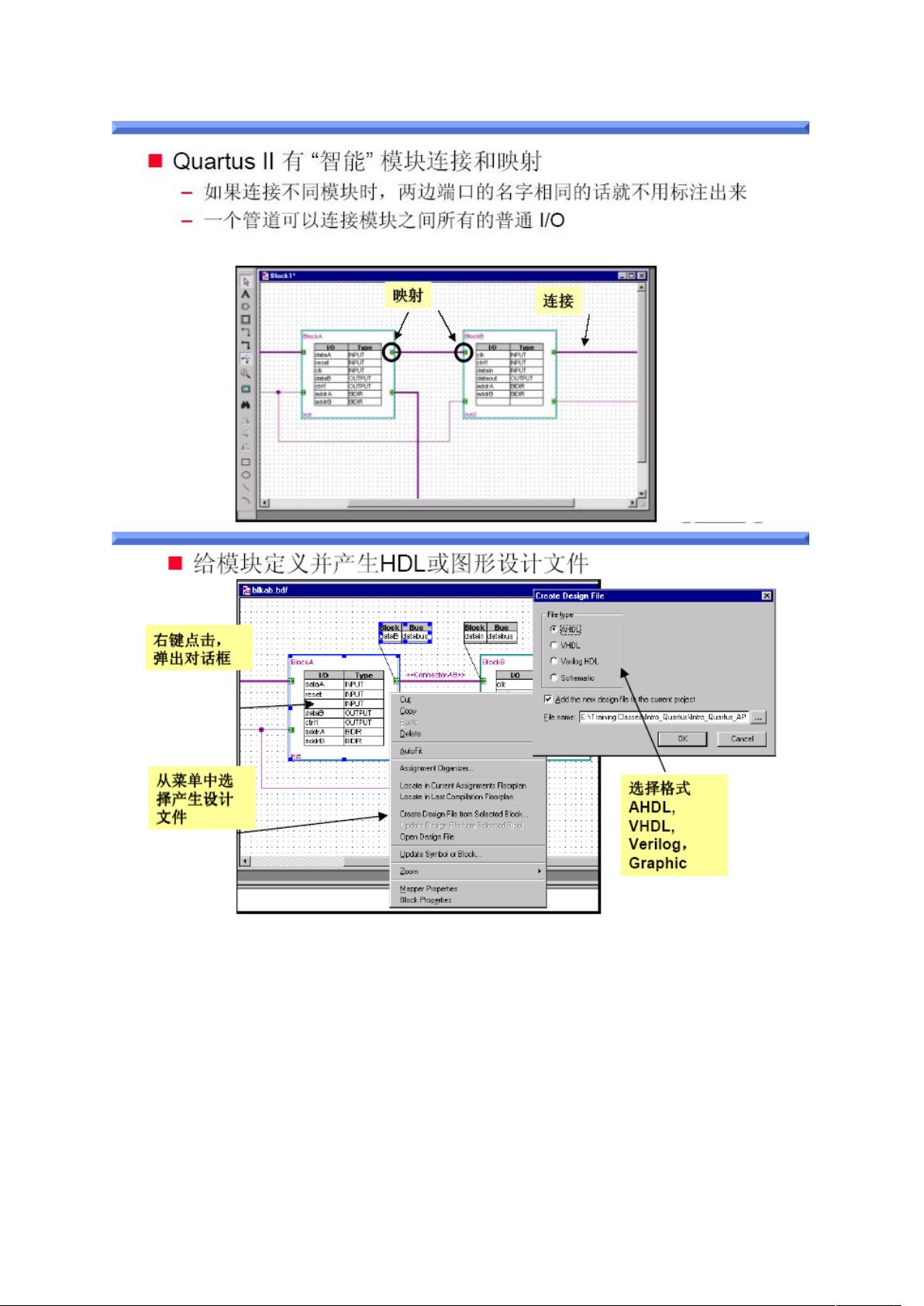

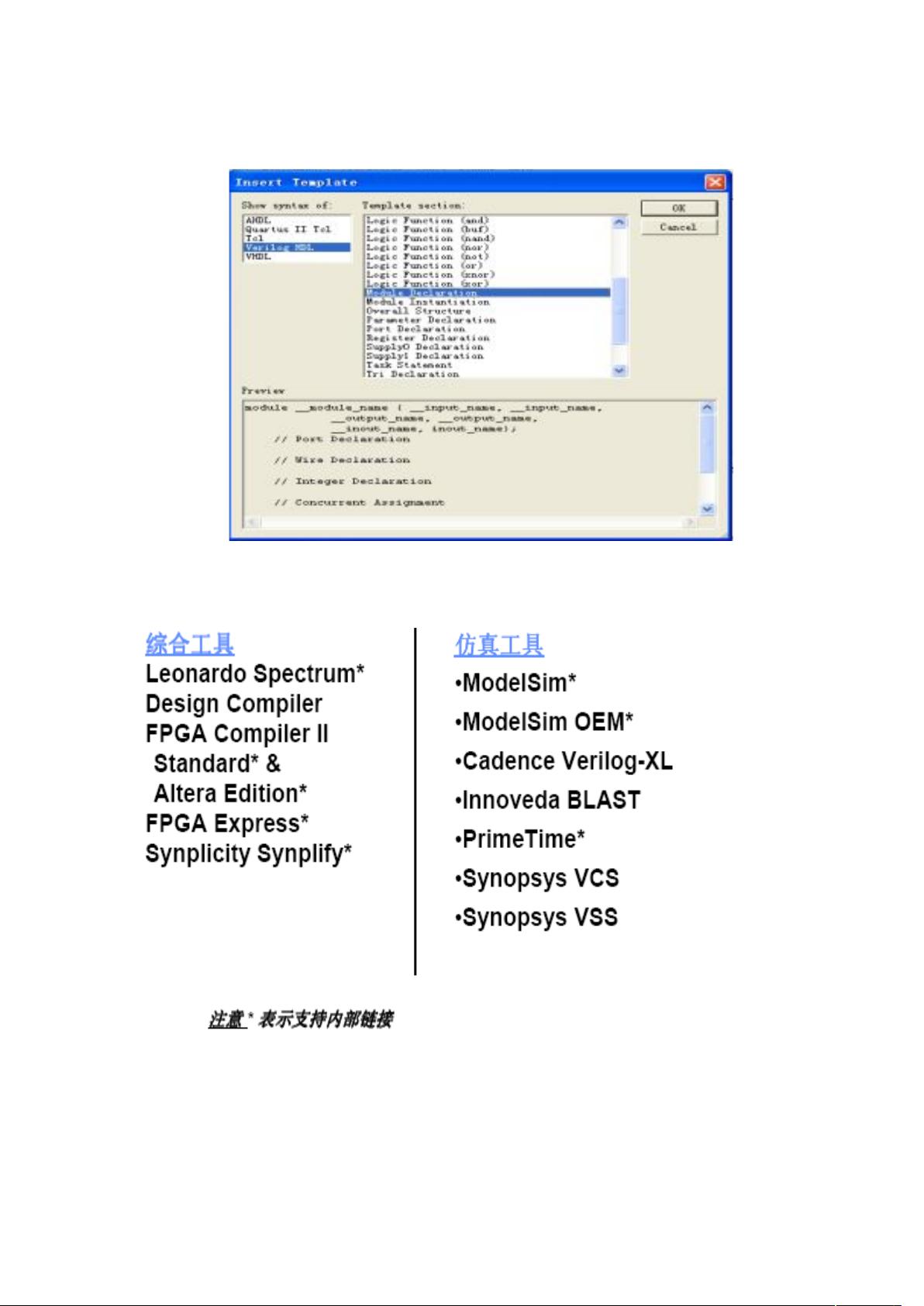

在这份实验指导书中,首先介绍了Quartus II,这是一个广泛使用的FPGA(现场可编程门阵列)设计工具。基于Quartus II的设计过程包括建立项目、图形和文本输入、第三方工具的集成,以及编译、引脚锁定、延迟分析、仿真和编程下载等环节。在设计输入部分,提到了原理图输入、文本编辑(如Verilog HDL)以及内存和第三方工具输入等多种方法,这些方法可以满足不同复杂度和需求的设计。

Quartus II的编译阶段,需要指定目标器件,锁定引脚分配,然后进行编译,生成编译报告以便于分析设计性能。延迟分析是评估设计速度的关键步骤,而仿真则用于验证设计的功能正确性。最后,编程下载将设计的配置数据加载到FPGA中,实现硬件功能。

GW48 SOPC系统是一个教学实验平台,用于实践SOPC和DSP(Digital Signal Processing)实验。文档详细介绍了GW48系统的使用注意事项、主板结构和实验电路的结构图,为使用者提供了清晰的操作指南。

在Verilog HDL设计数字电路部分,包含了多个基础到进阶的实验,如4选1多路选择器、8位加法器、8位移位寄存器、移位相加乘法器、模加/减计数器、六分频器和交通灯控制系统、A/D采样控制电路等,旨在帮助学习者通过实际操作掌握数字逻辑设计的基本原理和方法。

这份指导书对于学习FPGA设计和SOPC系统的初学者来说是非常有价值的资源,它不仅覆盖了理论知识,还提供了丰富的实践操作步骤,有助于提升读者在EDA领域的技能和理解。

233 浏览量

179 浏览量

2009-06-03 上传

268 浏览量

122 浏览量

2022-06-20 上传

114 浏览量

snails_ya

- 粉丝: 0

- 资源: 1

最新资源

- 团队任务:introsort && shakesort

- fsdownload.rar

- Geerooniimoo.io

- full_MEAN_ministore

- project-library

- 曼德尔卡洛

- C语言及数据结构课程设计:超市信息管理系统.zip

- PepperTab-crx插件

- O-HARA_SNS

- 易语言数组剖析-易语言

- archetype-catalog.zip

- RNToDoAppFirebase:有多个列表和选项的待办事项

- holbertonschool-low_level_programming

- 磊科nw336无线网卡驱动 1085.2 中文版

- aesthetic-portfolio

- 遍历窗口控件判断内容被改变-易语言