STM32G070内存对齐问题:从HardFault异常到解决方案

需积分: 5 10 浏览量

更新于2024-08-03

收藏 674KB PDF 举报

"本文档是应用笔记LAT1185,主要讨论了一个在使用STM32G070微控制器时遇到的HardFault异常问题,该问题与内存地址对齐有关。在KEIL MDK环境下,当编译优化级别设置为Level0时,程序会触发HardFault异常,而切换到Level1时程序则能正常运行。文档深入分析了问题的原因,并提供了相应的解决方案。"

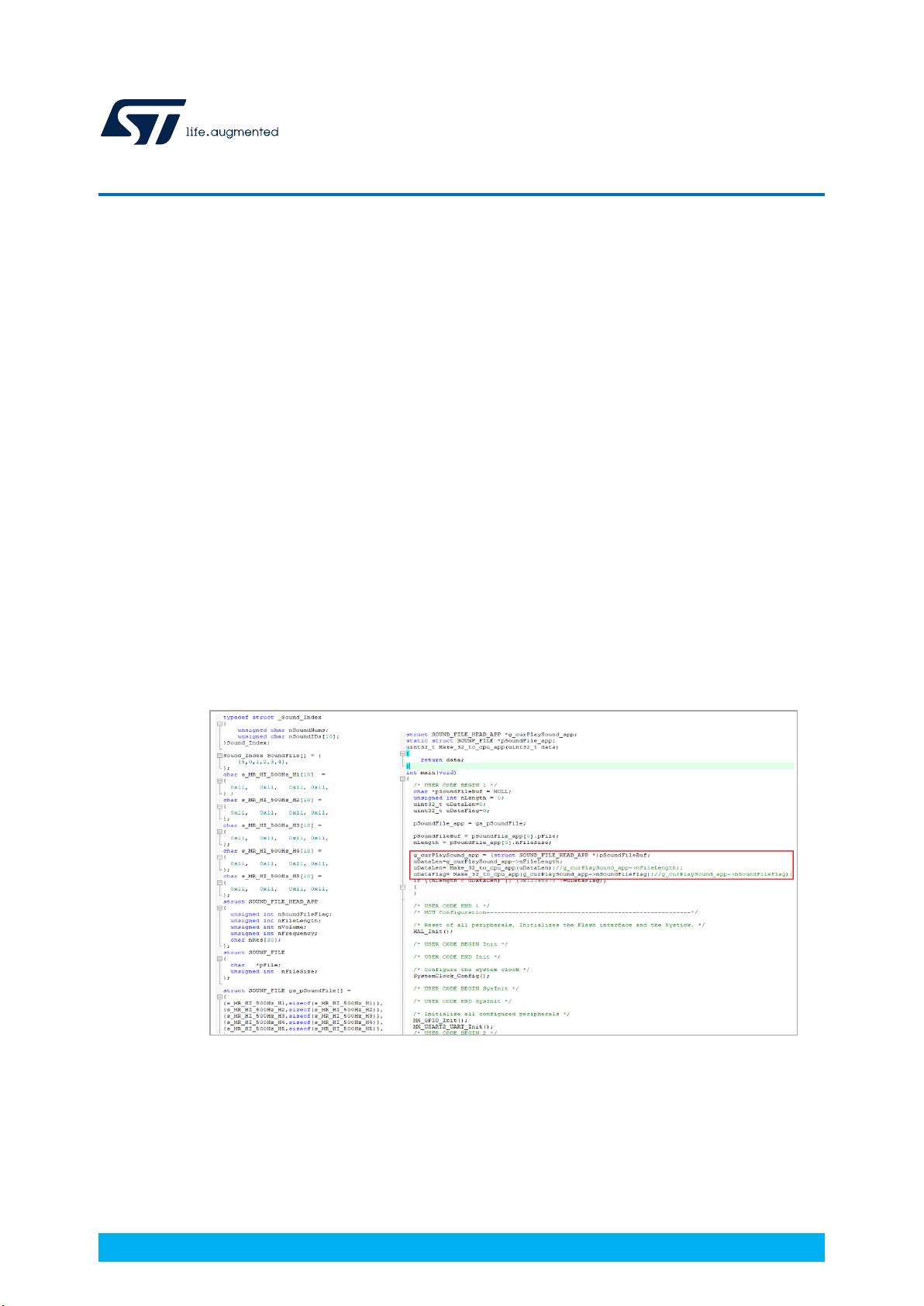

在STM32G070的开发过程中,有时会遇到一个看似与编译工具KEIL MDK相关的HardFault异常。客户报告称,当使用Level0优化级别时,程序会出错,但改为Level1时则运行良好。然而,经过分析,问题的根本原因并非KEIL MDK的bug,而是内存访问时的地址对齐问题。

问题在于,客户在代码中定义了一些全局数组,当尝试访问这些数组时,触发了HardFault异常。通过使用KEIL的调试器进行汇编级调试,发现在LDR指令执行时出现了问题。LDR指令用于从内存中加载一个WORD数据到指定寄存器,要求内存地址必须是4字节的倍数,即4字节对齐。如果地址未对齐,就会引发HardFault异常。

在出现问题的代码段中,LDR指令试图从非4字节对齐的地址0x2000000F加载数据,而当编译优化级别设置为Level1时,生成的代码访问的是4字节对齐的地址0x20000000,因此程序可以正常运行。

为了解决这一问题,开发者需要确保所有涉及内存访问的地方,特别是涉及到LDR指令的,其地址都是4字节对齐的。这可能意味着要重新组织数据结构,或者在访问特定内存区域之前进行适当的调整。在某些情况下,编译器可能会自动处理对齐问题,但为了确保兼容性和避免类似故障,程序员应明确理解并控制内存对齐。

在编写和调试STM32代码时,理解处理器架构的特性,如Cortex-M0的内存访问规则,至关重要。此外,适当设置编译器优化级别也可以帮助暴露潜在问题,因为不同的优化级别可能会影响代码生成的方式,使得某些问题在某些优化级别下显现出来。

地址对齐是嵌入式系统开发中的一个重要考虑因素,尤其是对于资源有限的微控制器。通过理解和遵循正确的对齐规则,可以避免不必要的硬件故障,提高代码的稳定性和效率。在遇到类似问题时,检查内存访问操作和编译器优化设置是排查问题的关键步骤。

点击了解资源详情

151 浏览量

点击了解资源详情

2024-03-21 上传

2024-03-15 上传

2024-03-15 上传

2024-04-02 上传

151 浏览量

2024-04-05 上传

冻结的鱼

- 粉丝: 2525

最新资源

- 项目管理词汇英汉对照索引:推动国内发展的关键工具

- Microsoft Visual C++ 6.0 MFC类库详解与配套资源

- ASP.NET中datalist的嵌套使用

- 安全清理C盘:优化硬盘空间的全面指南

- Eclipse中文入门:平台与基本操作详解

- 武大吉奥GeoSurf5.2:国产WebGIS平台,跨平台服务与开发利器

- RK2706 USB设备升级教程

- WebGIS入门与发展趋势:互联网驱动的GIS普及

- ARM 编程技巧:编译器优化和编程指南

- 802.11无线局域网组网与移动性分析

- 解决Windows多重引导故障全攻略

- Java编程规范与最佳实践

- 硬盘安装Linux:步骤详解与分区指南

- 萨师煊版《数据库系统概论》习题解析

- PC汇编语言入门:32位汇编基础

- SAP R/3系统详解:企业全面管理解决方案