数字集成电路中的互连线设计与影响分析

需积分: 9 192 浏览量

更新于2024-08-11

收藏 981KB PDF 举报

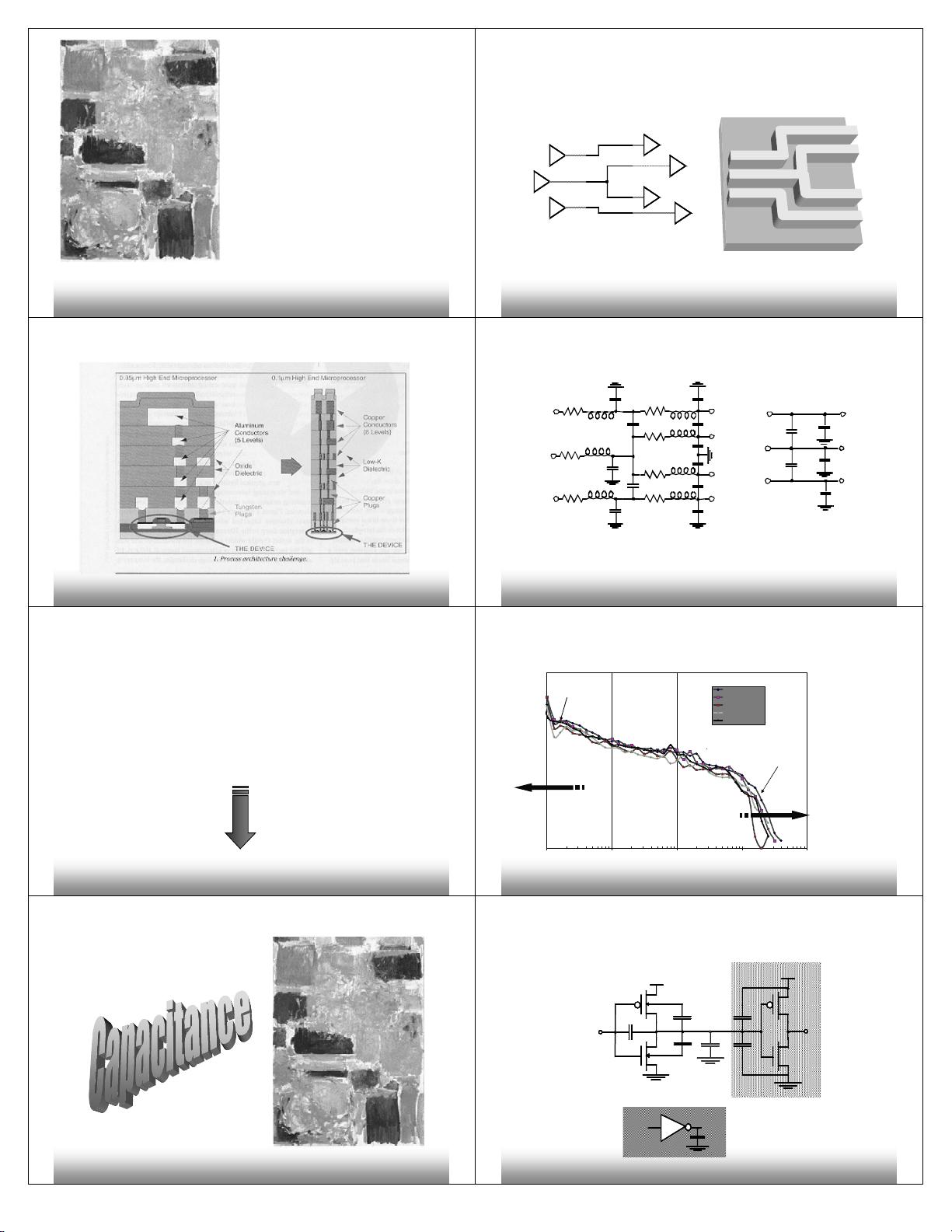

"本文档主要探讨了数字集成电路中的互连线设计,从设计的角度深入解析了互连线对芯片性能、可靠性和功耗的影响。内容涵盖了互连线的模型、寄生效应、电容概念以及不同材料的介电常数。"

在数字集成电路设计中,互连线起着至关重要的作用。它们负责在芯片上的各个元件之间传输信号,因此理解其工作原理和设计考虑是至关重要的。从设计角度透视数字集成电路,我们首先要了解互连线的基本构成和分类。互连线可以分为局部互连(Local Interconnect)和全局互联(Global Interconnect),其中局部互连通常在微小尺度上,而全局互联则跨越较大的距离,两者在技术要求和设计难度上有所不同。

互连线的设计不仅影响芯片的性能,还直接影响到系统的可靠性。随着集成电路的发展,互连线的数量呈指数级增长,例如从Pentium Pro到Pentium MMX再到后续的型号,互连线数量的增加表明了这一趋势。这带来了更复杂的互连寄生问题,如电容、电阻和电感等,这些寄生效应会降低信号传输的效率,增加功耗,并可能导致系统不稳定。

互连线模型是分析和优化设计的关键工具。所有包含模型(All-inclusive model)考虑了所有影响因素,而电容模型(Capacitance-only model)则专注于电容这一关键参数。电容是互连线中最重要的寄生效应之一,它会影响信号的上升时间、下降时间和扇出(Fanout)能力。当信号通过互连线时,电容会导致信号延迟并增加噪声。

电容的平板模型提供了一个直观的理解方式,其中介质(Dielectric)、衬底(Substrate)和线宽(W)、线长(L)以及厚度(tdi)是决定电容的关键因素。不同材料的介电常数(电容率)也至关重要,例如气凝胶、聚酰亚胺、二氧化硅、玻璃环氧、氮化硅和铝,甚至自由空间,它们决定了介质层的电学特性,从而影响互连线的性能。

数字集成电路的互连线设计是一项复杂而精细的任务,需要考虑诸多因素,如信号完整性和电源完整性,同时还要应对寄生效应带来的挑战。通过深入研究互连线的物理特性、模型和材料选择,设计师能够优化电路性能,提高系统可靠性,并降低功耗。

2021-05-21 上传

2021-05-21 上传

2008-07-24 上传

2023-11-24 上传

2023-07-30 上传

2023-03-26 上传

2023-05-27 上传

2024-11-07 上传

2023-04-23 上传

weixin_38655496

- 粉丝: 5

- 资源: 932

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新