Verilog子模块调用详解:ISE环境下的层次结构与实例

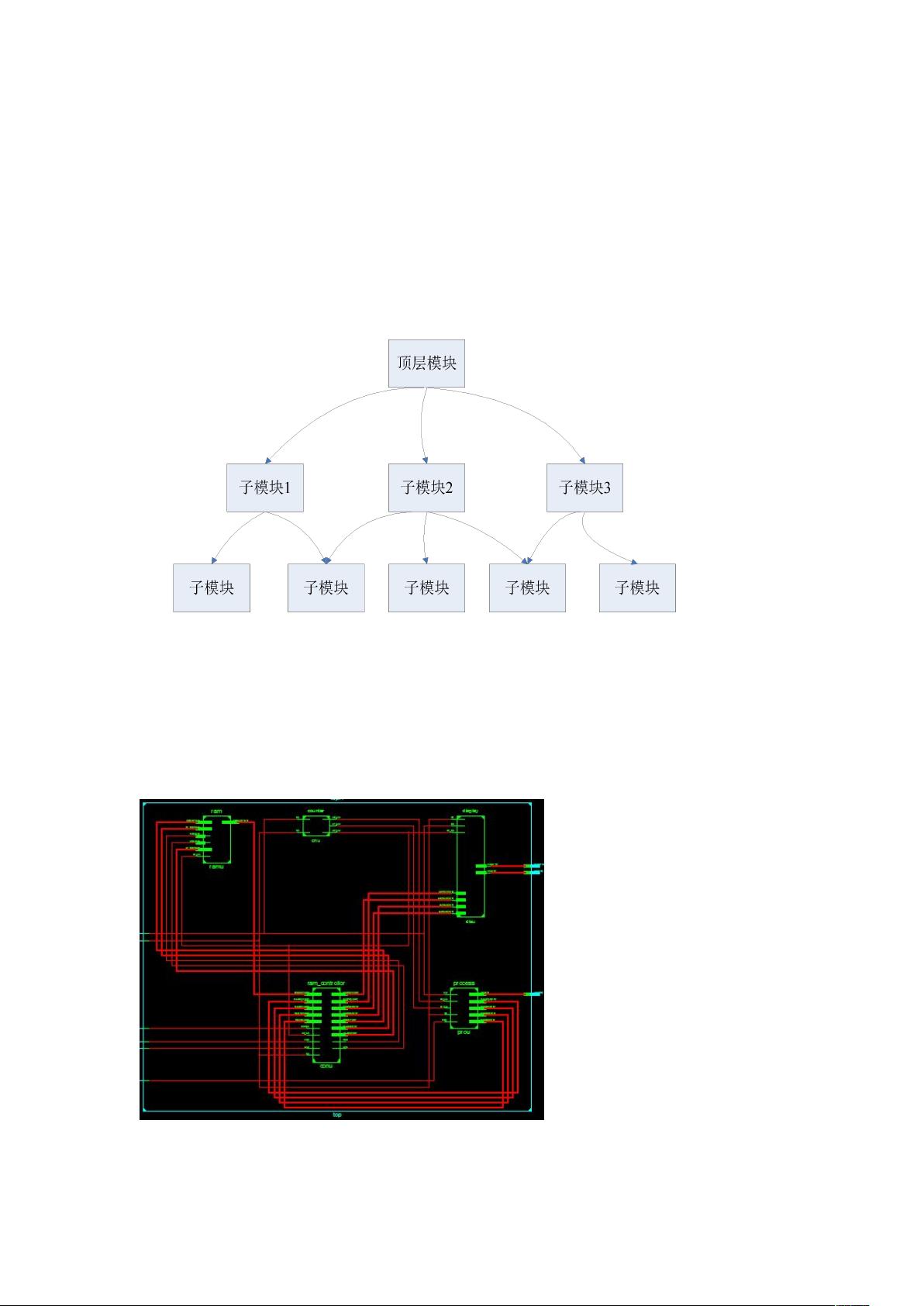

Verilog语言是一种硬件描述语言,用于设计和描述数字电路的行为。其模块化的设计思想类似于C语言中的函数调用,通过建立和调用子模块来增强代码的复用性和可维护性。在Verilog中,模块层次结构允许顶层模块调用多个子模块,子模块之间还可以嵌套,但通常不超过五级深度,以保持设计的清晰和效率。

在ISE开发环境中,创建模块层次结构的步骤如下:

1. 首先,创建一个新的工程,例如名为"top",并在其中建立一个顶层模块的Verilog文件,如"top.v"。文件名并不强制与工程名一致,但通常这样做有利于理解和管理。

2. 在这个工程下,创建子模块文件,比如"counter.v",编写具体的电路功能,如分频计数器。接着,为子模块创建Schematic Symbol,以便于理解和设计意图的可视化。

3. 在"counter.v"中,使用Instantiation Template(实例化模板)定义子模块的实例,并确保信号连接正确。信号分为两种类型:模块间的连接使用wire类型,外部信号与模块连接则用input/output类型,如果涉及外部输出信号,还需要定义为reg型以保持数据的连续性。

4. 将子模块实例复制到顶层模块"top.v"中,调整instance_name为自定义名称,并确保所有输入输出信号与顶层模块内的相应信号一一对应。这样,顶层模块负责管理子模块之间的交互,并完成最终电路的完整连接。

5. 综合设计后,会得到一个包含顶层模块调用子模块的完整电路图,这个电路图展示了如何通过Verilog模块的层次结构组织复杂的功能,提高设计的灵活性和可扩展性。

通过上述步骤,开发者可以在大型硬件设计项目中有效地组织代码,实现模块化的开发和测试,使得调试和维护更加容易。理解并熟练掌握Verilog子模块调用的方法,对于从事硬件设计或FPGA开发的工程师来说至关重要。

2021-03-06 上传

2021-10-12 上传

2024-10-26 上传

2020-08-03 上传

2021-10-02 上传

2011-05-14 上传

点击了解资源详情

Lang_Billow

- 粉丝: 6

- 资源: 2

最新资源

- myeclipse快捷键大全

- Sun云计算指南(中文)

- C#程序员基础必备 c#教程

- 给定三维空间的坐标,找出这个三维空间中的洞

- QTP中一些基础代码的积累

- POWERPCB完全教学.txt

- 如何用VC++6.0 MFC 实现计算器.txt

- 常用电子元器件参考资料

- sun.pdfsun.pdfsun.pdfsun.pdf

- PCF8563 日历时钟芯片原理及应用设计

- 用单片机控制直流电机

- Thinking in Java简体中文第2版

- VSS2005之Explorer功能及技巧

- VSS2005之Administrator功能及技巧

- c8051f控制比例电磁铁

- 多核处理器大规模并行系统中的任务分配问题及算法