可编程逻辑器件PLD:硬件结构与开发流程解析

79 浏览量

更新于2024-06-29

收藏 1.09MB PPTX 举报

"可编程逻辑器件的硬件结构及其开发流程"

可编程逻辑器件(PLD)是一种电子器件,其主要特点是其逻辑功能可以根据用户的需求通过编程进行定制,而不是固定不变。PLD的种类多样,包括PROM、PLA、PAL、GAL、CPLD以及FPGA。这些器件在复杂度上有所不同,从简单的逻辑门到复杂的可编程逻辑解决方案。

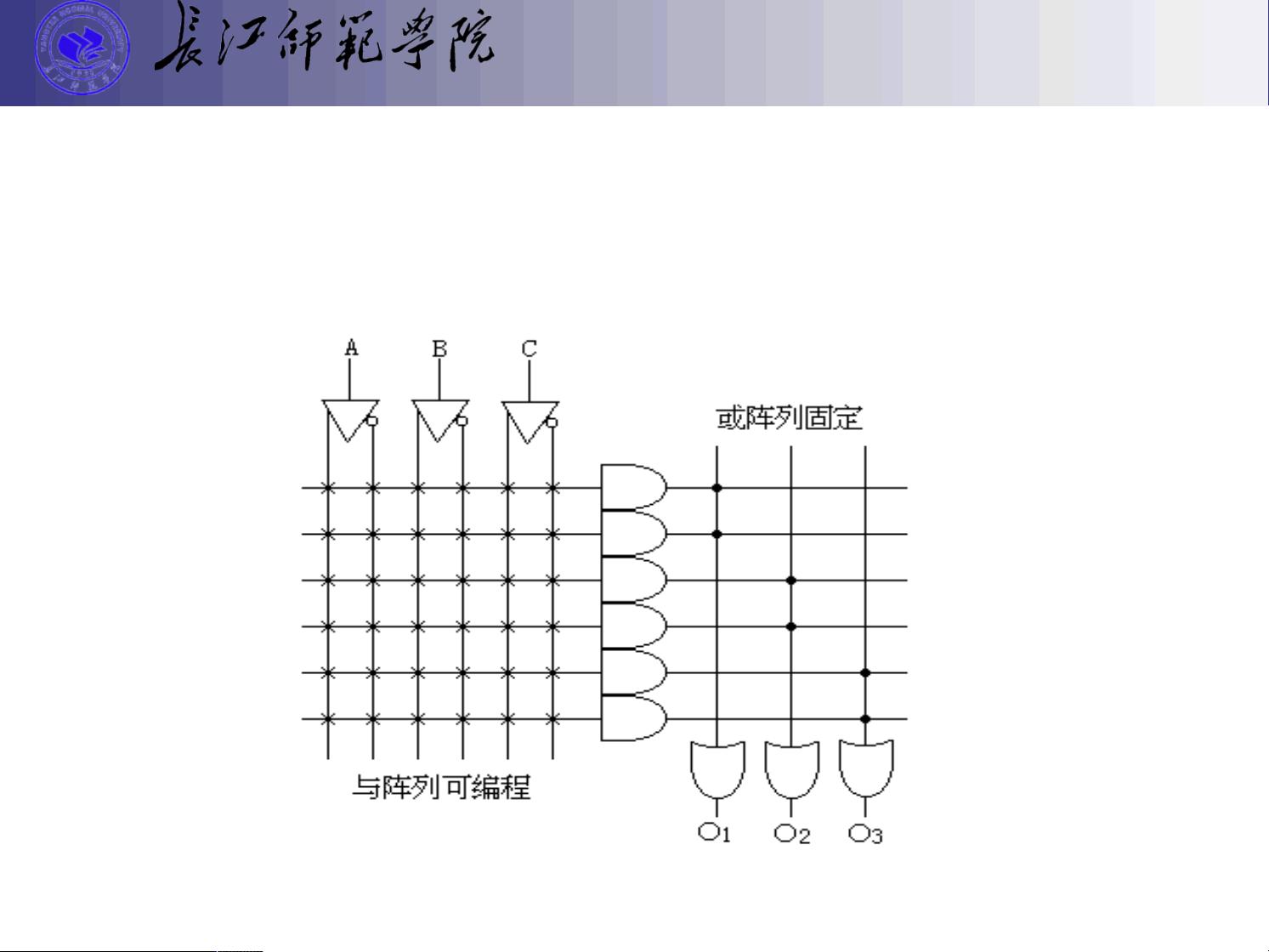

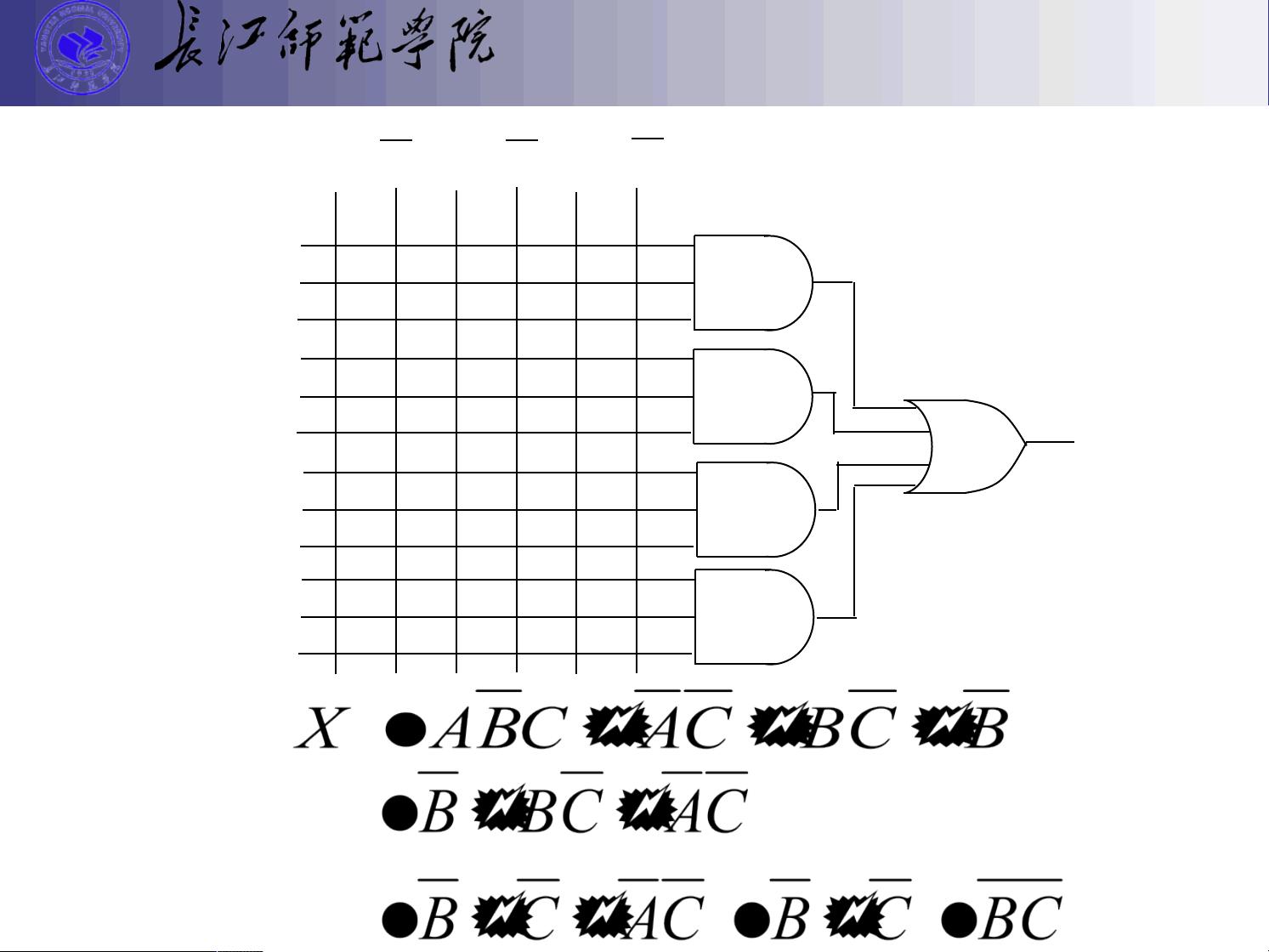

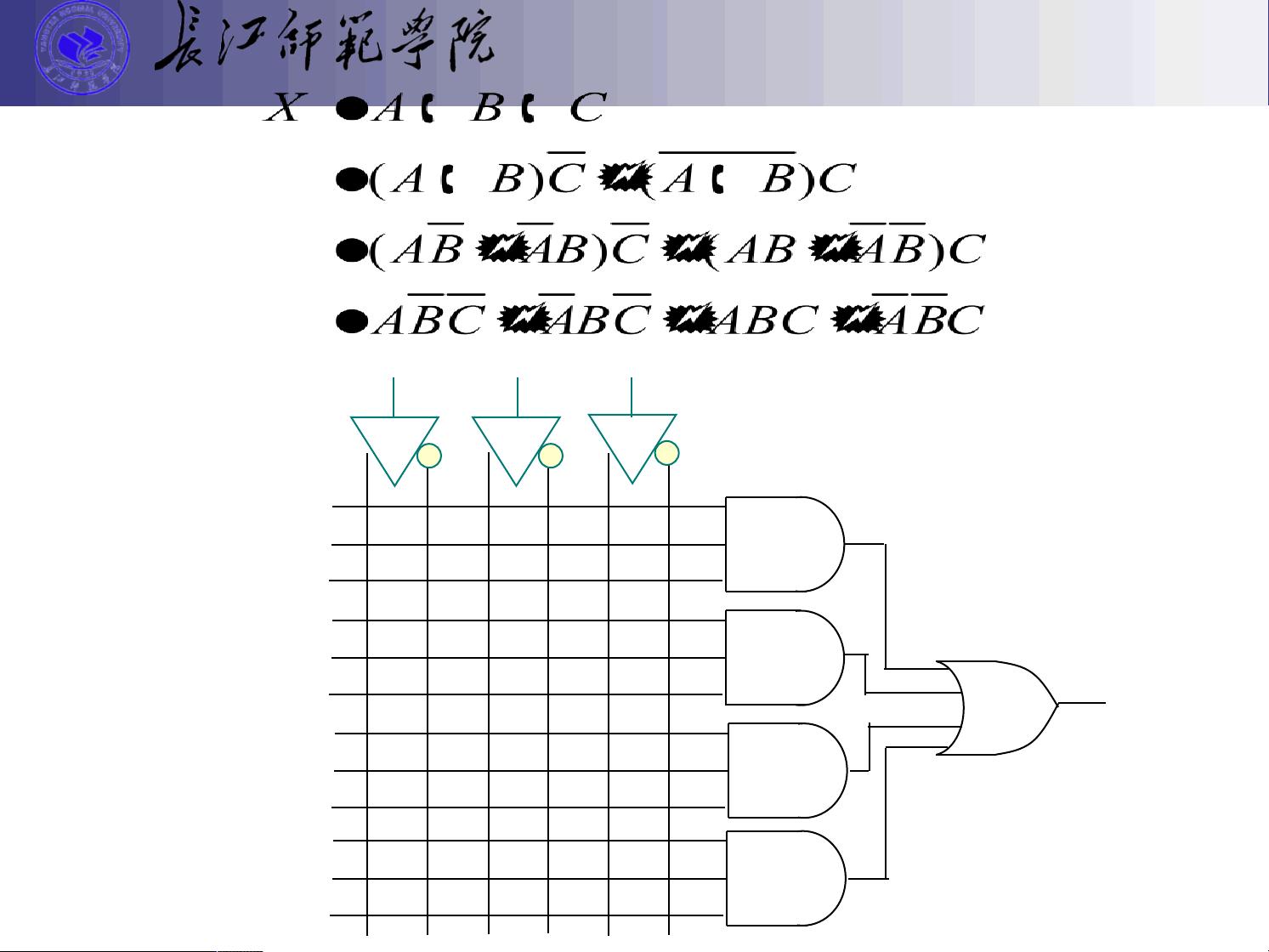

PROM(Programmable Read-Only Memory)是一种一次编程的存储器,一旦编程完成,其内容就不能更改。PLA(Programmable Logic Array)允许用户自定义与或阵列,以实现所需的逻辑功能。PAL(Programmable Array Logic)进一步扩展了这一概念,增加了可编程输出逻辑。GAL(Generic Array Logic)则提供了更高级的灵活性,可以实现更复杂的逻辑功能。CPLD(Complex Programmable Logic Device)具有更复杂的结构,采用连续式互连结构,确保逻辑单元之间的连接一致性。FPGA(Field-Programmable Gate Array)是目前最复杂的一种PLD,它包含大量的可编程逻辑块和可配置的互连资源,能实现非常复杂的逻辑设计,并且在设计完成后可以通过配置芯片进行现场编程。

在PLD的设计过程中,通常会使用门电路符号来表示逻辑功能,如与门、或门、非门、与非门和或非门等。PLD的逻辑表示方法还包括图形符号,其中缓冲门可以看作是与门,可编程连接或不连接的门则代表了PLD的可编程特性。

CPLD的互连结构是固定的,这意味着每次布线路径都相同,这在一定程度上限制了其灵活性,但也有助于提高可靠性。相比之下,FPGA的互连结构更加灵活,可以根据设计需求进行配置,从而实现更广泛的逻辑功能。例如,Spartan-3E FPGA系列提供了灵活的配置方法,可以根据设计需求调整资源分配。

在开发流程中,设计者通常使用EDA(Electronic Design Automation)平台,输入用硬件描述语言(HDL)编写的文本、原理图或状态图形,经过编译、优化、转换和综合等步骤,生成门级电路描述的网表文件。这个综合过程确保了设计的硬件实现与给定的硬件结构和约束条件相匹配。

FPGA中的查找表(LUT,Look-Up Table)是实现逻辑功能的关键组件,它们可以快速并灵活地实现任何布尔函数。嵌入式阵列(EAB)则进一步增强了FPGA的性能。此外,FPGA还有助于降低功耗,防止电源噪声,同时通过灵活的管脚定义减少设计工作量,缩短系统开发时间。

在实际应用中,比如编写PAL(GAL)阵列的输出表达式,或者使用FPGA的LUT实现特定函数,都是PLD开发过程中的常见任务。通过这样的编程,用户可以定制出满足特定需求的逻辑电路,而不受限于预设的功能。

总结来说,可编程逻辑器件的硬件结构和开发流程涉及多种类型的器件,从简单的PROM到复杂的FPGA,每种都有其独特的优势和应用场景。开发过程包括设计输入、逻辑综合和硬件配置,使得PLD成为现代电子设计中不可或缺的一部分,广泛应用于各种领域,如通信、计算机、工业控制和消费电子等。

2022-11-14 上传

2022-11-17 上传

2022-11-14 上传

2022-11-14 上传

2022-11-14 上传

2022-11-18 上传

2022-11-18 上传

2022-11-14 上传

matlab大师

- 粉丝: 2736

- 资源: 8万+

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率