数字电路设计:减法计数器与串行序列检测

版权申诉

29 浏览量

更新于2024-07-01

收藏 1.72MB DOCX 举报

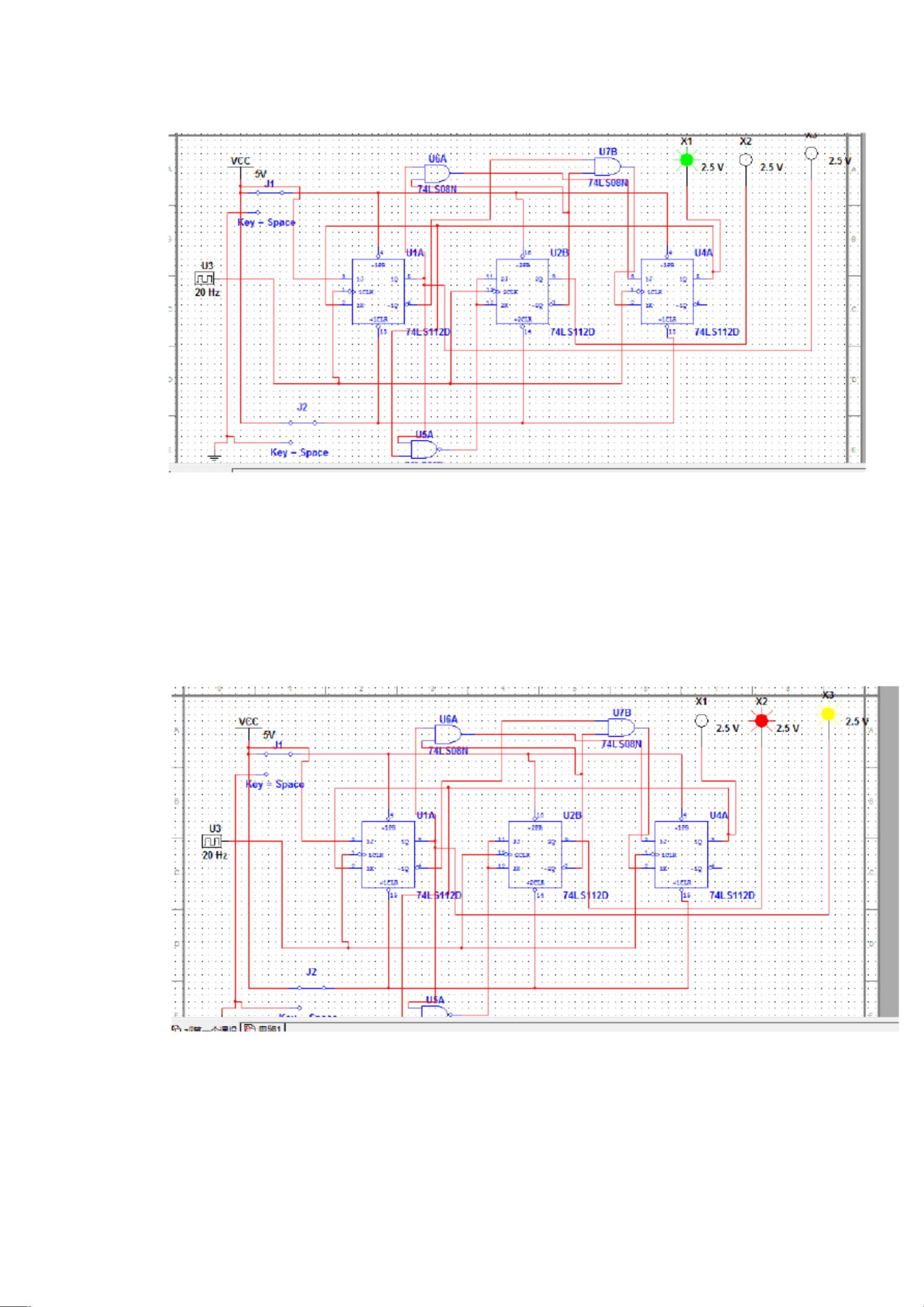

"该文档是关于数电课设的,主要讨论了减法计数器和串行序列检测器的设计,以及如何使用Multisim软件进行电路仿真。设计任务包括构建三位同步二进制减法计数器,以及一个能检测序列1100的串行序列检测器。文档还提到了两种设计序列信号发生器的方法,并在最后进行了设计总结和体会的分享。"

本文档详细介绍了数字电子课程设计的内容,主要关注减法计数器和串行序列检测器的实现。课程设计的目的是巩固理论知识,提升实践技能,通过实际操作加深对数字电路中逻辑器件的理解。

在设计任务部分,学生被要求使用JK触发器、74LS00和74LS08等逻辑门组件,设计一个能识别001和010为无效状态的三位同步二进制加法器。此外,还需要构建一个能检测特定串行序列111111的电路,并确保其在遇到无效状态时能自行启动。设计过程中,使用Multisim软件进行电路设计和仿真,以检验设计的正确性和有效性。

Multisim软件是电路设计和仿真的强大工具,允许用户创建电路图,放置和连接元器件,并进行实时仿真。通过软件,可以观察和分析电路参数,进行必要的调整,以满足设计要求。

接下来,文档详细探讨了三位同步二进制减法计数器的理论分析,这涉及到计数器的工作原理和逻辑门的组合。减法计数器在计数过程中,数值递减,通常由触发器和逻辑门电路构成,通过同步时钟信号控制计数状态的变化。

串行序列检测电路设计部分,目标是检测特定的四位序列1100。这种检测器可能基于计数器和比较器的组合,当输入序列与预设序列匹配时,输出特定的信号。

在设计序列信号发生器的部分,提供了两种方法。第一种方法结合计数器和数据选择器,第二种方法则利用D触发器。这两种方法都旨在产生特定的序列,可以根据设计需求和可用资源选择合适的方法。

最后,设计总结和体会部分,作者分享了在设计过程中的学习和感悟,可能是关于电路设计、问题解决技巧,以及软件使用的经验。

整个文档不仅涵盖了数字电路的基本原理,还强调了实践操作和问题解决的重要性,是数字电子学习者的一份宝贵参考资料。

164 浏览量

194 浏览量

374 浏览量

580 浏览量

786 浏览量

480 浏览量

123 浏览量

2022-06-16 上传

G11176593

- 粉丝: 6944

最新资源

- WebDrive v16.00.4368: 简易易用的Windows风格FTP工具

- FirexKit:Python的FireX库组件

- Labview登录界面设计与主界面跳转实现指南

- ASP.NET JS引用管理器:解决重复问题

- HTML5 canvas绘图技术源代码下载

- 昆仑通态嵌入版ASD操舵仪软件应用解析

- JavaScript实现最小公倍数和最大公约数算法

- C++中实现XML操作类的方法与应用

- 设计编程工具集:材料重量快速计算指南

- Fancybox:Jquery图片轮播幻灯弹窗插件推荐

- Splunk Fitbit:全方位分析您的活动与睡眠数据

- Emoji表情编码资源及数据库查询实现

- JavaScript实现图片编辑:截取、旋转、缩放功能详解

- QNMS系统架构与应用实践

- 微软高薪面试题解析:通向世界500强的挑战

- 绿色全屏大气园林设计企业整站源码与多技术项目资源