四片ADSP-TS201S构建的多DSP并行处理系统

190 浏览量

更新于2024-08-30

收藏 180KB PDF 举报

"该文主要讨论了一种基于ADSP-TS201S的多DSP并行系统设计,用于满足宽带雷达信号处理的高速和实时性需求。文章介绍了如何通过对比分析不同并行处理结构,选择合适的方案,以及如何利用FPGA和CPCI接口优化系统性能。"

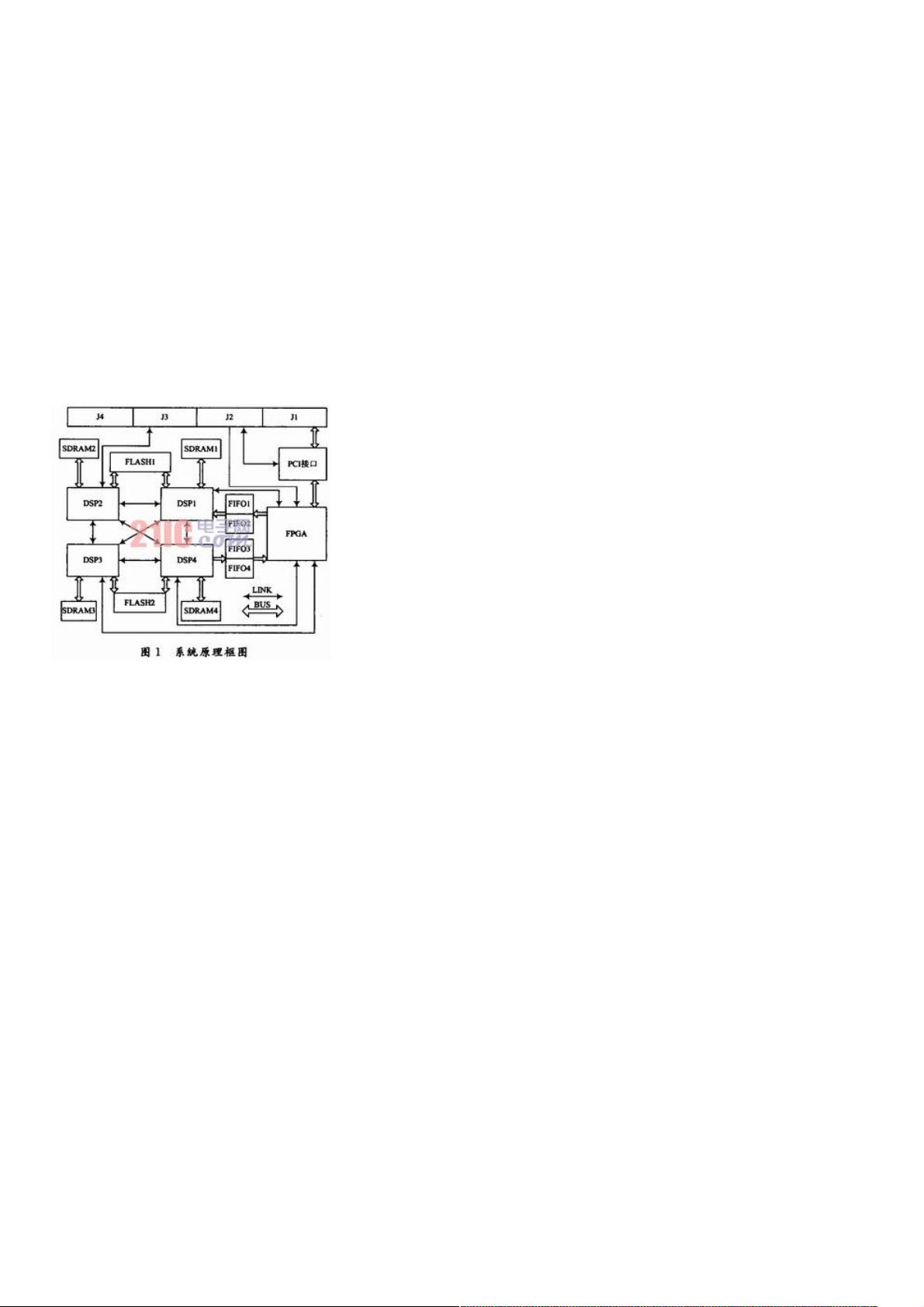

本文介绍的是一种解决宽带雷达信号处理挑战的技术方案,核心是采用多片ADSP-TS201S DSP芯片构建并行处理系统。ADSP-TS201S是一款高性能的数字信号处理器,适用于复杂的实时信号处理任务。在宽带雷达系统中,由于需要处理高采样率的回波信号,以及执行大量的脉冲压缩和高分辨率目标检测计算,单片DSP的处理能力往往不足,因此需要并行处理技术来提升系统性能。

作者通过比较3种不同的ADSP-TS201S并行处理架构,选择了外部总线共享与链路口混合耦合的方式,这种方式可以有效地分摊计算负载,提高处理速度。此外,为了进一步提升系统的灵活性和效率,系统设计中还融入了FPGA(现场可编程门阵列)和CPCI(Compact PCI)接口。FPGA在系统中起到控制和数据转换的作用,它可以高效地处理大量底层算法,同时协调多片DSP之间的通信。CPCI接口则用于板卡间的高速数据传输,确保整个系统的实时性和稳定性。

系统设计中,4片DSP根据任务需求进行分工协作,串行信号直接送至DSP2进行处理,而并行信号则先由FPGA接收并存储,待处理完成后,再通过DSP进行处理。处理结果由DSP4写入FIFO(先进先出队列),由FPGA读取并进行时序转换,通过CPCI总线传递到系统其他部分。这种设计不仅优化了数据流路径,也提高了系统的吞吐量。

本文提出的基于ADSP-TS201S的多DSP并行系统设计,结合FPGA和CPCI接口,为解决宽带雷达信号处理的挑战提供了一个有效且灵活的解决方案。这种设计思路不仅适用于雷达系统,也可以应用于其他对实时性和处理速度有高要求的信号处理领域。

2020-10-23 上传

2021-09-25 上传

2020-10-20 上传

2021-02-03 上传

2020-10-22 上传

点击了解资源详情

点击了解资源详情

2010-06-28 上传

2021-01-19 上传

weixin_38560107

- 粉丝: 1

- 资源: 936

最新资源

- Material Design 示例:展示Android材料设计的应用

- 农产品供销服务系统设计与实现

- Java实现两个数字相加的基本代码示例

- Delphi代码生成器:模板引擎与数据库实体类

- 三菱PLC控制四台电机启动程序解析

- SSM+Vue智能停车场管理系统的实现与源码分析

- Java帮助系统代码实现与解析

- 开发台:自由职业者专用的MEAN堆栈客户端管理工具

- SSM+Vue房屋租赁系统开发实战(含源码与教程)

- Java实现最大公约数与最小公倍数算法

- 构建模块化AngularJS应用的四边形工具

- SSM+Vue抗疫医疗销售平台源码教程

- 掌握Spring Expression Language及其应用

- 20页可爱卡通手绘儿童旅游相册PPT模板

- JavaWebWidget框架:简化Web应用开发

- 深入探讨Spring Boot框架与其他组件的集成应用