定点乘法实验报告 - 岳宇轩

需积分: 0 111 浏览量

更新于2024-08-04

收藏 272KB DOCX 举报

"岳宇轩的计算机组成原理实验报告——定点乘法"

这篇实验报告主要讨论的是定点乘法的实现,作者岳宇轩是2019级中国海洋大学计算机科学与技术系的学生。实验的目的是设计一个低效率的迭代乘法算法,用于处理两个32位定点数的乘法操作。实验涉及到的文件包括multiply.v和testbench.v,其中multiply.v是乘法器的Verilog模块实现,testbench.v则是测试平台。

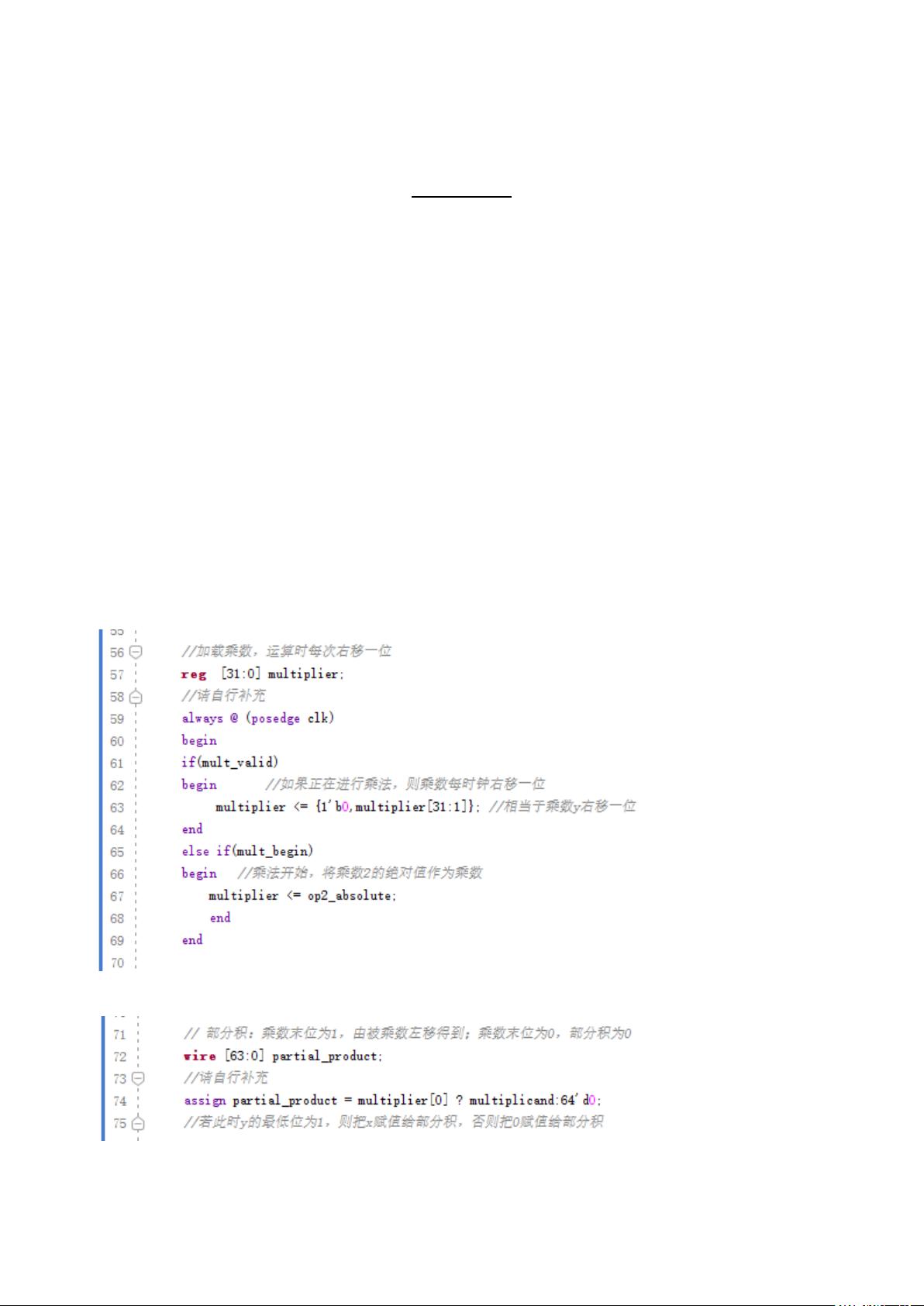

在multiply.v文件中,乘法器模块接收四个输入:时钟(clk)、乘法开始信号(mult_begin)、两个乘数(mult_op1和mult_op2),以及两个输出:乘积(product)和乘法结束信号(mult_end)。乘法结束信号的计算逻辑是:当乘法正在进行且乘数全为0时,该信号为高电平。在always @(posedge clk)块中,根据乘法开始和结束信号来控制mult_valid标志,表示乘法运算的状态。

在乘法器的设计中,首先进行了取符号和取绝对值的操作。通过判断输入乘数的最高位(符号位),可以得到每个操作数的符号(op1_sign和op2_sign),并计算出它们的绝对值(op1_absolute和op2_absolute)。正数的绝对值是其本身,负数的绝对值是取反再加1。这种分离符号和数值位的方法是为了后续的迭代乘法运算。

虽然报告中没有给出完整的multiply.v文件内容,但可以推测在后续的代码中,会有一个循环结构,每次时钟上升沿,乘数会右移一位,同时根据当前位和两个绝对值的乘积进行累加,直到乘数全部移位完毕,最终得到的累积结果就是乘积。这个过程是一个简单的位乘法,效率较低,但易于理解。

在testbench.v文件中,通常会设置一组输入数据,模拟乘法开始信号,然后通过仿真观察乘法器的输出是否正确,以验证乘法器模块的功能。

这个实验旨在理解和实现定点数乘法的硬件逻辑,通过Verilog语言进行描述,有助于深入理解数字逻辑和计算机组成原理中的基本运算单元设计。

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2023-03-13 上传

2024-11-20 上传

2023-05-15 上传

2023-12-01 上传

2023-05-25 上传

2023-04-25 上传

乐居买房

- 粉丝: 25

- 资源: 311

最新资源

- 数据库基础了解+习题有答案

- 系统的传递函数阵和状态空间表达式的转换

- FTL Intel

- 综合过程Design Compiler.doc

- JavaFX编程语言中文教程

- 悟透javaScript

- j2me帮助手册很好的东西

- linux gdb 调试手册

- Ansys 使用问答精华.pdf

- servlet2.4规范

- 操作系统考试试题含答案

- General Search

- 单片机毕业设计论文文献翻译

- 排列树问题 对于给定的n个圆,编程计算最小长度排列。

- 0-1 Knapsack 试设计一个用回溯法搜索子集空间树的函数。该函数的参数包括结点可行性判定函数和上界函数等必要的函数,并将此函数用于解0-1背包问题。

- 子集树问题 试设计一个用回溯法搜索子集空间树的函数。该函数的参数包括结点可行性判定函数和上界函数等必要的函数,并将此函数用于解装载问题。