FPGA在高速数据采集缓存系统中的核心应用

需积分: 9 190 浏览量

更新于2024-11-01

1

收藏 442KB PDF 举报

"FPGA芯片在高速数据采集缓存系统中的应用"

本文主要探讨了FPGA(Field-Programmable Gate Array)芯片在高速数据采集缓存系统中的应用。FPGA因其高速性能、低延迟、硬件可配置性和灵活性,成为了高速数据采集领域的理想选择。与传统的单片机和DSP相比,FPGA具有更高的时钟频率和更短的内部延迟,能够快速处理大量数据,并且可以集成复杂的控制逻辑、译码和接口电路。

在系统设计中,FPGA的优势在于可使用IP内核技术,允许开发者通过继承、共享或购买知识产权内核来加快开发进程。利用电子设计自动化(EDA)工具进行设计、综合和验证,能有效缩短开发周期,降低开发风险,提高设计效率,使系统更能适应市场的快速变化。

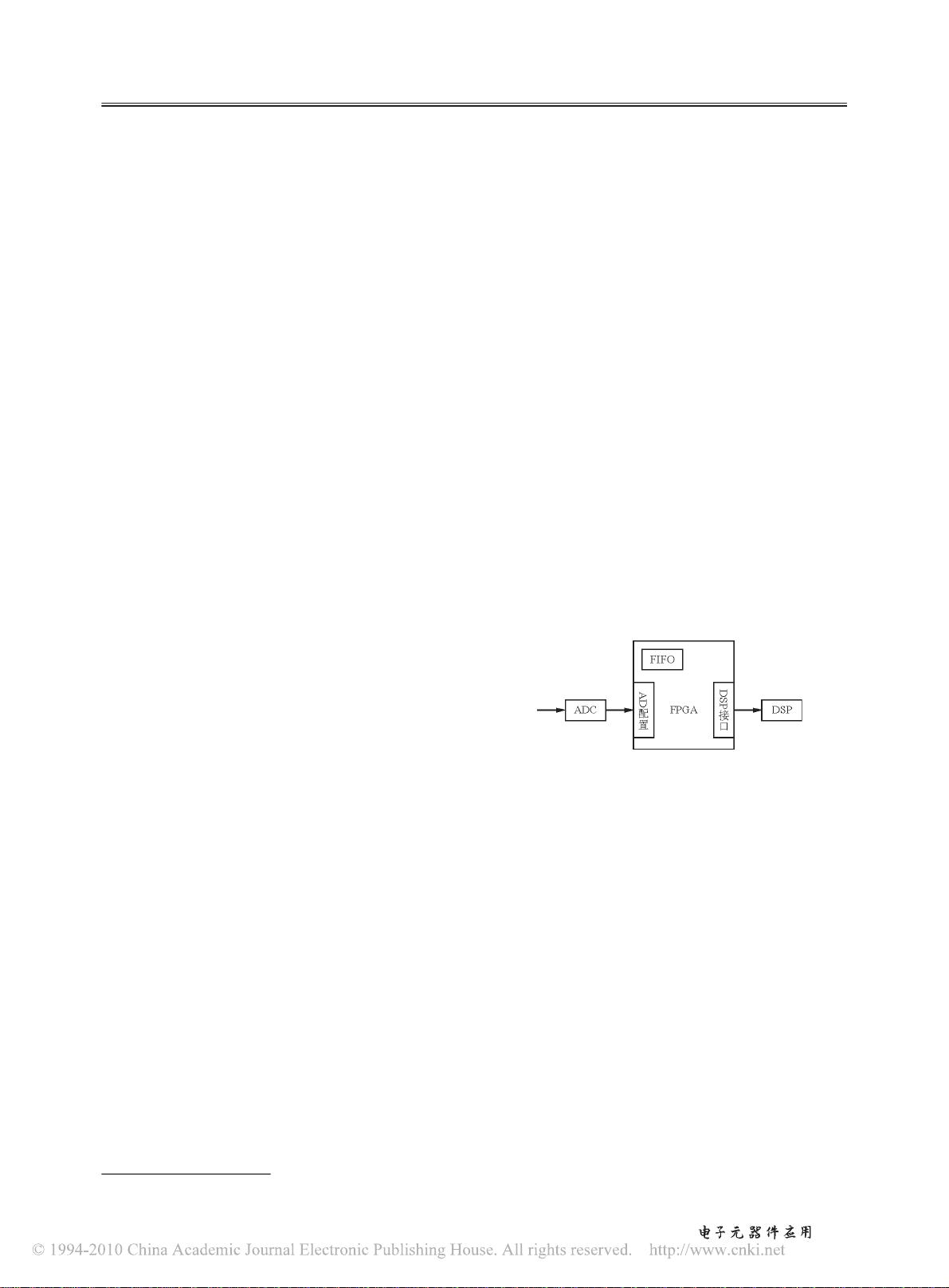

本文介绍的高速数据采集系统采用FPGA作为核心逻辑控制模块,与高速ADC(Analog-to-Digital Converter)和DSP(Digital Signal Processor)相结合,用于雷达信号的预处理和采集。系统架构中,FPGA执行多种功能,如PPL倍频、ADC控制、FIFO管理、SPI接口、DSP总线接口和自检模块等。FPGA的中断产生模块能产生周期性中断,配合视频包络和100MHz时钟生成50MHz的DMA(Direct Memory Access)同步传送时钟,实现数据高效传输至DSP。ADC控制串行接口采用通用三线串口,SPI总线接口则用于控制本振。

系统选用的ADC是数据采集的关键,其性能直接影响整个系统的性能。考虑到雷达信号处理的复杂性和处理量,高速大容量的FPGA能够满足实时数据采集和预处理的需求。本例中,系统使用的ADC应具备足够高的中频频率(1125MHz)和带宽(250MHz)以适应高速数据流。

FPGA在高速数据采集缓存系统中的应用体现了其在信号处理领域的强大能力,不仅能够提供高性能的实时处理,还具有良好的可扩展性和可定制性,使得系统可以根据不同应用场景进行灵活调整。通过合理选择FPGA芯片和ADC,可以构建出高效、稳定且适应性强的数据采集系统。

2021-10-29 上传

2021-07-13 上传

125 浏览量

186 浏览量

2021-02-03 上传

112 浏览量

2021-07-13 上传

2020-10-26 上传

185 浏览量

zhengdaobaozengna

- 粉丝: 4

最新资源

- WebDrive v16.00.4368: 简易易用的Windows风格FTP工具

- FirexKit:Python的FireX库组件

- Labview登录界面设计与主界面跳转实现指南

- ASP.NET JS引用管理器:解决重复问题

- HTML5 canvas绘图技术源代码下载

- 昆仑通态嵌入版ASD操舵仪软件应用解析

- JavaScript实现最小公倍数和最大公约数算法

- C++中实现XML操作类的方法与应用

- 设计编程工具集:材料重量快速计算指南

- Fancybox:Jquery图片轮播幻灯弹窗插件推荐

- Splunk Fitbit:全方位分析您的活动与睡眠数据

- Emoji表情编码资源及数据库查询实现

- JavaScript实现图片编辑:截取、旋转、缩放功能详解

- QNMS系统架构与应用实践

- 微软高薪面试题解析:通向世界500强的挑战

- 绿色全屏大气园林设计企业整站源码与多技术项目资源