"在Nexys4 DDR上实现DDR2读写例程及时序要求"

下载需积分: 0 | DOCX格式 | 870KB |

更新于2024-01-21

| 191 浏览量 | 举报

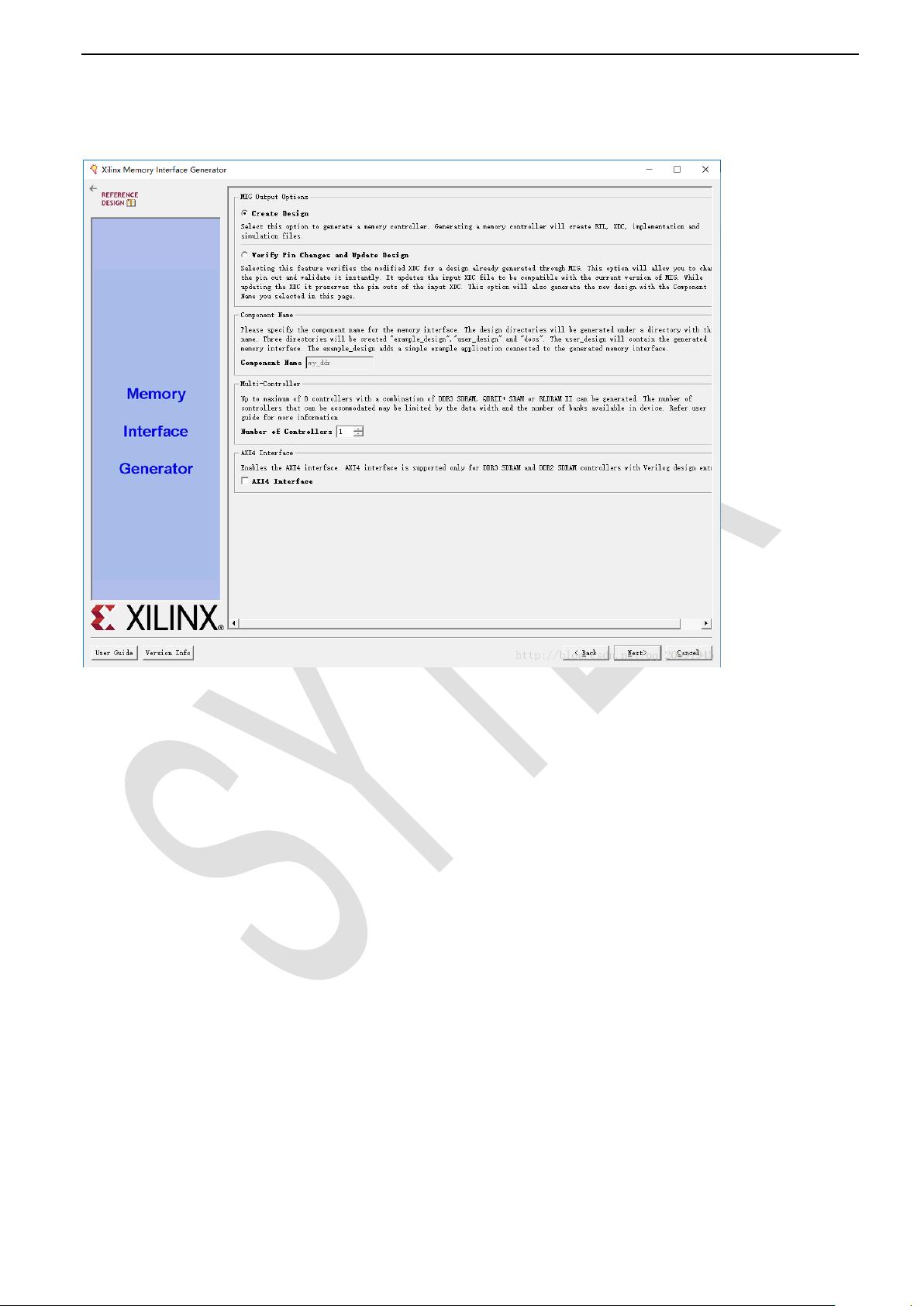

本文主要介绍了在Nexys4 DDR开发板上实现DDR2读写的例程以及对应的写操作时序。通过Vivado 2015.4工具,对DDR控制器的控制信号和写操作时序进行了详细的介绍和分析,以及必须注意的特别注意事项。

在Nexys4 DDR上实现的DDR2读写例程是通过FPGA对DDR进行读写操作所需的控制器。根据官方文档UG586,DDR控制器的时序主要包括控制信号和写操作时序。在控制信号时序中,只有当app_rdy信号有效时,程序所发出的读写命令才会被控制器接收,这点必须特别注意。在写操作时序中,向DDR写数据时,需要提供写命令app_cmd、地址app_addr、数据app_wdf_data等信号,且写入的数据最多可以比app_cmd提前一个时钟周期有效,最迟可以比app_cmd晚两个时钟周期有效。特别注意的是,在写数据的时候必须同时检测app_rdy和app_wdf_rdy信号是否有效,否则写入命令无法成功写入到DDR控制器的命令FIFO中,从而导致写操作失败。

在实现DDR2读写的例程中,使用Vivado 2015.4工具在Nexys4 DDR开发板上进行了详细的实现和分析。通过分析控制信号和写操作时序,对DDR2读写过程的关键信号进行了具体的介绍和分析,以确保读写操作的准确性和稳定性。通过本文的介绍,读者可以更加深入地了解在Nexys4 DDR上实现DDR2读写的例程所需的关键步骤和时序要求,以及如何在FPGA开发板上进行相应的控制器设计和实现。同时,对于写操作时序中的特别注意事项也为读者在实际应用中避免了可能遇到的问题,提供了重要的参考和指导。

总之,本文对在Nexys4 DDR上实现DDR2读写例程以及对应的写操作时序进行了详细的介绍和分析,通过详细分析控制信号和写操作时序,为读者提供了在FPGA开发板上实现DDR2读写的重要参考和指导,对于深入理解DDR2读写的工作原理和时序要求具有重要的参考价值。

相关推荐

一曲歌长安

- 粉丝: 1090

最新资源

- 51单片机控制的智能移动机器人设计教程

- 掌握PopupWindow实现Android下拉框技巧

- 单片机嵌入式学习全攻略:视频教程分享

- STM32电子相册:功能全面,源码完备,毕设首选

- Laravel打造移动Twitter客户端citcuit开发介绍

- 代码对比神器:文本对比工具详解

- jQuery入门教学与源码解析,前端小白必看

- 东芝TMPM3H2FWDUG微控制器的可靠性分析报告

- Python 3.6实现简易敏感词过滤技术

- MyEclipse插件Tomcat 7.0.27版本的安装与应用

- 四页css3信封式滑动效果实现

- 如何批量删除注册表中的特定字段

- Laravel集成Intercom类包装器指南

- ActiveMQ快速入门示例教程

- jQuery幻灯片插件:视觉差效果与子幻灯片创新

- 深入解析Java状态模式及其在软件开发中的应用