FN9299 Rev.3.00 Page 11 of 54

Nov 21, 2018

ISL81601 1. Overview

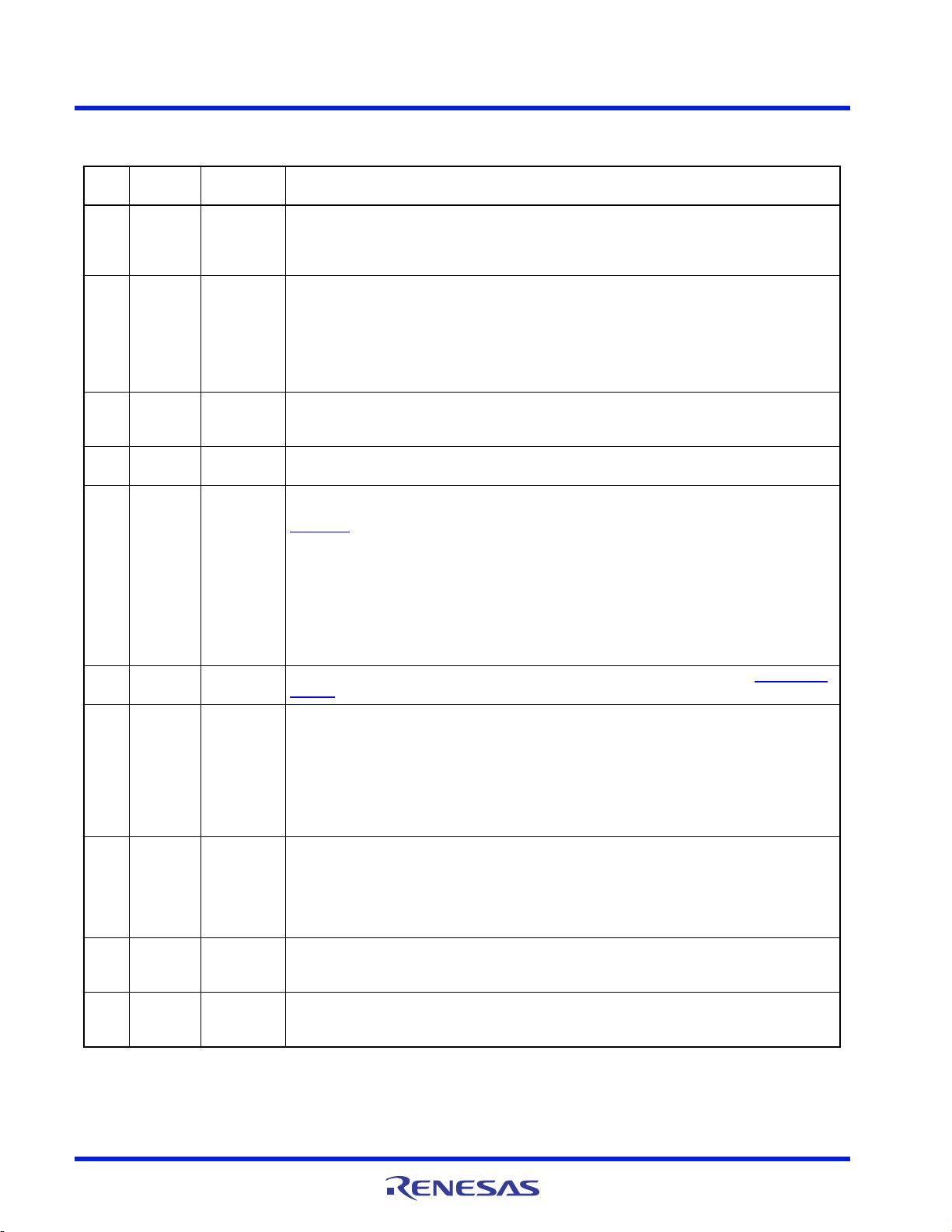

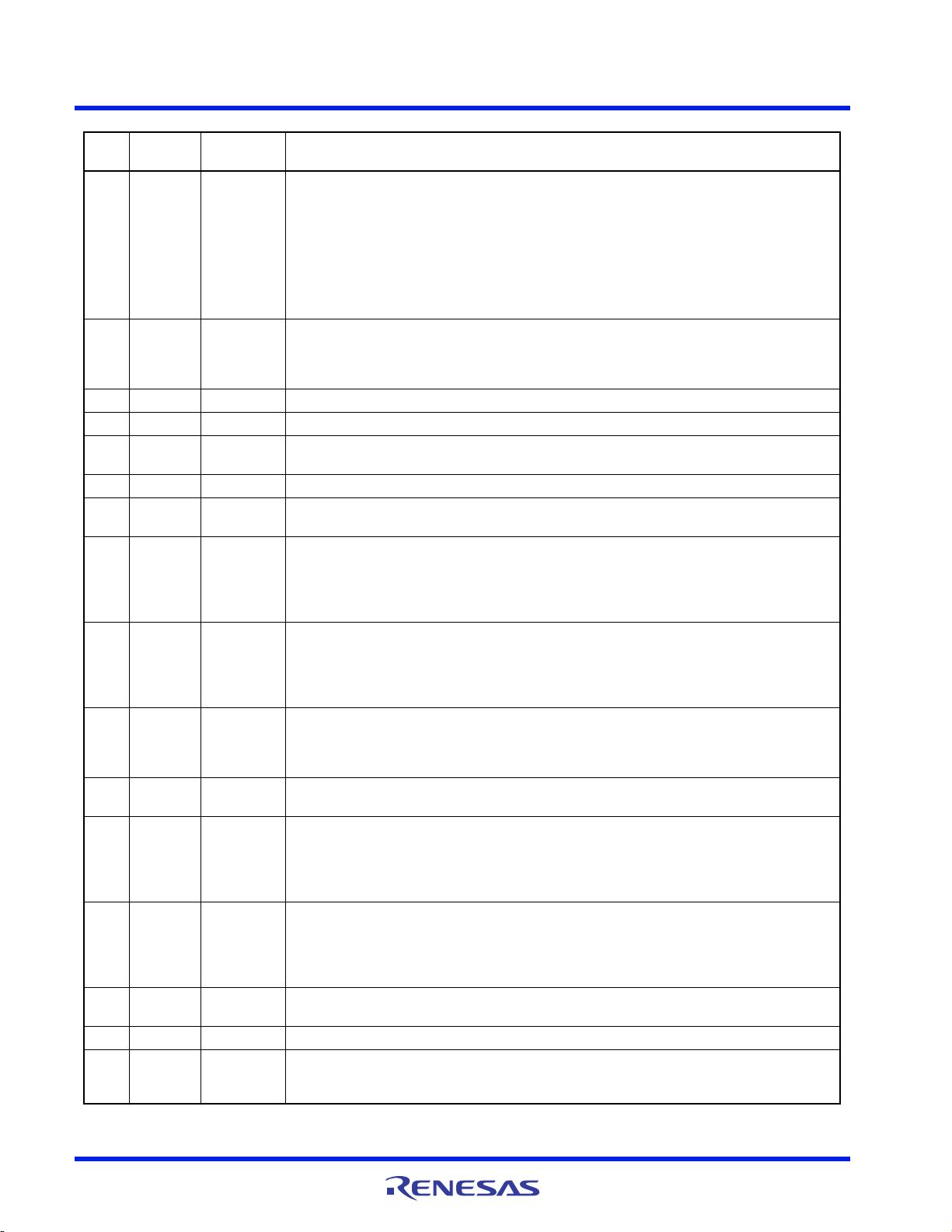

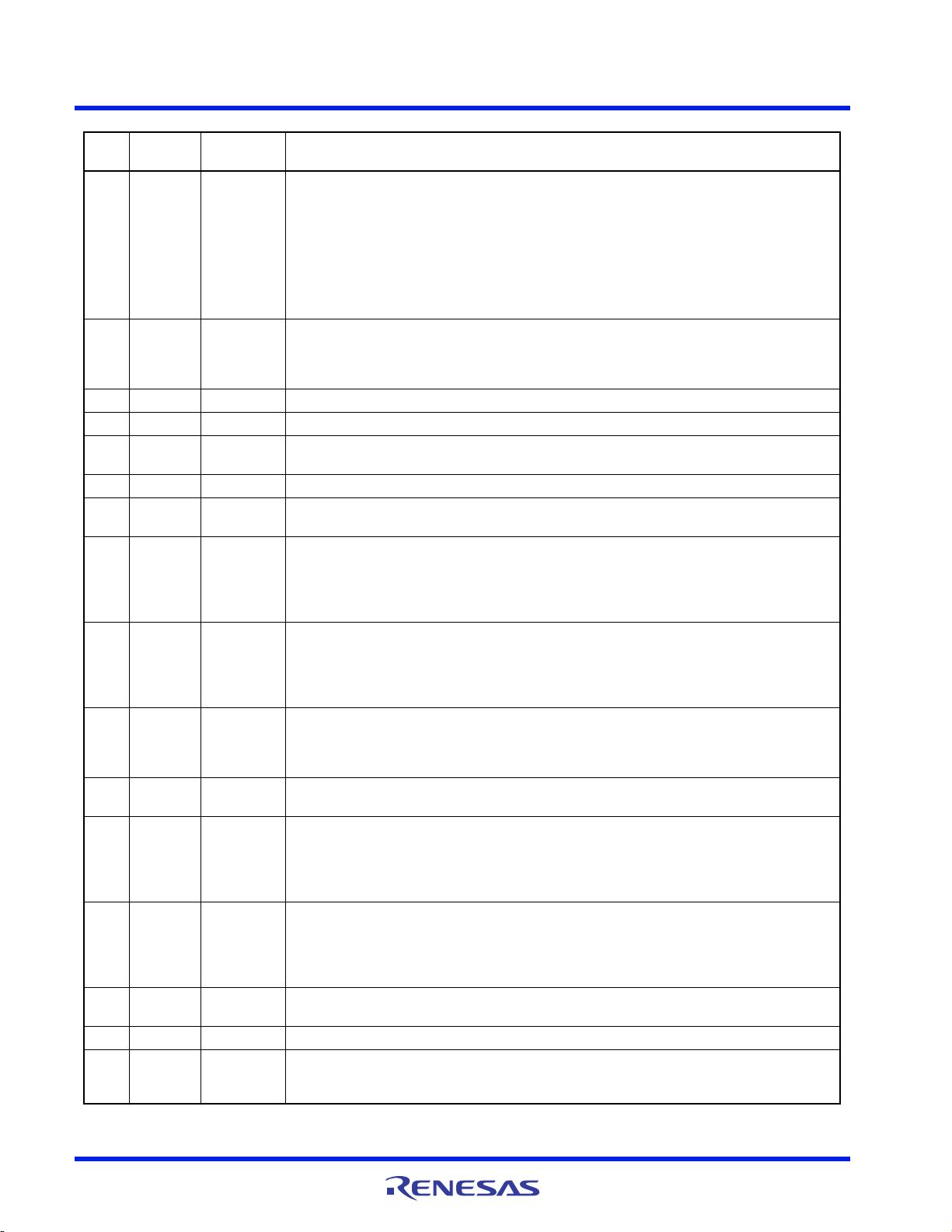

11 18 IMON_OUT Output current monitor. The current from this pin is proportional to the differential voltage between

the ISEN+ and ISEN- pins. Connect a resistor and capacitor network between the pin and SGND to

make the pin voltage proportional to the average output current. When the pin voltage reaches 1.2V,

the internal average current limit loop reduces the output voltage to keep the output current constant

when constant current OCP mode is set or the converter shuts down when hiccup OCP mode is set.

In DE Burst mode, when this pin voltage is less than 850mV, the controller runs in Burst mode.

When this pin voltage is higher than 880mV, the controller exits Burst mode. When a higher

resistance on this pin is used to set its voltage higher than 880mV at no load condition, the controller

runs in DE mode with no burst operation.

12 19 OV OVP comparator output signal. The pin is pulled low to GND by an internal 250k resistor in normal

operation. It is pulled high when output OVP trips. The pull-up MOSFET r

DS(ON)

resistance is about

4.5k. Connect this pin together in multi-chip parallel operation application to sync all the chips

together for the OVP reaction.

13 20 ISEN- Output current sense signal negative input pin.

14 21 ISEN+ Output current sense signal positive input pin.

15 23 PGOOD Open-drain logic output used to indicate the status of output voltage. This pin is pulled low when the

output is not within ±10% of the nominal voltage or the EN pin is pulled LOW.

16 25 UG2 High-side MOSFET gate driver output controlled by the boost PWM signal.

17 26 PHASE2 Phase node connection of the boost converter. This pin is connected to the junction of the upper

MOSFET’s source, filter inductor, and lower MOSFET’s drain of the boost converter.

18 27 BOOT2 Bootstrap pin to provide bias for the boost high-side driver. The positive terminal of the bootstrap

capacitor connects to this pin. Connect a bootstrap diode between this pin and VDD to create the

bias for the high-side driver. The BOOT2 to PHASE2 voltage is monitored internally. When the

voltage drops to 5.95V at no switching condition, a minimum off-time pulse is issued to turn off UG2

and turn on LG2 to refresh the bootstrap capacitor and maintain the high-side driver bias voltage.

19 29 LG2/

OC_MODE

Low-side MOSFET gate driver output controlled by the boost PWM signal and OCP mode set pin.

The OCP mode is set by a resistor connected between the pin and ground during the initiation stage

before soft-start. During the initiation stage, the pin sources out 10µA current to set the voltage on

the pin. If the pin voltage is less than 0.3V, the OCP is set to constant current mode. If the pin

voltage is higher than 0.3V, the OCP is set to Hiccup mode.

20 30 VDD Output of the internal 8V linear regulator supplied by either VIN or EXTBIAS. This output supplies

bias for the IC low-side drivers and the boot circuitries for the high-side drivers. The VDD pin must

always be decoupled to PGND pin with a minimum of 4.7µF ceramic capacitor placed very close to

the pin.

21 31 PGND Power ground connection. This pin should be connected to the sources of the lower MOSFETs and

the (-) terminals of the VDD decoupling capacitors.

22 32 LG1/

PWM_MODE

Low-side MOSFET gate driver output controlled by the buck PWM signal and PWM mode set pin.

The PWM mode is set by a resistor connected between the pin and ground during the initiation

stage before soft-start. During the initiation stage, the pin sources out 10µA current to set the

voltage on the pin. If the pin voltage is less than 0.3V, the converter is set to forced PWM mode. If

the pin voltage is higher than 0.3V, the converter is set to DE mode.

23 34 BOOT1 Bootstrap pin to provide bias for the buck high-side driver. The positive terminal of the bootstrap

capacitor connects to this pin. Connect a bootstrap diode between this pin and VDD to create the

bias for the high-side driver. The BOOT1 to PHASE1 voltage is monitored internally. When the

voltage drops to 5.95V at no switching condition, a minimum off-time pulse is issued to turn off UG1

and turn on LG1 to refresh the bootstrap capacitor and maintain the high-side driver bias voltage.

24 35 PHASE1 Phase node connection of the buck converter. This pin is connected to the junction of the upper

MOSFET’s source, filter inductor, and lower MOSFET’s drain of the buck converter.

25 36 UG1 High-side MOSFET gate driver output controlled by the buck PWM signal.

26 38 EXTBIAS External bias input for the optional VDD LDO. There is an internal switch to disconnect the VIN LDO

when EXTBIAS voltage is higher than 7.5V. Decouple this pin to ground with a 10µF ceramic

capacitor when it is in use, otherwise tie this pin to ground. DO NOT float this pin.

Pin #

(QFN)

Pin #

(HTSSOP)

Pin

Name Function