"FPGA设计数字钟:VHDL语言实现与功能拓展"

版权申诉

159 浏览量

更新于2024-02-25

收藏 368KB DOC 举报

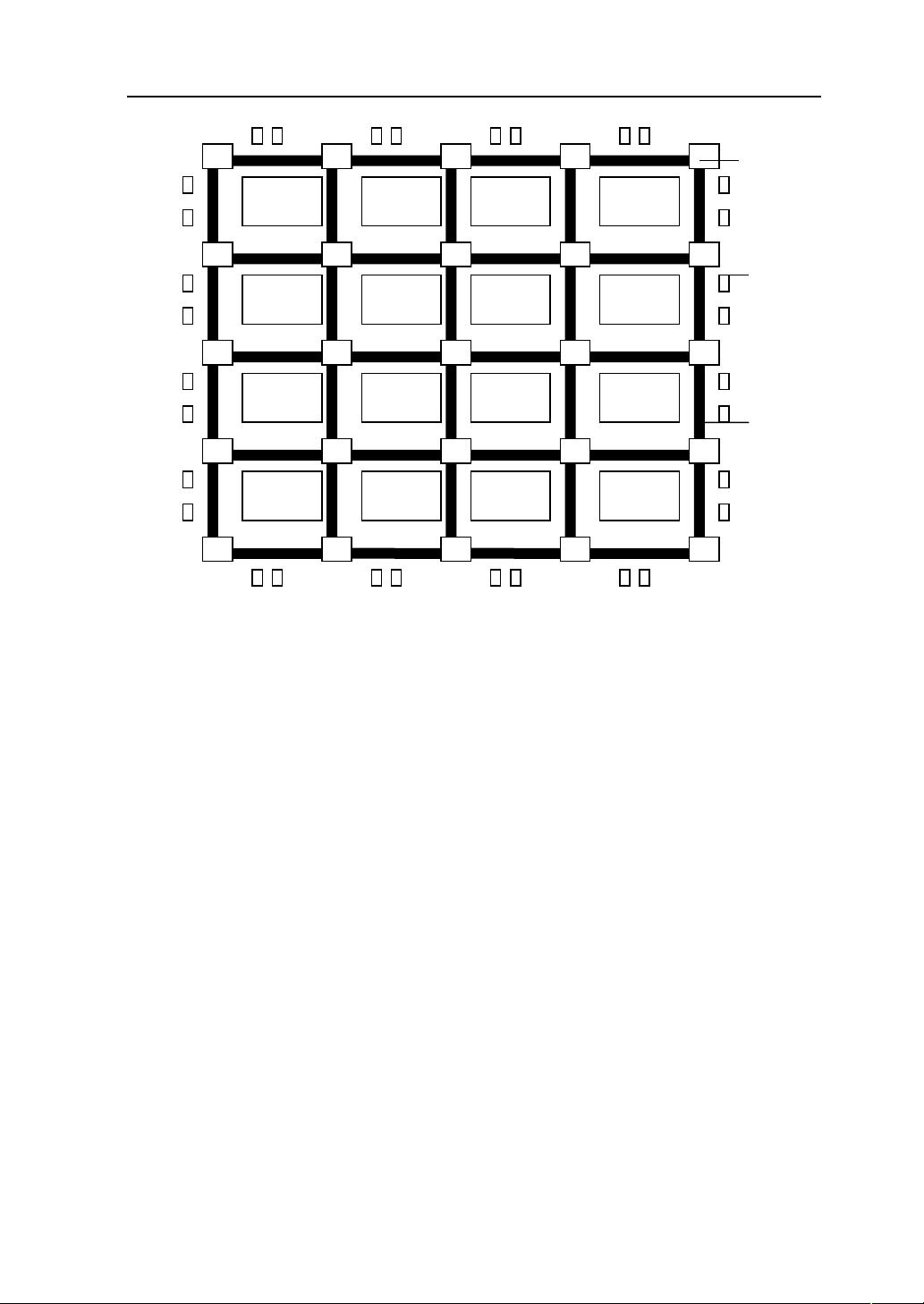

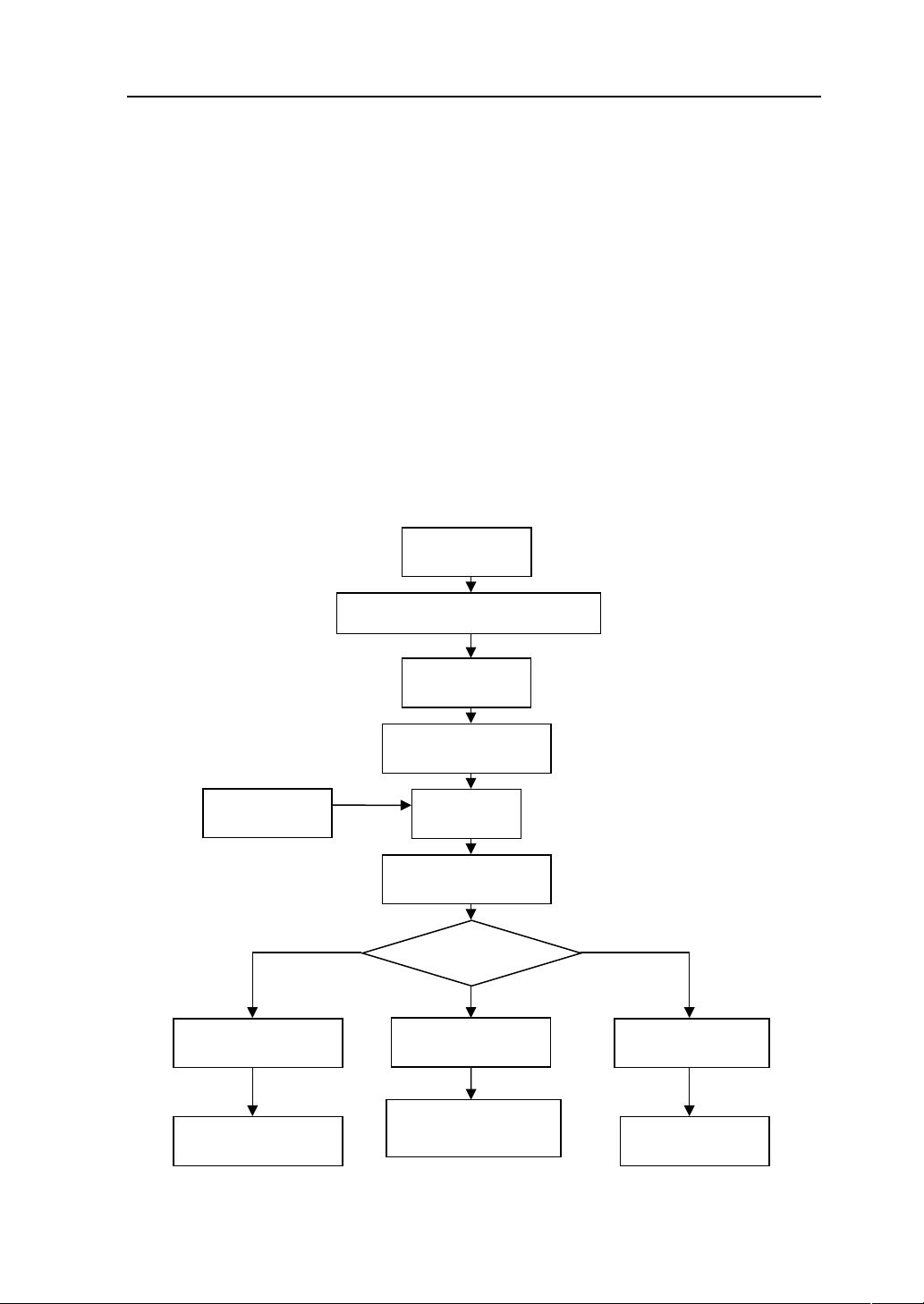

Based on VHDL language implementation, this design uses EDA technology, with VHDL as the logical description method to design files. In the MaxplusII tool environment, a FPGA-based digital clock is created using a top-down design approach, where various basic modules work together to form the clock. The chip used is EP1K100QC208-3, consisting of clock module, control module, timing module, data decoding module, display and alarm module. After compiling and simulating the program, it is downloaded and verified on the programmable logic device. The system can display the year, month, day, hours, minutes, and seconds separately, with functions for clock calibration, reset, start and stop using keyboard inputs. Key words: digital clock; hardware description language; VHDL; FPGA; keyboard interface.

In summary, the digital clock design implemented in VHDL language on FPGA is a comprehensive and functional system that accurately displays time and date information. The utilization of EDA technology and top-down design methodology ensures a structured and efficient development process. The clock's various modules work together seamlessly to provide users with a reliable and user-friendly experience. The ability to calibrate, reset, start and stop the clock using keyboard inputs adds convenience and flexibility to the system. Overall, this FPGA-based digital clock design showcases the power and versatility of hardware description languages in creating complex yet practical electronic systems.

6965 浏览量

226 浏览量

2024-04-16 上传

215 浏览量

320 浏览量

2021-10-04 上传

2021-09-30 上传

2023-06-20 上传

智慧安全方案

- 粉丝: 3845

- 资源: 59万+

最新资源

- saturn::globe_with_meridians:新的迷你快速浏览器

- 企业前台大厅模型设计

- 基于python+django+vue开发的工作数据获取与可视化

- NodeJS-Sample-Project:使用Express的节点Js上的样本项目,具有基本结构和数据库连接

- 战利品

- myBinomTest(s,n,p,Sided):具有任意二项式概率的 1 或 2 边二项式检验-matlab开发

- 银行存款余额调节表格excel模版下载

- 演唱会舞台3D模型

- autoprop:从访问器方法推断属性

- ABAssignment04

- 物品交接明细表excel模版下载

- desafio_conceitos_node

- vewa_app2:VEWA 网络应用程序

- 中式现代风会议室模型

- gritjz.github.io:史蒂芬·张的个人网站

- 工程质量验收记录表excel模版下载