FPGA实现百兆以太网RGMII接口设计详解

版权申诉

"本文主要探讨了基于FPGA的百兆以太网RGMII接口设计,结合Altera的Cyclone IV FPGA芯片和Marvell的88E1111 PHY芯片,阐述了如何实现这一设计。"

在现代电子工程中,FPGA(Field-Programmable Gate Array)因其高度可配置性和高速处理能力,被广泛应用于网络通信系统的设计。在本文中,作者详细介绍了使用FPGA实现百兆以太网接口,特别是Rapid Gigabit Media Independent Interface (RGMII)接口的设计方法。

百兆以太网,即Fast Ethernet,是一种广泛使用的局域网技术,能够处理突发通信和大量数据传输,具有优秀的互操作性和丰富的软硬件支持。在FPGA中实现这种接口,可以实现高速并发处理,避免处理资源的冲突,提高数据传输效率。

文章首先提到了选择的FPGA芯片——Altera的Cyclone IV EP4CE115F29C7N,这是一款具有高性能和低功耗特性的芯片。配合88E1111 PHY芯片,可以构建完整的以太网物理层和媒体访问控制层(MAC)。

系统设计部分,作者提出了两种方案:一是单芯片解决方案,即PHY和MAC都在同一芯片上;二是分立的PHY和MAC层。文中采用前者,使用RGMII模式,其中88E1111需要通过特定的配置设置为RGMII接口,具体是通过CONFIG4和CONFIG5的电平设置来完成。

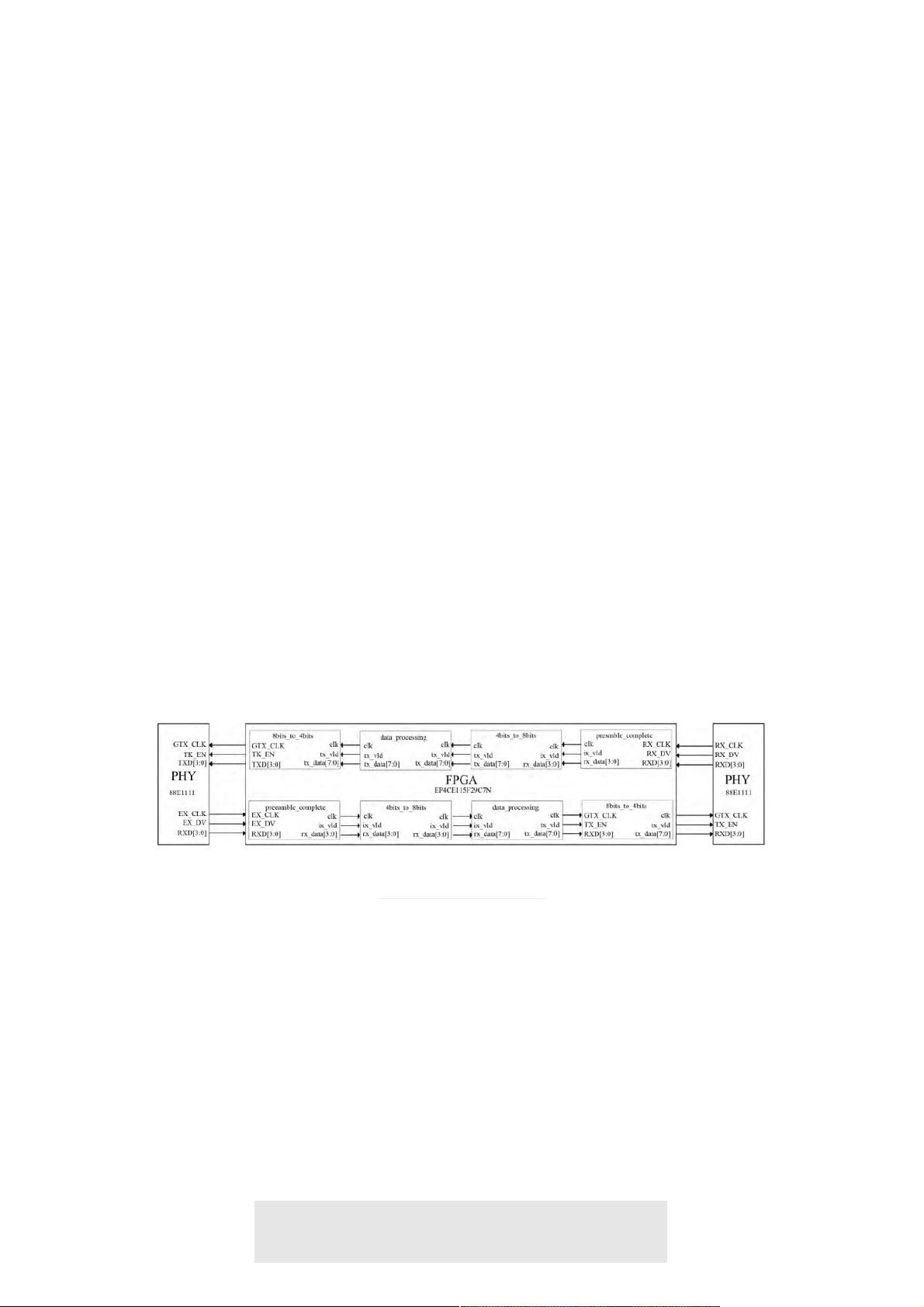

在系统功能框架中,设计包括上行和下行两个通道,数据通过PHY进入FPGA进行处理,再返回到PHY输出。关键模块包括:

1. preamble_complete模块:处理以太网帧的前导码,这是识别帧起始的关键部分。

2. 4bits_to_8bits:将4位数据拼接成8位,适应8位数据传输的标准。

3. data_processing:执行IP和MAC地址替换等高级协议处理。

4. 8bits_to_4bits:将处理后的8位数据拆分为4位,准备发送到PHY。

硬件电路实现部分,详细描述了CONFIG4和CONFIG5引脚的连接,确保正确配置88E1111为RGMII模式。此外,还讨论了PHY与MAC之间的连接,以及系统所需的时钟设计,包括12.5MHz和25MHz的时钟,这些时钟对于同步数据传输至关重要。

总体而言,这篇文章深入浅出地讲解了基于FPGA的百兆以太网RGMII接口设计,涵盖了从理论背景到实际硬件配置的各个环节,为FPGA开发人员提供了宝贵的设计参考。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-08-03 上传

2022-07-14 上传

2023-05-13 上传

2023-08-31 上传

2022-07-14 上传

2021-07-13 上传

_webkit

- 粉丝: 31

- 资源: 1万+

最新资源

- iphone application progamming guide

- java笔试题(英文版有答案与讲解)

- 01_进销存管理系统

- 软件项目开发计划书样例.doc下载

- ORACLE 数据库WEB 控制台命令

- C/C++嵌入式编程

- ObjectARX开发实例教程-20070715.pdf

- Windows平台OracleRAC构建.

- MapXtreme2005 开发手册

- IBM AIX 虚拟IO服务器实现MPIO案例分析

- Oracle_RAC_For_Window

- GB-T 20158-2006 信息技术 软件生存周期过程 配置管理

- Ansi C standard

- 《ARM应用系统开发详解——基于S3C4510B的系统设计(第二版)》

- easyarm1138

- 数据库第四版答案数据库第四版答案