高速电路设计:信号完整性的挑战与解决策略

48 浏览量

更新于2024-08-30

收藏 221KB PDF 举报

"高速电路设计中信号完整性分析"

在高速电路设计中,信号完整性是一个至关重要的概念,尤其是在系统时钟频率和信号上升时间不断提高的今天。信号完整性涉及到如何确保信号在传输过程中保持其原有的质量和形状,不受噪声干扰,避免反射、振荡和其他失真现象。随着技术的发展,这些问题在设计中变得越来越突出,而很多设计者却往往在设计后期才开始关注。

首先,特征阻抗控制是信号完整性设计的基础。在高速电路中,信号线必须被视为传输线,其特性阻抗与源和负载的阻抗匹配,以防止信号反射。不匹配会导致信号质量下降,增加功率损耗,并可能导致错误的数据传输。因此,正确计算和选择传输线的特性阻抗是保证信号完整性的关键。

其次,终端匹配也是不可或缺的一环。终端匹配电阻用于吸收信号在到达终端时可能出现的反射,以减小信号的失真。特别是在长线或高阻抗负载的情况下,终端匹配尤其重要。

电源和地平面的设计同样对信号完整性有深远影响。良好的电源和地平面布局可以提供稳定的电压参考,减少噪声耦合,提高信号质量。电源层和地层应尽可能连续且平坦,以降低阻抗并减少电磁干扰。

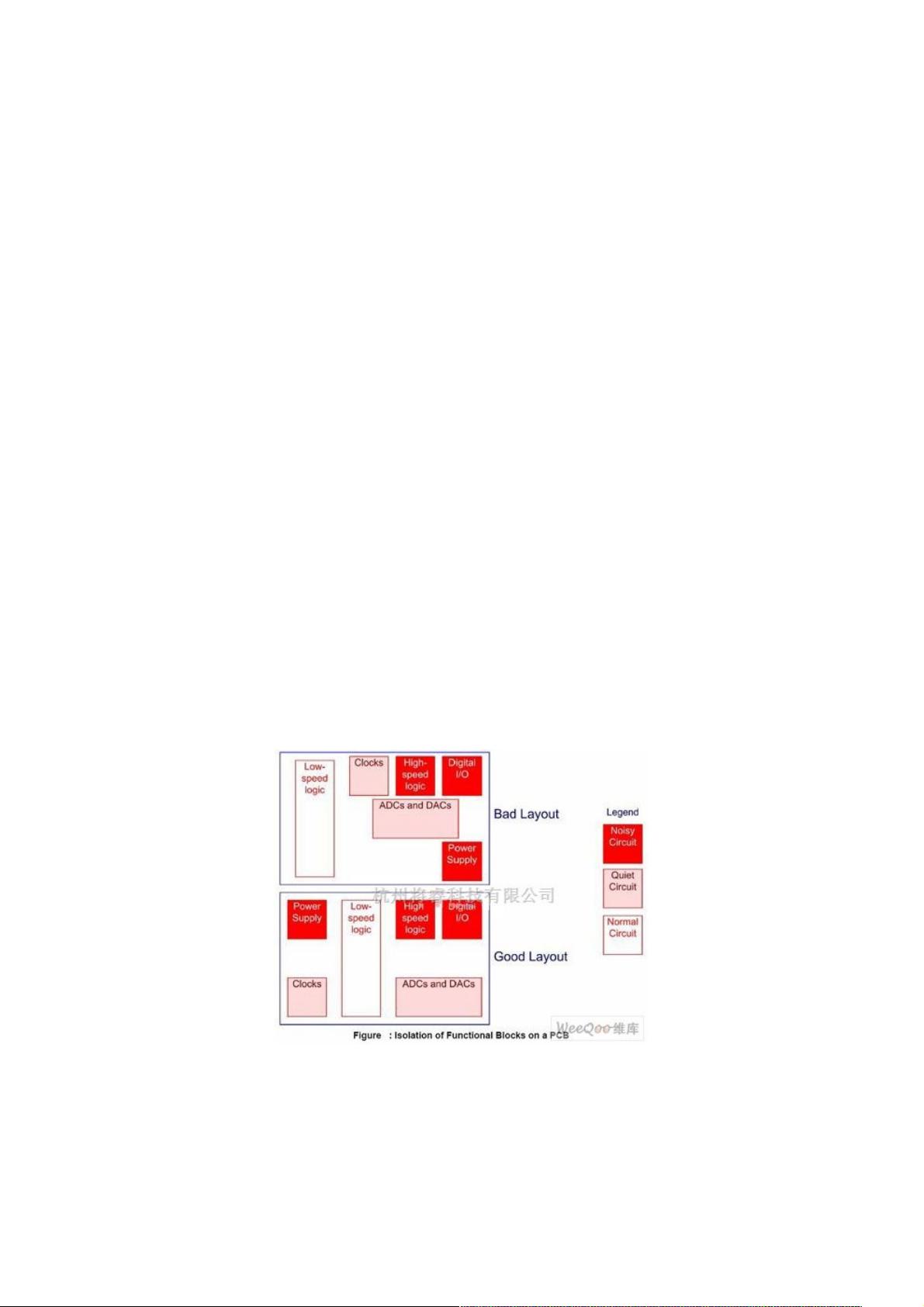

信号布线策略也对信号完整性至关重要。合理的布线能降低串扰,即一个信号线对其他信号线产生的噪声。布线应该遵循最小化互连线长度、减少转折、避免过密布线的原则,以减小信号间的相互影响。

串扰是高速电路设计中的另一个挑战,尤其是在多层PCB板上。当信号线靠近时,它们之间的电场和磁场交互作用会产生耦合噪声,影响信号质量。通过使用屏蔽层、地平面间隔和适当的布线策略,可以有效地减少串扰。

在高速数字电路设计中,信号完整性的忽视会导致一系列问题,如信号衰减、时序错误、数据丢失等,严重影响系统的稳定性和可靠性。因此,设计者必须在设计早期就考虑这些问题,进行仿真和分析,以预测和解决潜在的信号完整性问题。这不仅能够提高设计的成功率,还能避免在设计后期进行昂贵的修改。

信号完整性是高速电路设计中的核心考量因素之一。设计师需要对特征阻抗控制、终端匹配、电源地平面设计、信号布线和串扰管理有深入的理解,并在设计过程中不断优化,以实现高效、可靠的高速数字系统。通过学习和应用这些知识,工程师能够在面对高速电路设计的挑战时,更加游刃有余。

2016-06-12 上传

206 浏览量

2023-11-17 上传

117 浏览量

2020-08-27 上传

237 浏览量

178 浏览量

weixin_38567956

- 粉丝: 1

最新资源

- C#实现自定义尺寸条形码和二维码生成工具

- Bootthink多系统引导程序成功安装经验分享

- 朗读女中文朗读器,智能语音朗读体验

- Jupyter Notebook项目培训教程

- JDK8无限强度权限策略文件8下载指南

- Navicat for MySQL工具压缩包介绍

- Spring和Quartz集成教程:定时任务解决方案

- 2013百度百科史记全屏效果的fullPage实现

- MATLAB开发电磁转矩电机瞬态响应研究

- 安卓系统短信问题解决方案:使用BlurEmailEngine修复

- 不同版本Android系统的Xposed框架安装指南

- JavaScript项目实验:模拟骰子与颜色转换器

- 封装高效滑动Tab动画技术解析

- 粒子群优化算法在Matlab中的开发与应用

- 网页图书翻页效果实现与turnjs4插件应用

- JSW: 一种新型的JavaScript语法,支持Coffeescript风格