没有合适的资源?快使用搜索试试~ 我知道了~

首页Cypress S25FS128S/256S:1.8V SPI Flash with Multi-I/O and ECC Features

Cypress S25FS128S/256S:1.8V SPI Flash with Multi-I/O and ECC Fea...

需积分: 10 4 下载量 83 浏览量

更新于2024-07-15

收藏 4.69MB PDF 举报

本文档详细介绍了Cypress半导体公司的S25FS128S和S25FS256S两种1.8伏特串行外围接口(Serial Peripheral Interface, SPI)闪存存储器。这些产品具有高密度特性,分别是128Mbits(16Mbytes)和256Mbits(32Mbytes),适用于对存储容量有较高需求的应用场景。

S25FS系列采用SPI接口标准,支持多种模式:SPI时钟极性和相位模式0和3,允许双数据速率(DDR)选项。地址扩展性很强,提供24或32位地址选择,兼容S25FL-A、S25FL-K、S25FL-P和S25FL-SS等系列的命令集和引脚布局,这使得它们在不同的设计环境中能够无缝集成。

在读取操作方面,S25FS128S/256S支持多种模式,包括正常、快速、双/四/DDR四路I/O读取以及突发(Burst Wrap)、连续(XIP)和快速编程接口(QPI)。同时,它们提供了Serial Flash Discoverable Parameters (SFDP)和Common Flash Interface (CFI),用于获取配置信息,帮助用户优化闪存性能。

编程功能强大,包括256或512字节的页编程缓冲区,以及程序暂停和恢复功能。更重要的是,它们内置了自动错误校验代码(Automatic ECC),通过硬件实现单比特错误校正,提高了数据存储的可靠性和稳定性。

在擦除操作上,S25FS128S/256S支持混合扇区优化,这意味着可以选择性地擦除部分扇区,从而提高数据处理效率。这种闪存技术特别适合于那些需要高效、灵活且可扩展的数据存储应用,如嵌入式系统、微控制器和物联网设备。

Cypress的S25FS128S和S25FS256S系列闪存因其高性能、灵活的接口选项和高级纠错功能,是现代电子设计中不可或缺的存储解决方案。设计师在选择和集成这类产品时,应充分考虑其特点和应用场景的需求,以充分利用其优点。

Document Number: 002-00368 Rev. *J Page 16 of 151

S25FS128S

S25FS256S

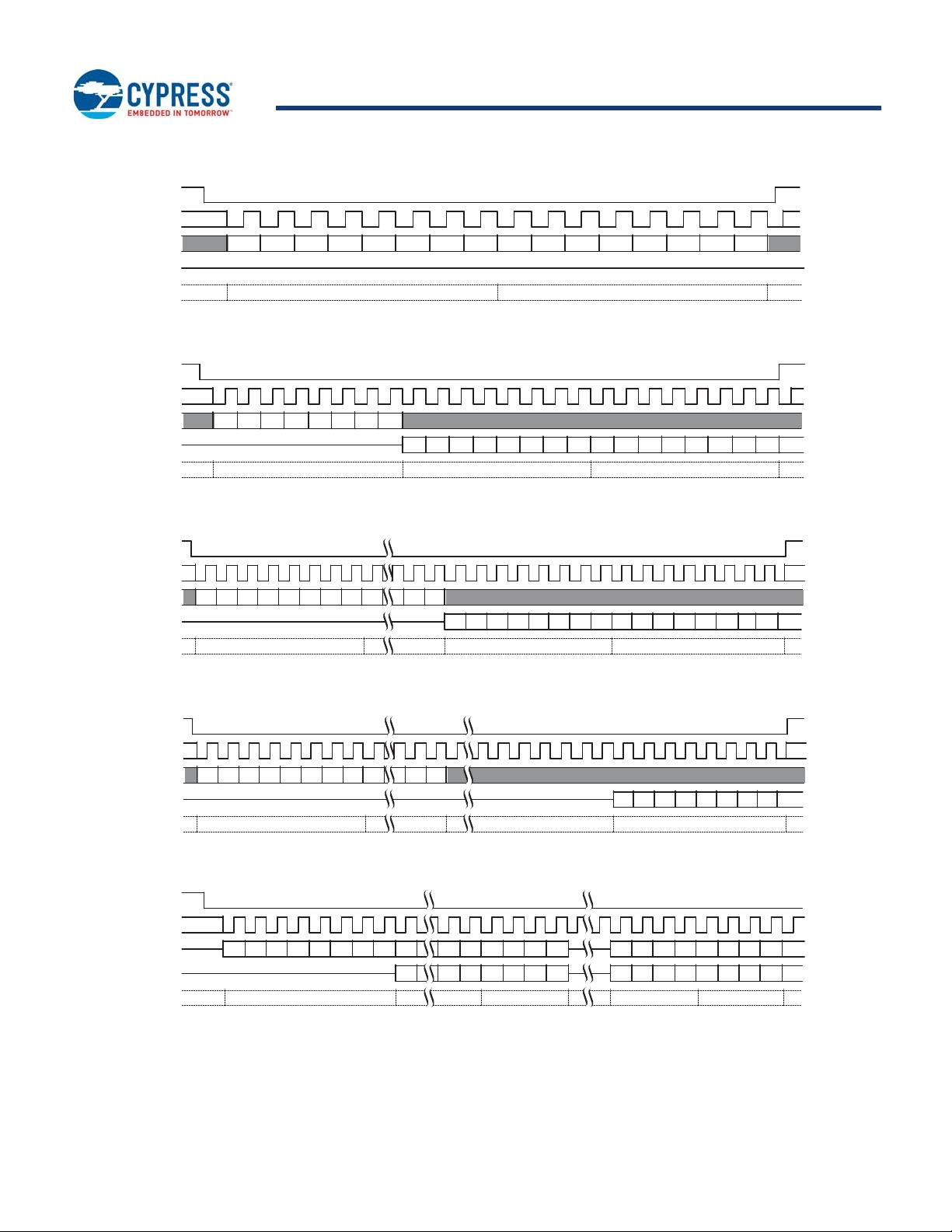

Figure 3.4 Single Bit Wide Input Command

Figure 3.5 Single Bit Wide Output Command

Figure 3.6 Single Bit Wide I/O Command without Latency

Figure 3.7 Single Bit Wide I/O Command with Latency

Figure 3.8 Dual I/O Command

CS#

SCK

SI

SO

Phase

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

Instruction Input Data

CS#

SCK

SI

SO

Phase

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

Instruction Data 1 Data 2

CS#

SCK

SI

SO

Phase

7 6 5 4 3 2 1 0 31 1 0

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

Instruction Address Data 1 Data 2

CS#

SCK

SI

SO

Phase

7 6 5 4 3 2 1 0 31 1 0

7 6 5 4 3 2 1 0

Instruction Address Dummy Cycles Data 1

CS#

SCK

IO0

IO1

Phase

7 6 5 4 3 2 1 0 30 2 0 6 4 2 0 6 4 2 0 6 4 2 0

31 3 1 7 5 3 1 7 5 3 1 7 5 3 1

Instruction Address Mode Dum Data 1 Data 2

Document Number: 002-00368 Rev. *J Page 17 of 151

S25FS128S

S25FS256S

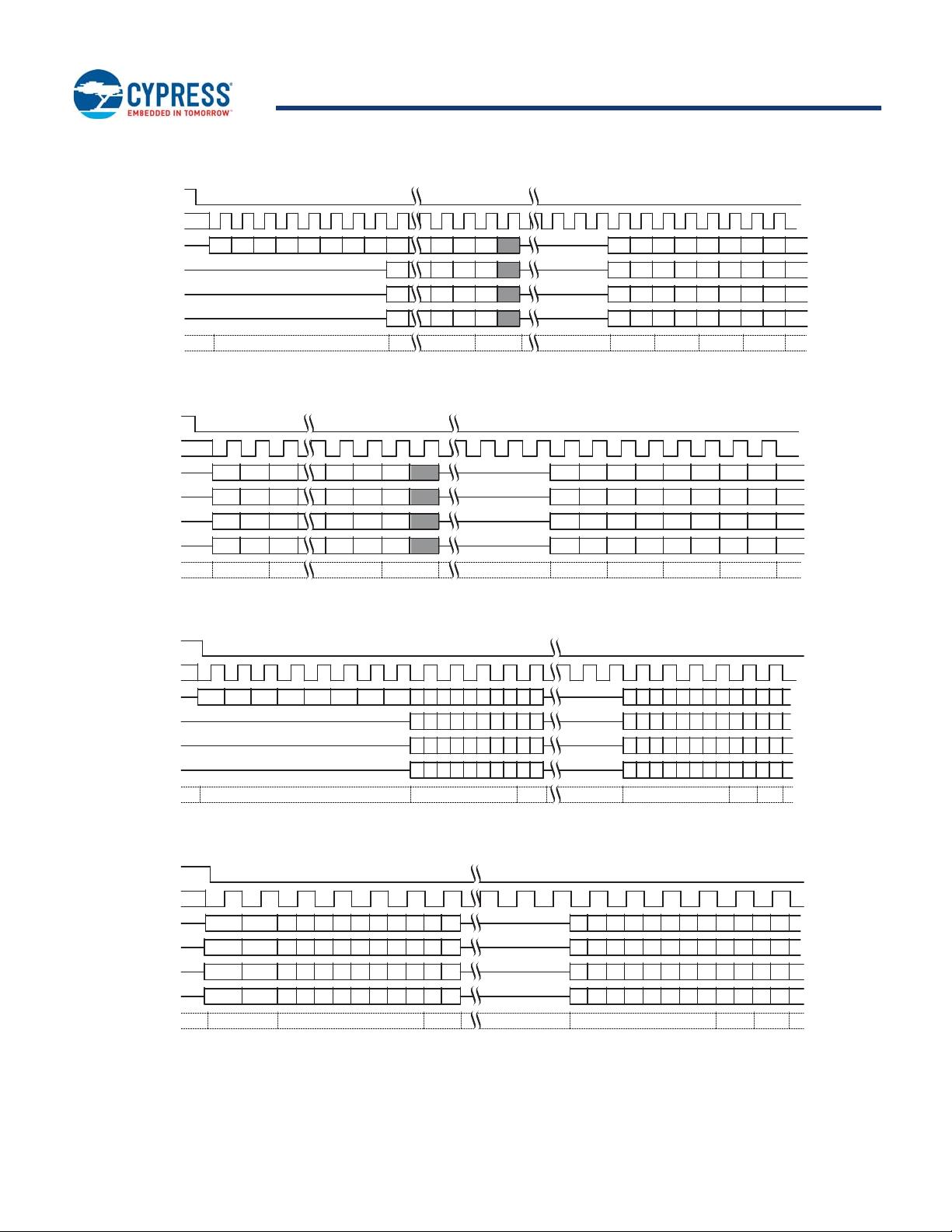

Figure 3.9 Quad I/O Command

Figure 3.10 Quad I/O Read Command in QPI Mode

Figure 3.11 DDR Quad I/O Read

Figure 3.12 DDR Quad I/O Read in QPI Mode

Additional sequence diagrams, specific to each command, are provided in Commands on page 76.

CS#

SCK

IO0

IO1

IO2

IO3

Phase

7 6 5 4 3 2 1 0 28 4 0 4 0 4 0 4 0 4 0 4 0

29 5 1 5 1 5 1 5 1 5 1 5 1

30 6 2 6 2 6 2 6 2 6 2 6 2

31 7 3 7 3 7 3 7 3 7 3 7 3

Instruction Address Mode Dummy D1 D2 D3 D4

CS#

SCK

IO0

IO1

IO2

IO3

Phase

4 0 28 4 0 4 0 4 0 4 0 4 0 4 0

5 1 29 5 1 5 1 5 1 5 1 5 1 5 1

6 2 30 6 2 6 2 6 2 6 2 6 2 6 2

7 3 31 7 3 7 3 7 3 7 3 7 3 7 3

Instruct. Address Mode Dummy D1 D2 D3 D4

CS#

SCK

IO0

IO1

IO2

IO3

Phase

7 6 5 4 3 2 1 0 28 24 20 16 12 8 4 0 4 0 7 6 5 4 3 2 1 0 4 0 4 0

29 25 21 17 13 9 5 1 5 1 7 6 5 4 3 2 1 0 5 1 5 1

30 26 22 18 14 10 6 2 6 2 7 6 5 4 3 2 1 0 6 2 6 2

31 27 23 19 15 11 7 3 7 3 7 6 5 4 3 2 1 0 7 3 7 3

Instruction Address Mode Dummy DLP D1 D2

CS#

SCK

IO0

IO1

IO2

IO3

Phase

4 0 28 24 20 16 12 8 4 0 4 0 7 6 5 4 3 2 1 0 4 0 4 0

5 1 29 25 21 17 13 9 5 1 5 1 7 6 5 4 3 2 1 0 5 1 5 1

6 2 30 26 22 18 14 10 6 2 6 2 7 6 5 4 3 2 1 0 6 2 6 2

7 3 31 27 23 19 15 11 7 3 7 3 7 6 5 4 3 2 1 0 7 3 7 3

Instruct. Address Mode Dummy DLP D1 D2

Document Number: 002-00368 Rev. *J Page 18 of 151

S25FS128S

S25FS256S

3.3 Interface States

This section describes the input and output signal levels as related to the SPI interface behavior.

Legend

Z = No driver - floating signal

HL = Host driving V

IL

HH = Host driving V

IH

HV = Either HL or HH

X = HL or HH or Z

HT = Toggling between HL and HH

ML = Memory driving V

IL

MH = Memory driving V

IH

MV = Either ML or MH

3.3.1 Power-Off

When the core supply voltage is at or below the V

CC (Low)

voltage, the device is considered to be powered off. The device does not

react to external signals, and is prevented from performing any program or erase operation.

3.3.2 Low-Power Hardware Data Protection

When V

CC

is less than V

CC (Cut-off)

the memory device will ignore commands to ensure that program and erase operations can not

start when the core supply voltage is out of the operating range.

Interface States Summary

Interface State V

CC

SCK CS#

IO3 /

RESET#

WP# / IO2 SO / IO1 SI / IO0

Power-Off <V

CC

(low) X X X X Z X

Low-Power Hardware Data Protection <V

CC

(cut-off) X X X X Z X

Power-On (Cold) Reset

≥V

CC

(min) X HH X X Z X

Hardware (Warm) Reset Non-Quad Mode

≥V

CC

(min) X X HL X Z X

Hardware (Warm) Reset Quad Mode

≥V

CC

(min) X HH HL X Z X

Interface Standby

≥V

CC

(min) X HH X X Z X

Instruction Cycle (Legacy SPI)

≥V

CC

(min) HT HL HH HV Z HV

Single Input Cycle

Host to Memory Transfer

≥V

CC

(min) HT HL HH X Z HV

Single Latency (Dummy) Cycle

≥V

CC

(min) HT HL HH X Z X

Single Output Cycle

Memory to Host Transfer

≥V

CC

(min) HT HL HH X MV X

Dual Input Cycle

Host to Memory Transfer

≥V

CC

(min) HT HL HH X HV HV

Dual Latency (Dummy) Cycle

≥V

CC

(min) HT HL HH X X X

Dual Output Cycle

Memory to Host Transfer

≥V

CC

(min) HT HL HH X MV MV

Quad Input Cycle

Host to Memory Transfer

≥V

CC

(min) HT HL HV HV HV HV

Quad Latency (Dummy) Cycle

≥V

CC

(min) HT HL X X X X

Quad Output Cycle

Memory to Host Transfer

≥V

CC

(min) HT HL MV MV MV MV

DDR Quad Input Cycle

Host to Memory Transfer

≥V

CC

(min) HT HL HV HV HV HV

DDR Latency (Dummy) Cycle

≥V

CC

(min) HT HL MV or Z MV or Z MV or Z MV or Z

DDR Quad Output Cycle

Memory to Host Transfer

≥V

CC

(min) HT HL MV MV MV MV

Document Number: 002-00368 Rev. *J Page 19 of 151

S25FS128S

S25FS256S

3.3.3 Power-On (Cold) Reset

When the core voltage supply remains at or below the V

CC (Low)

voltage for ≥ t

PD

time, then rises to ≥ V

CC (Minimum)

the device will

begin its Power-On Reset (POR) process. POR continues until the end of t

PU

. During t

PU

the device does not react to external input

signals nor drive any outputs. Following the end of t

PU

the device transitions to the Interface Standby state and can accept

commands. For additional information on POR see Power-On (Cold) Reset on page 28

3.3.4 Hardware (Warm) Reset

A configuration option is provided to allow IO3 to be used as a hardware reset input when the device is not in Quad Mode or when it

is in Quad Mode and CS# is high. When IO3 / RESET# is driven low for t

RP

time the device starts the hardware reset process. The

process continues for t

RPH

time. Following the end of both t

RPH

and the reset hold time following the rise of RESET# (t

RH

) the device

transitions to the Interface Standby state and can accept commands. For additional information on hardware reset see Reset

on page 28

3.3.5 Interface Standby

When CS# is high the SPI interface is in standby state. Inputs other than RESET# are ignored. The interface waits for the beginning

of a new command. The next interface state is Instruction Cycle when CS# goes low to begin a new command.

While in interface standby state the memory device draws standby current (I

SB

) if no embedded algorithm is in progress. If an

embedded algorithm is in progress, the related current is drawn until the end of the algorithm when the entire device returns to

standby current draw.

A Deep Power-Down (DPD) mode is supported by the FS-S family of devices. If the device has been placed in DPD mode by the

DPD (B9h) command, the interface standby current is I

DPD

. The DPD command is accepted only while the device is not performing

an embedded operation, as indicated by the Status Register-1 volatile Write In Progress (WIP) bit being cleared to zero

(SR1V[0]=0). While in DPD mode, the device ignores all commands except the Release from DPD (RES ABh) command, that will

return the device to the Interface Standby state after a delay of t

RES

.

3.3.6 Instruction Cycle (Legacy SPI Mode)

When the host drives the MSB of an instruction and CS# goes low, on the next rising edge of SCK the device captures the MSB of

the instruction that begins the new command. On each following rising edge of SCK the device captures the next lower significance

bit of the 8-bit instruction. The host keeps CS# low, and drives the Write Protect (WP#) and IO3/RESET signals as needed for the

instruction. However, WP# is only relevant during instruction cycles of a WRR or WRAR command and is otherwise ignored.

IO3/RESET# is driven high when the device is not in Quad Mode (CR1V[1] = 0) or QPI Mode (CR2V[6] = 0) and hardware reset is

not required.

Each instruction selects the address space that is operated on and the transfer format used during the remainder of the command.

The transfer format may be Single, Dual I/O, Quad I/O, or DDR Quad I/O. The expected next interface state depends on the

instruction received.

Some commands are stand alone, needing no address or data transfer to or from the memory. The host returns CS# high after the

rising edge of SCK for the eighth bit of the instruction in such commands. The next interface state in this case is Interface Standby.

3.3.7 Instruction Cycle (QPI Mode)

In QPI Mode, when CR2V[6]=1, instructions are transferred 4 bits per cycle. In this mode, instruction cycles are the same as a Quad

Input Cycle. See Quad Input Cycle - Host to Memory Transfer on page 20.

3.3.8 Single Input Cycle - Host to Memory Transfer

Several commands transfer information after the instruction on the single Serial Input (SI) signal from host to the memory device.

The host keeps RESET# high, CS# low, and drives SI as needed for the command. The memory does not drive the Serial Output

(SO) signal.

The expected next interface state depends on the instruction. Some instructions continue sending address or data to the memory

using additional Single Input Cycles. Others may transition to Single Latency, or directly to Single, Dual, or Quad Output Cycle

states.

Document Number: 002-00368 Rev. *J Page 20 of 151

S25FS128S

S25FS256S

3.3.9 Single Latency (Dummy) Cycle

Read commands may have zero to several latency cycles during which read data is read from the main flash memory array before

transfer to the host. The number of latency cycles are determined by the Latency Code in the Configuration Register (CR2V[3:0]).

During the latency cycles, the host keeps RESET# high, CS# low. The Write Protect (WP#) signal is ignored. The host may drive the

SI signal during these cycles or the host may leave SI floating. The memory does not use any data driven on SI / I/O0 or other I/O

signals during the latency cycles. The memory does not drive the Serial Output (SO) or I/O signals during the latency cycles.

The next interface state depends on the command structure i.e. the number of latency cycles, and whether the read is single, dual,

or quad width.

3.3.10 Single Output Cycle - Memory to Host Transfer

Several commands transfer information back to the host on the single Serial Output (SO) signal. The host keeps RESET# high, CS#

low. The Write Protect (WP#) signal is ignored. The memory ignores the Serial Input (SI) signal. The memory drives SO with data.

The next interface state continues to be Single Output Cycle until the host returns CS# to high ending the command.

3.3.11 Dual Input Cycle - Host to Memory Transfer

The Read Dual I/O command transfers two address or mode bits to the memory in each cycle. The host keeps RESET# high, CS#

low. The Write Protect (WP#) signal is ignored. The host drives address on SI / IO0 and SO / IO1.

The next interface state following the delivery of address and mode bits is a Dual Latency Cycle if there are latency cycles needed or

Dual Output Cycle if no latency is required.

3.3.12 Dual Latency (Dummy) Cycle

Read commands may have zero to several latency cycles during which read data is read from the main flash memory array before

transfer to the host. The number of latency cycles are determined by the Latency Code in the Configuration Register (CR2V[3:0]).

During the latency cycles, the host keeps RESET# high, CS# low. The Write Protect (WP#) signal is ignored. The host may drive the

SI / IO0 and SO / IO1 signals during these cycles or the host may leave SI / IO0 and SO / IO1 floating. The memory does not use

any data driven on SI / IO0 and SO / IO1 during the latency cycles. The host must stop driving SI / IO0 and SO / IO1 on the falling

edge at the end of the last latency cycle. It is recommended that the host stop driving them during all latency cycles so that there is

sufficient time for the host drivers to turn off before the memory begins to drive at the end of the latency cycles. This prevents driver

conflict between host and memory when the signal direction changes. The memory does not drive the SI / IO0 and SO / IO1 signals

during the latency cycles.

The next interface state following the last latency cycle is a Dual Output Cycle.

3.3.13 Dual Output Cycle - Memory to Host Transfer

The Read Dual Output and Read Dual I/O return data to the host two bits in each cycle. The host keeps RESET# high, CS# low. The

Write Protect (WP#) signal is ignored. The memory drives data on the SI / IO0 and SO / IO1 signals during the Dual Output Cycles.

The next interface state continues to be Dual Output Cycle until the host returns CS# to high ending the command.

3.3.14 Quad Input Cycle - Host to Memory Transfer

The Quad I/O Read command transfers four address or mode bits to the memory in each cycle. In QPI Mode the Quad I/O Read and

Page Program commands transfer four data bits to the memory in each cycle, including the instruction cycles. The host keeps CS#

low, and drives the IO signals.

For Quad I/O Read the next interface state following the delivery of address and mode bits is a Quad Latency Cycle if there are

latency cycles needed or Quad Output Cycle if no latency is required. For QPI Mode Page Program, the host returns CS# high

following the delivery of data to be programmed and the interface returns to standby state.

3.3.15 Quad Latency (Dummy) Cycle

Read commands may have zero to several latency cycles during which read data is read from the main flash memory array before

transfer to the host. The number of latency cycles are determined by the Latency Code in the Configuration Register (CR2V[3:0]).

During the latency cycles, the host keeps CS# low. The host may drive the IO signals during these cycles or the host may leave the

剩余150页未读,继续阅读

carl_wang_123

- 粉丝: 58

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- Java+Servlet+API说明文档

- spring中文版教程

- Discrete time model and algorithm for container yard crane scheduling.pdf

- ARM公司的AMBA总线规范

- C++Builder6.0界面实例开发

- C++Programming

- 我的操作系统实验-银行家算法

- java字符反转代码

- Linux初学者入门优秀教程

- 手机号码和email校验的Js代码

- NAND FLASH PMON烧写指南

- 09版三级网络技术上级100题

- voip详细原理说明

- 软件集成测试工作指南

- JAVASCRIPT真经

- SAP 常用数据表 列表 开发人员的必备资料哦

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功