Verilog实现LCD液晶显示实验与代码详解

本篇资源是关于PLD实验的详细报告,主要涉及LCD液晶显示技术在Verilog语言中的应用。实验者利用Xilinx SPARTAN-6 FPGA实验箱和ISE V14.7软件环境,旨在通过实践学习Verilog编程以及如何设计和控制LCD12864这种128列×64行的液晶显示模块。

首先,实验的主要目标包括理解并掌握Verilog语言的设计思路,熟悉硬件平台,以及能够独立在软件环境中完成实验设计。具体要求是通过LCD显示实验,在LCD屏幕上显示特定的文本,如学号和姓名,以实践基本的数据传输和控制。

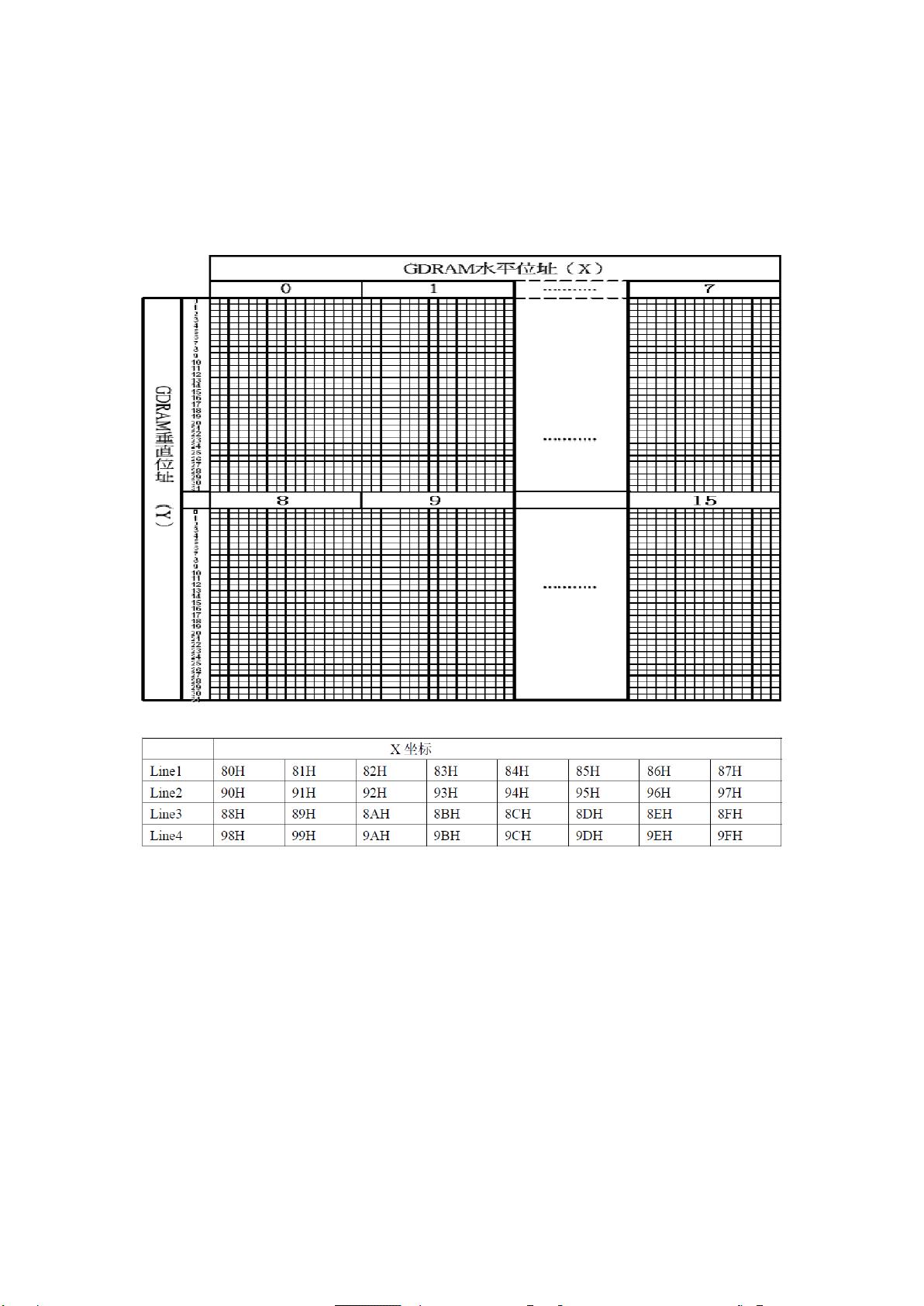

DM12864M模块是一种汉字图形点阵液晶显示模块,支持中文汉字和字符显示,以及高级功能如自定义字符和背光控制。模块的关键技术参数如电源范围、显示内容、色彩和角度都做了详细介绍。此外,还提供了模块的外形尺寸、引脚说明以及显示坐标关系,对于理解液晶屏的工作原理至关重要。

实验的焦点在于接口时序设计,尤其是与微处理器(MPU)的并行通信。实验者根据指导材料设计了RS(寄存器选择)、R/W(读写)和E(使能)这三个控制信号的逻辑,确保在写入数据时正确设置RS和R/W,同时让E信号与液晶时钟同步。Verilog代码示例展示了这些信号的实现细节。

这个资源为学习者提供了一个实际操作的范例,涵盖了从理论知识到硬件接线,再到软件编程的完整流程,对想要深入理解FPGA与LCD交互的同学具有很高的参考价值。通过阅读和实践这份报告,读者可以提升自己的数字逻辑设计和嵌入式系统开发能力。

相关推荐

190 浏览量

drjiachen

- 粉丝: 172

最新资源

- 下载JDK8 64位Windows版安装包

- VB实现的学生公寓宿舍管理系统详细解析

- YeetSTM32K开发板:STM32新成员特性解读

- C语言实现链表操作源码分享

- 牙医门户MERN应用开发流程与构建指南

- Qt图形界面中实现鼠标拖动与缩放功能

- Discuz!实时股票指数滚动代码插件发布

- Matlab全系列教程:轻松入门到精通

- 全国电子设计大赛G题解析:空地协同智能消防系统

- Java实现的学生管理系统详细介绍

- Python Discord猎户座机器人项目实战解析

- Win10下libssh2库1.7.0版本编译与资源分解析

- 掌握Python基础:wcl-basic-python项目示例解析

- Matlab至C语言转换:MLP编码器实战项目源码解析

- 易优CMS模板分享:全套网站解决方案

- Delphi xe中文版ASqlite3问题修复及测试