EDA技术与ASIC、FPGA设计:VHDL综合解析

需积分: 1 134 浏览量

更新于2024-07-27

收藏 177KB DOC 举报

"EDA技术, ASIC设计, FPGA开发, VHDL, 综合, 自顶向下设计"

EDA(Electronic Design Automation)技术是电子设计自动化的核心工具,它涵盖了从电路概念到物理实现的整个设计流程。在ASIC(Application-Specific Integrated Circuit)设计中,EDA技术被用来设计和验证高度定制的集成电路,而FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)是实现这些设计的常用平台,它们属于可编程ASIC,能够快速原型验证和部署。EDA技术将软硬件设计紧密结合,推动了SoC(System on Chip)的发展,即在一个芯片上集成完整的系统。

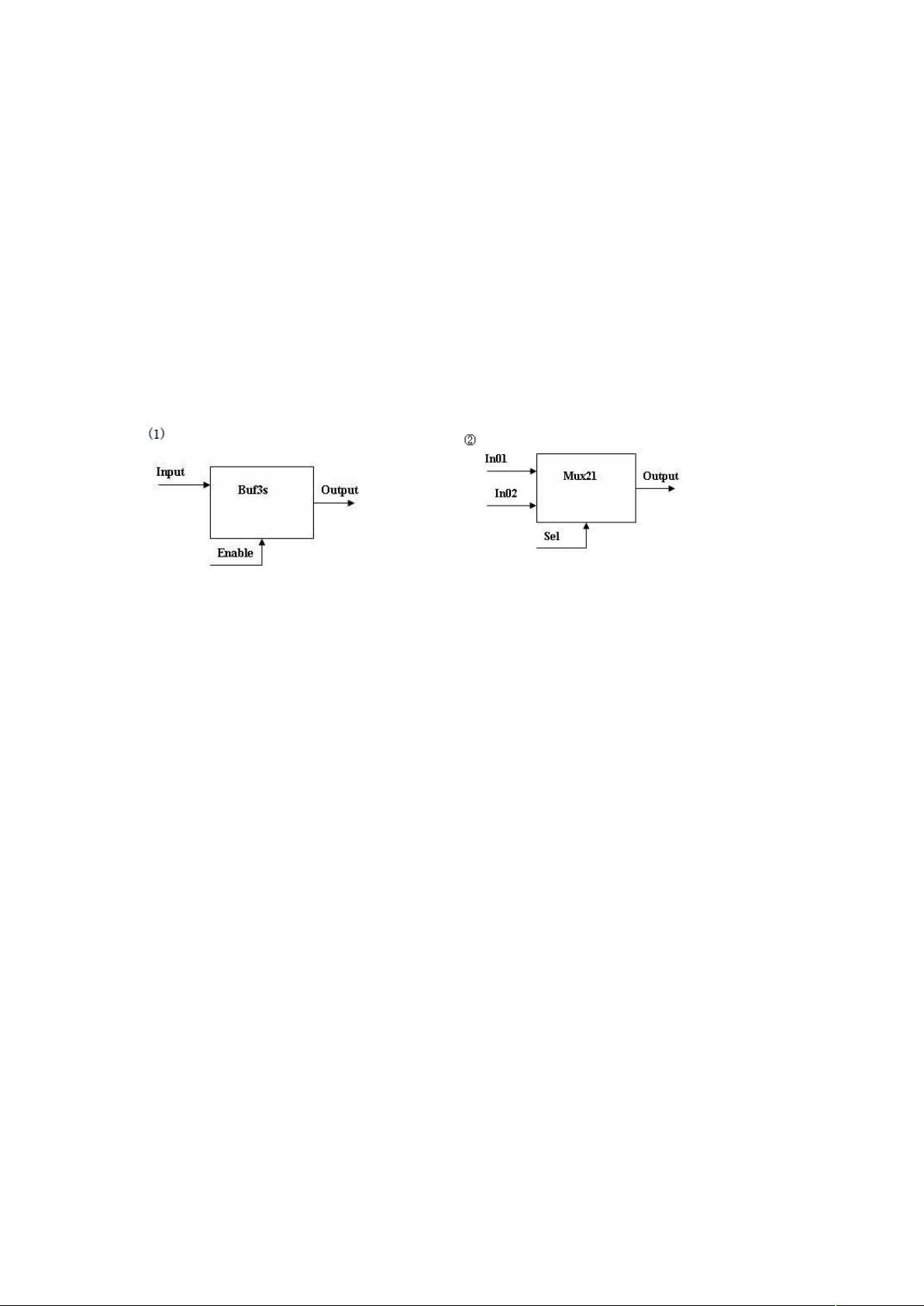

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,与传统的软件描述语言不同,VHDL不仅能够描述电路的行为,还可以描述其结构。它的特点是代码具有相对独立性,不依赖于特定硬件环境,可以被综合器转化为底层电路结构,这个过程包含了能动性和创造性,可以根据设计库、工艺库和约束条件生成最优的电路实现。综合是EDA流程中的关键步骤,分为多种类型,包括行为综合、逻辑综合等,将高层次的设计转化为可实现的硬件结构。

在电子设计自动化中,综合处于核心地位,因为它连接了高级设计概念和实际的物理实现。综合器需要考虑工艺库信息、约束条件等,将VHDL程序转化为电路实现的网表,对于性能、面积和功耗的优化至关重要。

自顶向下的设计方法是EDA技术中的一种重要设计策略。这种方法将复杂的设计分解为多个子模块,自顶向下逐层细化,使得设计的管理和复用更加高效,同时便于早期发现设计问题,提高设计的可维护性和可重用性。通过这种方式,设计者可以先从系统级别的概念开始,然后逐步深入到每个组件的细节,从而实现大规模的电子系统设计。

297 浏览量

2023-02-27 上传

514 浏览量

302 浏览量

2022-06-20 上传

2022-06-20 上传

210 浏览量

@Willem

- 粉丝: 0

最新资源

- 多技术领域源码集锦:园林绿化官网企业项目

- 定制特色井字游戏Tic Tac Toe开源发布

- TechNowHorse:Python 3编写的跨平台RAT生成器

- VB.NET实现程序自动更新的模块设计与应用

- ImportREC:强大输入表修复工具的介绍

- 高效处理文件名后缀:脚本批量添加与移除教程

- 乐phone 3GW100体验版ROM深度解析与优化

- Rust打造的cursive_table_view终端UI组件

- 安装Oracle必备组件libaio-devel-0.3.105-2下载

- 探索认知语言连接AI的开源实践

- 微软SAPI5.4实现的TTSApp语音合成软件教程

- 双侧布局日历与时间显示技术解析

- Vue与Echarts结合实现H5数据可视化

- KataSuperHeroesKotlin:提升Android开发者的Kotlin UI测试技能

- 正方安卓成绩查询系统:轻松获取课程与成绩

- 微信小程序在保险行业的应用设计与开发资源包