运放驱动容性负载:问题、影响与解决策略

84 浏览量

更新于2024-08-31

1

收藏 346KB PDF 举报

在电子设计中,运算放大器(Op-Amp)驱动容性负载是一个不可忽视的问题,尤其是在信号传输线路如同轴电缆中,电容效应往往作为意外的负载出现在电路中。考虑驱动容性负载的原因在于,尽管在大多数情况下,电路设计者并不主动选择这样的负载,但它确实会影响放大器的性能。

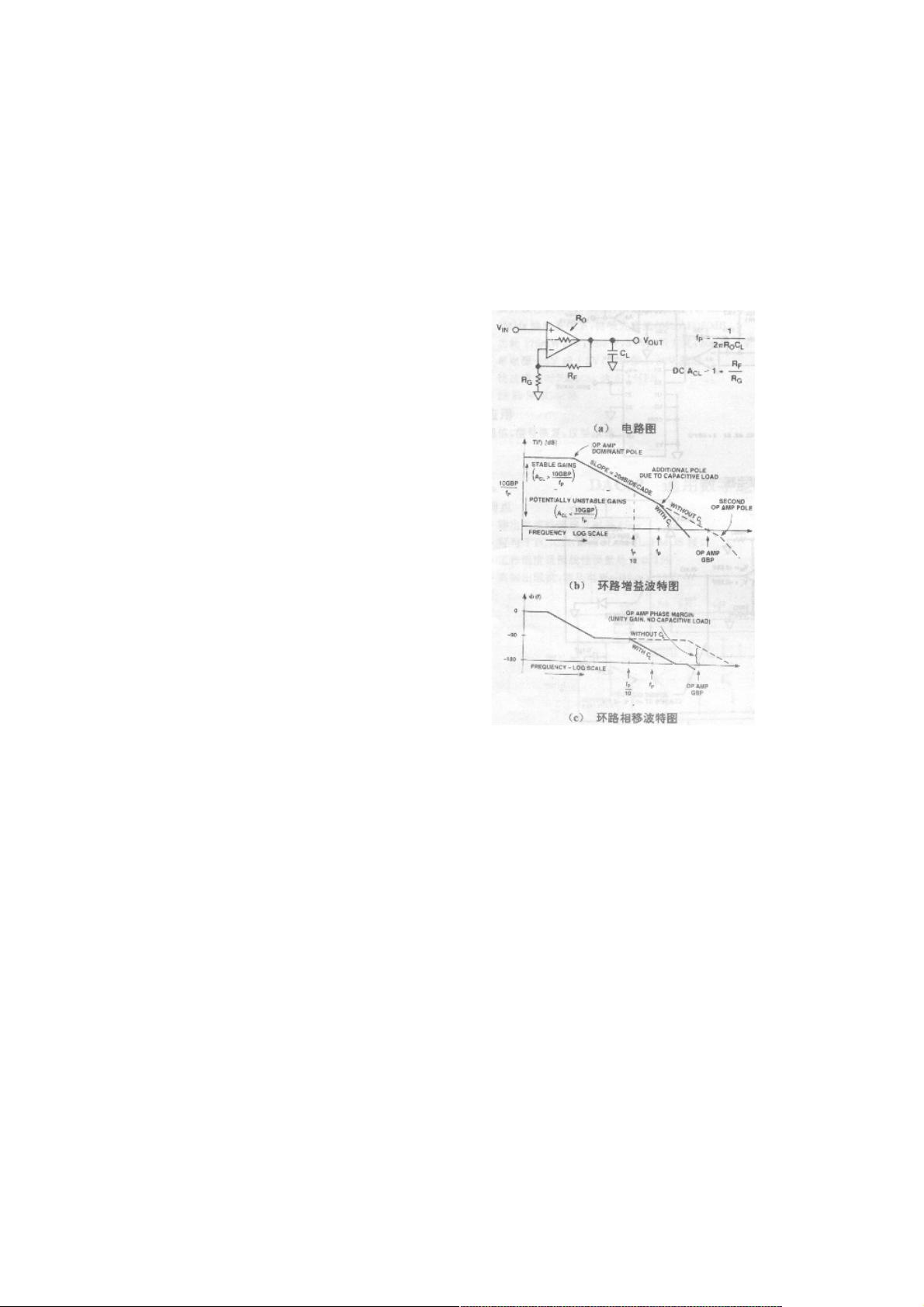

首先,容性负载会对运放的工作频率范围产生影响。运放可以近似看作一个振荡器,其内部的输出电阻(RO)与容性负载结合时,会在放大器的传递函数中引入额外的极点。这些极点导致幅频特性斜率变陡,使得电路的稳定性受到威胁。例如,如果开环增益和反馈衰减之和超过1,或者在某个工作频率下,环路相移超过-180°,就可能出现振荡现象。

运放的闭环带宽,即GBP除以闭环增益(ACL),是评估稳定性的重要参数。相位裕度是另一个关键概念,它衡量了系统能承受的容许相移而不至于失稳。如果相位裕度低于45°,可能会出现响应异常,如频响“尖峰”、阶跃响应中的过冲或“振铃”。为了确保稳定,容性负载产生的附加极点应高于闭环带宽至少10倍。

处理容性负载的方法包括查阅运放的数据手册,其中会列出“容性负载驱动能力”的指标,以及“小信号过冲与容性负载关系曲线”。过冲与负载电容成指数关系增长,当过冲达到100%时,运放就可能变得不稳定。因此,设计师应尽可能减小过冲,确保它在安全范围内,并考虑到增益的影响。例如,如果在低增益下,VFA可以稳定驱动100pF的容性负载,随着增益的提升,该能力会相应增强。

在实际设计中,选择合适的运放型号和调整电路参数以补偿容性负载的影响至关重要。这可能涉及到选择具有更强容性负载驱动能力的运放,或者通过电路设计手段(如串联电阻)来降低负载的等效电容,从而保持系统的稳定性。理解并妥善处理容性负载对运算放大器性能的影响是电子工程师必须掌握的关键技能。

220 浏览量

103 浏览量

127 浏览量

167 浏览量

2021-09-22 上传

647 浏览量

2021-02-03 上传

2021-02-03 上传

2021-02-03 上传

weixin_38631049

- 粉丝: 6

最新资源

- ASP.NET集成支付宝即时到账支付流程详解

- C++递推法在解决三道经典算法问题中的应用

- Qt_MARCHING_CUBES算法在面绘制中的应用

- 传感器原理与应用课程习题解答指南

- 乐高FLL2017-2018任务挑战解析:饮水思源

- Jquery Ui婚礼祝福特效:经典30款小型设计

- 紧急定位伴侣:蓝光文字的位置追踪功能

- MATLAB神经网络实用案例分析大全

- Masm611: 安全高效的汇编语言调试工具

- 3DCurator:彩色木雕CT数据的3D可视化解决方案

- 聊天留言网站开发项目全套资源下载

- 触摸屏适用的左右循环拖动展示技术

- 新型不连续导电模式V_2控制Buck变换器研究分析

- 用户自定义JavaScript脚本集合分享

- 易语言实现非主流方式获取网关IP源码教程

- 微信跳一跳小程序前端源码解析