Virtex-4 FPGA实现高速SPI接口:HSC-ADC-EVALC平台详解

FPGA实现SPI总线是一种常见的技术应用,特别是在处理高速数据传输和外设接口方面。本文讨论的焦点是ADI公司的HSC-ADC-EVALC高速转换器评估平台,它基于Xilinx Virtex-4 FPGA(XC4VFX20-10FFG672C),这是一款强大的可编程逻辑器件,支持多种接口标准,包括SPI(Serial Peripheral Interface)。SPI作为一种串行同步通信协议,由主设备和多个从设备组成,通过SDI(串行数据输入)、SDO(串行数据输出)、SCLK(串行移位时钟)和CS(从使能信号)四个信号线进行数据交换。

HSC-ADC-EVALC平台集成了高性能ADC,支持1.8V、2.5V和3.3V CMOS以及LVDS接口,能够处理高达644MSPS SDR和800MSPS DDR的数据速率,适应18位多路ADC的实时分析任务,如FFT(快速傅立叶变换)和SNR(信噪比)、SINAD(信号与噪声和干扰之比)、SFDR(相位噪声谱密度)等指标的测量。

该平台的核心设计实现了如下关键功能:

1. **8-bit CPU接口与SPI接口通信**:允许CPU和其他系统组件之间无缝连接,支持不同数据类型和长度的传输。

2. **配置控制**:通过CPU接口可以灵活地配置和管理SPI接口的工作模式、波特率和工作方式。

3. **主从模式与多波特率支持**:允许用户选择不同的工作模式,适应不同应用场景下的数据交互。

4. **工作模式和方式选择**:提供了灵活的接口控制,可根据需要调整接口操作。

5. **全双工通信**:SPI支持同时进行数据的发送和接收,提高了数据传输效率。

6. **1-bit输入输出**:允许单个比特的数据交换,进一步扩展了接口的灵活性。

在电路设计上,平台包括控制寄存器(SPI_CTRL)、内部时钟(SPI_CLK)和数据移位寄存器(SPI_BUF)等核心模块。SPI接口的设计没有内置的应答机制,这意味着无法检测数据传输的错误或丢失,因此在使用时需要注意数据完整性。

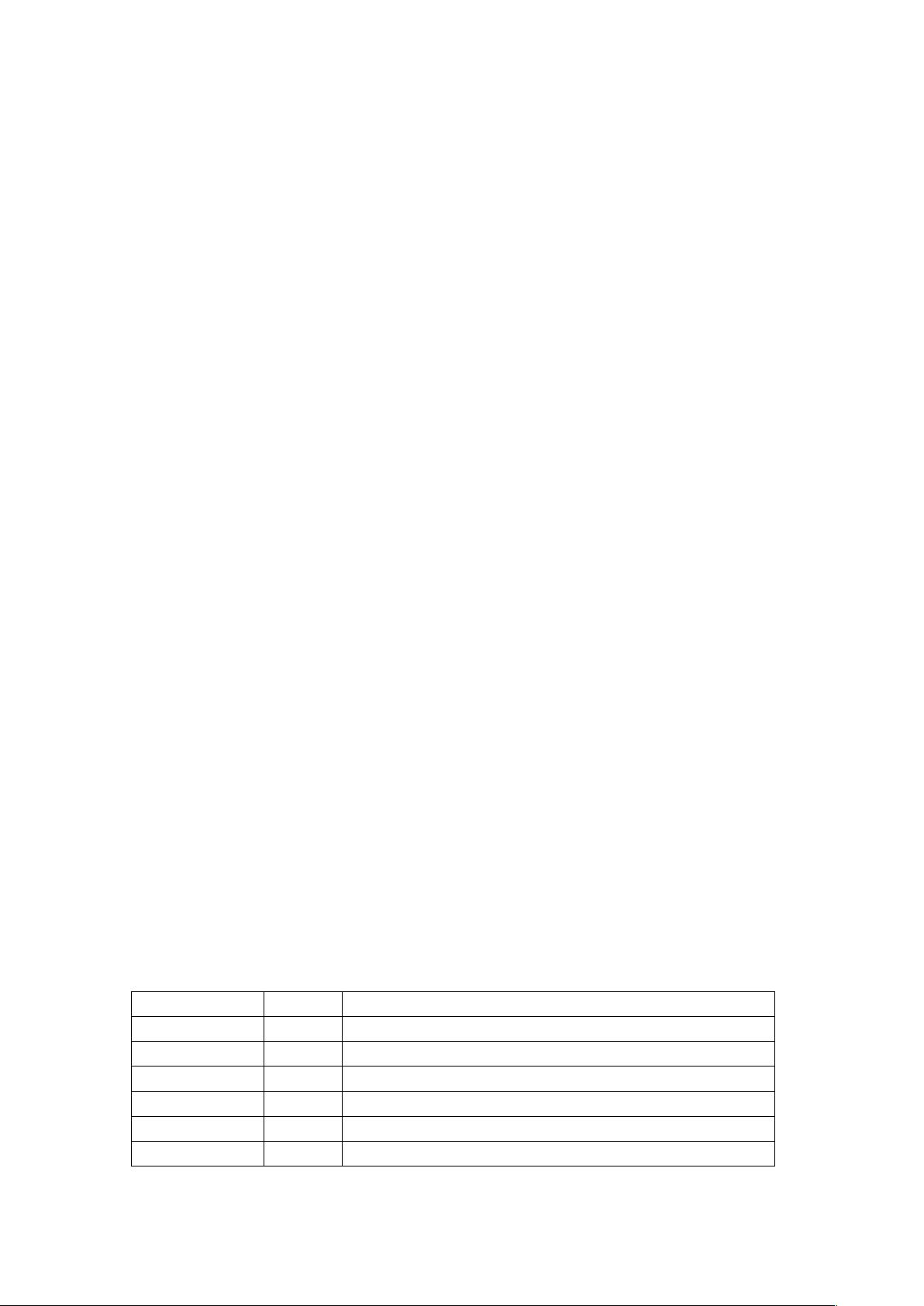

表1列出了平台上的主要接口,如系统时钟clk和双向8-bit数据总线data[7:0],以及地址线addr[11:0]用于配置和选择特定功能。整体来说,这个设计是一个综合的解决方案,结合了高性能硬件和灵活的软件接口,适用于需要高速SPI通信和精确数据处理的系统设计。

5067 浏览量

367 浏览量

567 浏览量

2021-07-13 上传

2022-09-24 上传

196 浏览量

kaiwang289

- 粉丝: 0

最新资源

- Sybase15系统管理指南:AdaptiveServerEnterprise中文手册

- Sybase15 AdaptiveServerEnterprise 中文系统表手册

- Eclipse IDE详解:从基础到高级设置

- 深入学习Java:Bruce Eckel的第四版思维之书

- Eclipse整合开发工具基础教程详解

- NIOS II 开发教程:从用户指令到DMA与UART实战

- 操作系统的LRU页面置换算法实现

- STL实战指南:提升编程效率与应对挑战

- TMS320C54XX DSP硬件结构与设计解析

- 自编数据结构文本编辑器实现与错误修正

- VC++6.0实现密码学大数加减乘除源代码示例

- Java贪吃蛇游戏实现:SnakeGame.java代码解析

- 适应性外包发展:寻找最合适的技术与策略

- Libsvm与Matlab集成:教程与路径设置详解

- Oracle 10g 数据库基础概念详解

- S3C6410 RISC Microprocessor User's Manual