FPGA状态机设计:摩尔与米勒状态机解析

版权申诉

"FPGA状态机的设计与编码方法"

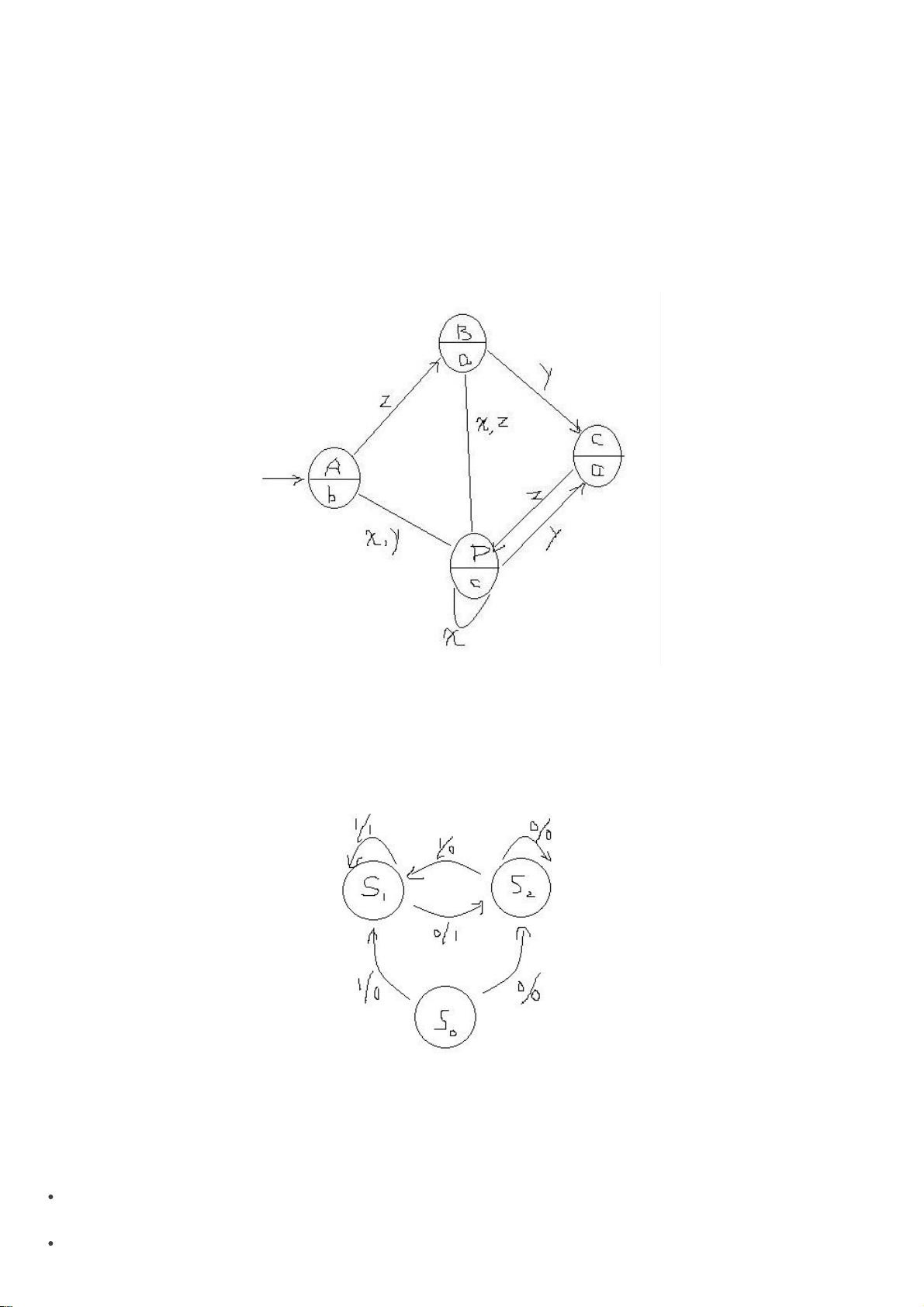

在FPGA开发中,状态机是一种核心的设计元素,用于实现数字系统的顺序控制逻辑。主要存在两种类型的状态机:摩尔(Moore)状态机和米勒(Mealy)状态机。

1. 摩尔状态机:

摩尔状态机的特点是其输出仅取决于当前状态,与输入无关。这意味着在状态图中,每个状态节点都有一个或多个输出信号。这种设计使得输出的变化发生在状态切换的同一时刻,即在时钟上升沿后。

2. 米勒状态机:

米勒状态机则不同,它的输出不仅与当前状态有关,还与输入信号有关。因此,状态图中的每条转移边通常会包含输入和输出信息。这意味着输出可能在输入改变时即时响应,而不必等待下一个时钟周期。

3. 状态编码:

状态编码是表示状态机内部状态的方式,常见的编码有三种:

- 二进制码(Binary码):这是一种连续编码方式,码元值连续变化,例如S0=3'd0, S1=3'd1, S2=3'd2, S3=3'd3。

- 格雷码(Gray码):相邻码元之间只有一个位不同,有利于减少转换过程中的错误,如S0=3'b000, S1=3'b001, S2=3'b011, S3=3'b010。二进制码与格雷码之间可以通过异或操作相互转换。

- 独热码(One-hot码):每个状态只有一个位为1,其余位为0,如S0=3'b001, S1=3'b010, S2=3'b100。独热码在状态比较时只需要比较一位,简化译码逻辑,但可能会占用更多的触发器资源。

4. 编码选择:

- 二进制码和格雷码在使用较少的触发器的同时,可能会消耗更多的组合逻辑资源。

- 独热码虽然在状态比较时具有优势,但在表示相同数量的状态时,可能需要更多的触发器。

在CPLD(复杂可编程逻辑器件)中,由于其丰富的组合逻辑资源,常选用二进制码或格雷码。而在FPGA(现场可编程门阵列)中,由于其更丰富的触发器资源,独热码编码更为常见。但这不是绝对的规则,小型设计(状态数小于4)或特定需求情况下,也可以在FPGA中使用二进制编码,或者在CPLD中使用独热编码。

选择哪种状态机类型和编码方式取决于具体的设计需求,包括资源利用率、速度、错误容错能力以及系统复杂性等因素。在实际应用中,开发者需要权衡这些因素来优化设计。

2022-04-22 上传

2022-04-22 上传

2022-04-22 上传

2022-04-22 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2022-04-22 上传

2021-07-13 上传

_webkit

- 粉丝: 30

- 资源: 1万+

最新资源

- 新代数控API接口实现CNC数据采集技术解析

- Java版Window任务管理器的设计与实现

- 响应式网页模板及前端源码合集:HTML、CSS、JS与H5

- 可爱贪吃蛇动画特效的Canvas实现教程

- 微信小程序婚礼邀请函教程

- SOCR UCLA WebGis修改:整合世界银行数据

- BUPT计网课程设计:实现具有中继转发功能的DNS服务器

- C# Winform记事本工具开发教程与功能介绍

- 移动端自适应H5网页模板与前端源码包

- Logadm日志管理工具:创建与删除日志条目的详细指南

- 双日记微信小程序开源项目-百度地图集成

- ThreeJS天空盒素材集锦 35+ 优质效果

- 百度地图Java源码深度解析:GoogleDapper中文翻译与应用

- Linux系统调查工具:BashScripts脚本集合

- Kubernetes v1.20 完整二进制安装指南与脚本

- 百度地图开发java源码-KSYMediaPlayerKit_Android库更新与使用说明