FPGA驱动的图像字符叠加器设计与实现

需积分: 0 18 浏览量

更新于2024-08-05

收藏 276KB PDF 举报

本文主要探讨了基于现场可编程门阵列(FPGA)的图像字符叠加器的设计。视频字符叠加器是一种重要的视频处理设备,它能够在电视屏幕的特定位置同时显示图像信号和用户定义的字符信息,如文字、图形或数字等。这项技术在信息显示、广告投放、实时数据展示等领域有广泛应用。

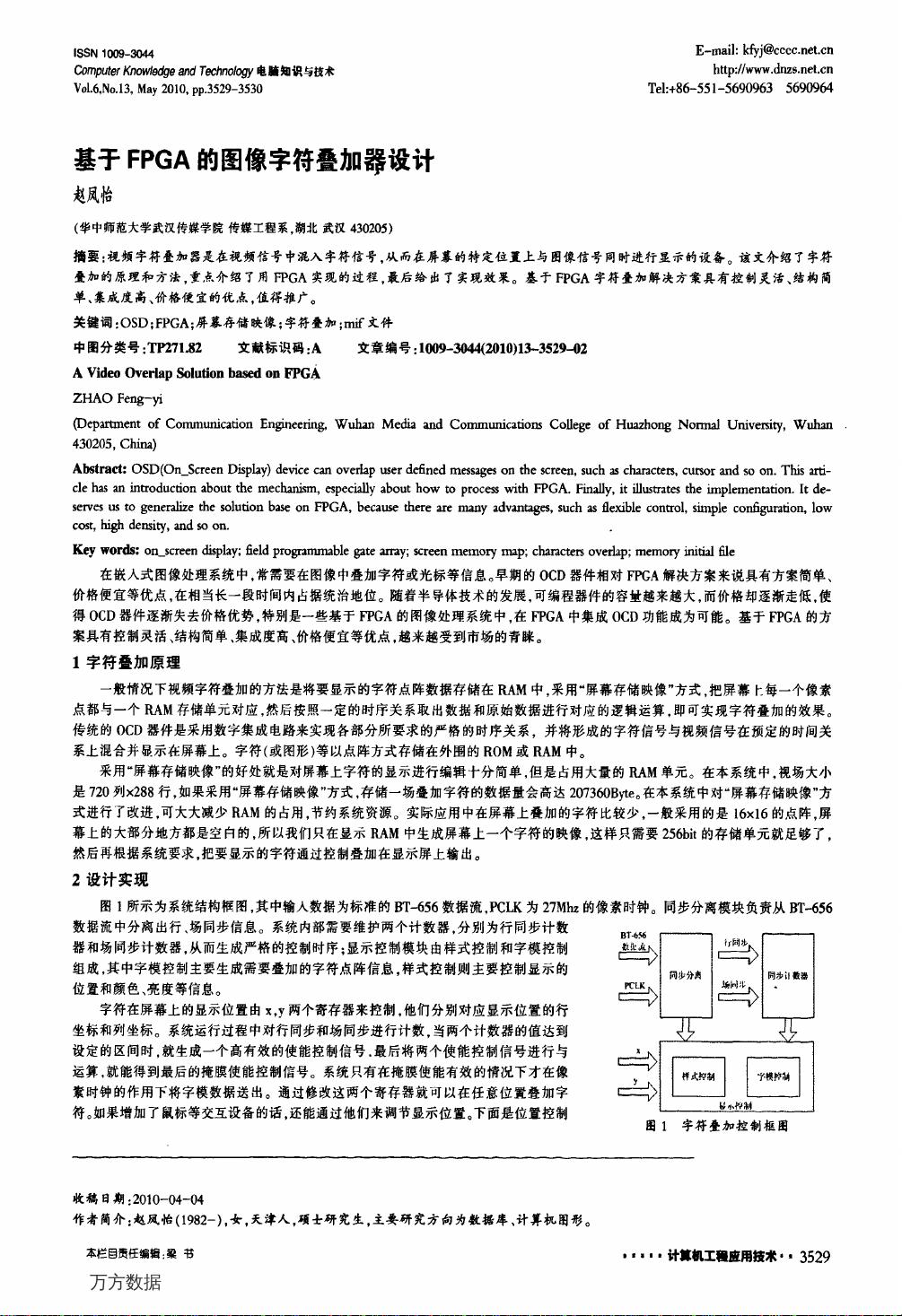

文章首先介绍了字符叠加的基本原理,即通过混合视频信号和字符信号,实现字符与图像的同步显示。字符叠加器通常包括字符生成、传输和混合三个关键步骤,其中字符生成可能涉及到文本处理、图形生成等,传输则涉及数据的高效传输,混合则是将字符信号精确地嵌入到视频帧中。

作者着重讲述了如何利用FPGA来实现这一过程。FPGA作为可编程硬件平台,其并行处理能力和灵活性使得它成为理想的选择。FPGA可以设计成专用集成电路,针对字符叠加器的功能进行定制,能够实现高速处理、低延迟以及高度的资源利用率。FPGA的结构简单,易于编程和修改,而且由于其高集成度,可以减少外部组件,降低系统成本。

文中详细阐述了基于FPGA的字符叠加器设计流程,包括硬件设计、软件编程和调试环节,可能涉及到了Verilog或 VHDL等高级硬件描述语言。此外,文章还可能讨论了如何优化存储映像,以提高字符的显示质量和响应速度。

最后,作者展示了基于FPGA字符叠加器的实际应用效果,证明了其在控制灵活性、性能和成本上的优势,认为这种解决方案具有很高的实用价值和推广潜力。总结来说,这篇文章提供了一个实用的FPGA技术在视频字符叠加器中的应用案例,对于那些寻求高效、低成本字符叠加解决方案的工程师和技术人员具有重要的参考价值。

2021-07-07 上传

2023-01-18 上传

点击了解资源详情

2023-09-27 上传

2021-09-25 上传

2014-05-10 上传

2020-08-26 上传

2023-04-28 上传

杜拉拉到杜拉拉

- 粉丝: 26

- 资源: 325

最新资源

- matlab解压代码-RiderID:“使用横向力扰动测试骑自行车的骑手控制识别”中自行车骑手控制系统识别的源代码,Schwab、deLang

- 24C16.rar_微处理器开发_C/C++_

- 第6章+信号处理电路-教程与笔记习题

- HTML网站源码-室内家居建筑设计响应式网页模板-适配移动端&PC端.zip

- 基于TV-Nesterov算法的医学图像去噪算法matlab仿真+仿真录像

- 电子工程物理基础v1.0(4)-教程与笔记习题

- 网页文章采集工具-易语言

- 【WordPress插件】2022年最新版完整功能demo+插件.zip

- you-win:一个友好的游戏库,供以前可能使用过Scratch的怪异人群使用

- 基于html5 canvas绘制彩色浮动的粒子动画特效源码.zip

- mems.rar_C/C++_

- seirs_SEIRS_SEIRS仿真代码_

- bryhlee.github.io:Bryson Lee(bryhlee)的个人网站

- HTML网站源码-休闲旅行商务响应式网页模板-适配移动端&PC端.zip

- matlab解压代码-XVFI:XVFI的官方存储库

- VB+ACCESS自动组卷系统(源代码+系统).rar