高速电路设计中的传输线效应与信号完整性关键问题探讨

132 浏览量

更新于2024-09-02

收藏 303KB PDF 举报

高速电路传输线效应和信号完整性问题在现代电子系统设计中日益重要,尤其是在工作频率达到50MHz乃至100MHz以上的高频率电路中。随着系统复杂性和集成度的提升,电子设计师面临的挑战也随之增加。以下是关于这些问题的主要知识点:

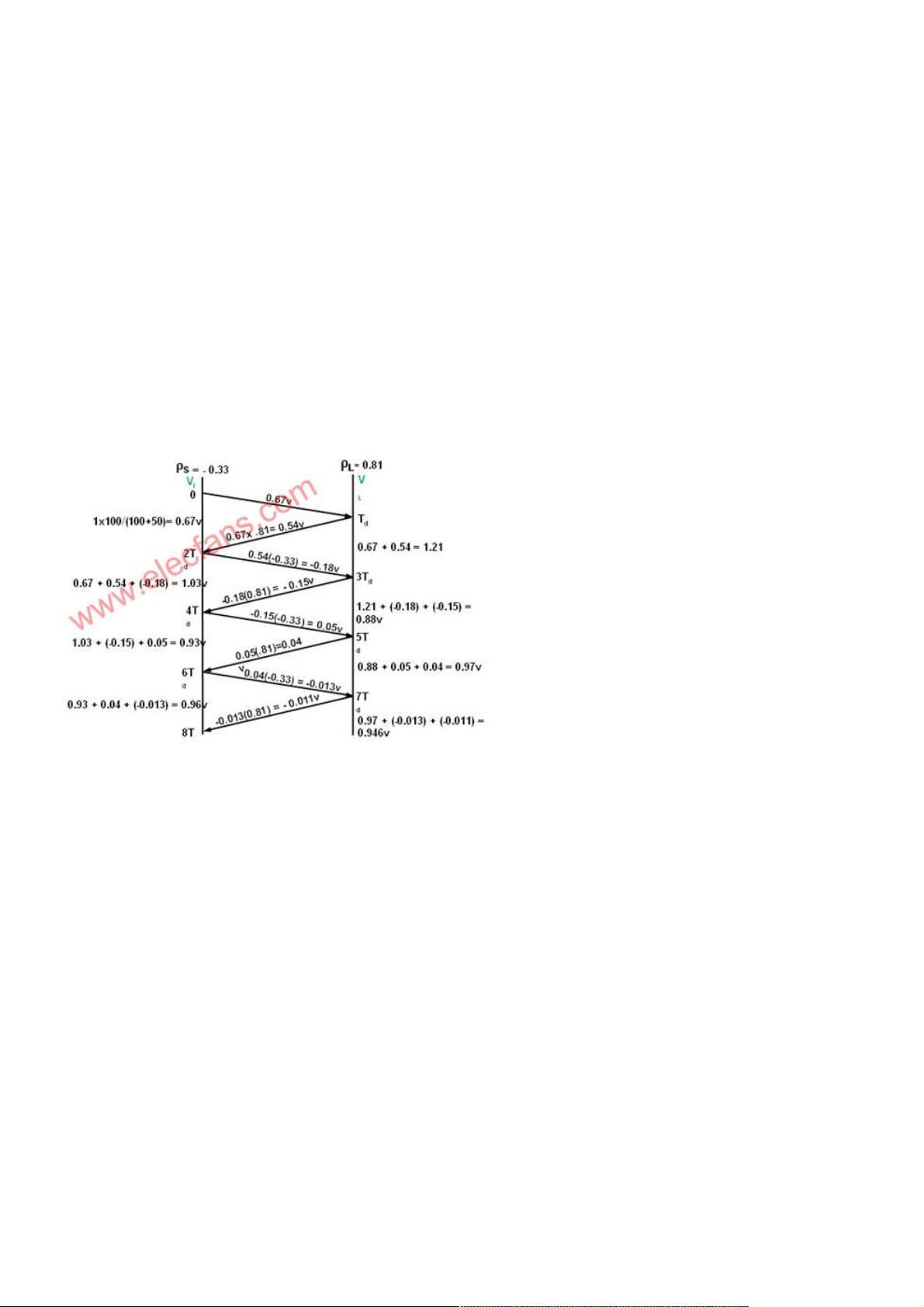

1. **反射信号 (Reflections)**:

当电路中的信号线未正确终止(即终端匹配不足)时,信号会在到达接收端前反射回源端,导致信号失真。反射的主要成因包括线路过长、终端阻抗不匹配、过量电容或电感等。解决方法是确保走线末端的适当终端配置。

2. **延迟与时序错误 (Delays and Timing Errors)**:

高速信号在传输过程中,如果信号在逻辑电平转换期间存在延迟,可能导致时序错误和电路功能紊乱。设计者需要考虑信号最长路径上的最大延迟,并进行合理的布线和时序分析。

3. **过冲 (Overshoot)**:

过冲是由信号传输速度过快或线路过长引起的。即使接收端通常有输入保护措施,过高的过冲电压仍可能超出元件的规格,造成元器件损坏。为了减小过冲,应优化信号速率和走线长度,同时提供适当的过冲抑制电路。

4. **串扰 (Coupling)**:

信号线间的电磁耦合会导致邻近信号线上的噪声或信号干扰。尤其在近距离和小线间距条件下,异步信号和时钟信号容易受到严重影响。通过合理布局、使用屏蔽层或隔离信号线可以减少串扰。

5. **电磁辐射 (Electromagnetic Interference, EMI)**:

高速电路在工作时会产生电磁辐射,可能干扰周围的电子设备。电磁干扰源于工作频率过高和布局布线不当。为了控制EMI,设计师需遵循辐射规范,使用EMI滤波器和合理布局,同时借助昂贵的EMI仿真工具来评估和优化设计。

总结来说,高速电路设计不仅要求电子系统设计师具备深入理解传输线行为的能力,还要关注信号完整性问题,通过优化设计策略和使用仿真工具来减少反射、延迟、过冲和电磁辐射,以确保系统的可靠性和互操作性。

点击了解资源详情

2021-01-19 上传

2020-08-27 上传

2020-11-11 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38663837

- 粉丝: 4

- 资源: 946

最新资源

- C++ Qt影院票务系统源码发布,代码稳定,高分毕业设计首选

- 纯CSS3实现逼真火焰手提灯动画效果

- Java编程基础课后练习答案解析

- typescript-atomizer: Atom 插件实现 TypeScript 语言与工具支持

- 51单片机项目源码分享:课程设计与毕设实践

- Qt画图程序实战:多文档与单文档示例解析

- 全屏H5圆圈缩放矩阵动画背景特效实现

- C#实现的手机触摸板服务端应用

- 数据结构与算法学习资源压缩包介绍

- stream-notifier: 简化Node.js流错误与成功通知方案

- 网页表格选择导出Excel的jQuery实例教程

- Prj19购物车系统项目压缩包解析

- 数据结构与算法学习实践指南

- Qt5实现A*寻路算法:结合C++和GUI

- terser-brunch:现代JavaScript文件压缩工具

- 掌握Power BI导出明细数据的操作指南