OPB总线仲裁器的RTL设计与FPGA实现分析

81 浏览量

更新于2024-08-31

1

收藏 271KB PDF 举报

"EDA/PLD中的OPB总线仲裁器的RTL设计与FPGA实现"

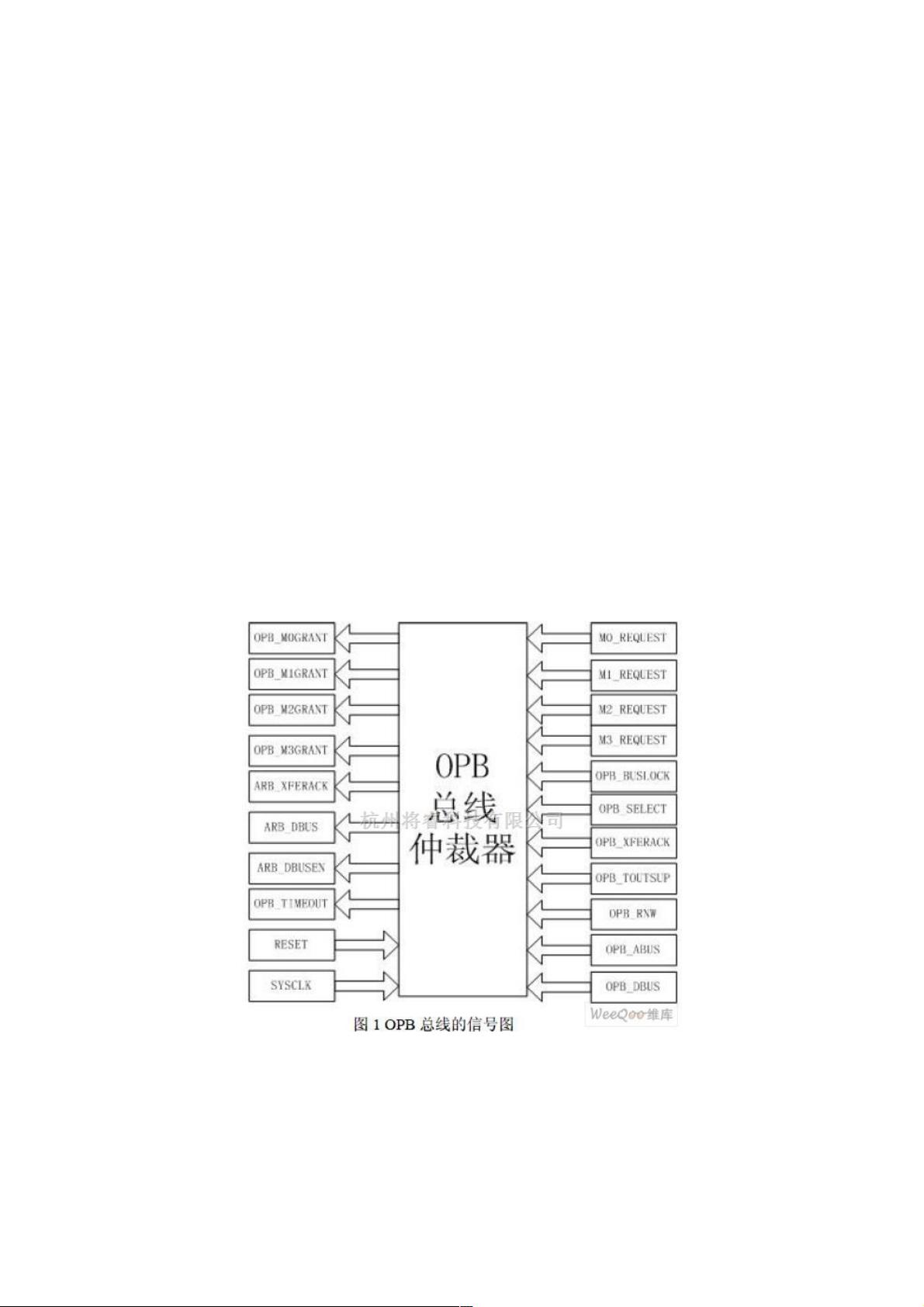

在嵌入式系统和SoC(System on Chip)设计中,OPB(On-Chip Peripheral Bus)总线是一种重要的互联架构,用于连接处理器内核与外围设备。随着SoC设计技术的进步,对高效、标准化的互连方案的需求日益增长。CoreConnect总线架构应运而生,它包括三层总线:PLB(Processor Local Bus)、OPB和DCR(Device Control Register)。OPB总线专门设计用于慢速数据率设备,如UART和GPIO,以实现这些设备与处理器的有效通信。

OPB总线仲裁器是确保多个主设备公平、高效地访问总线的关键组件。本文深入探讨了OPB总线仲裁器的信号处理和仲裁原理,并在Quartus II 8.0开发环境中,利用Verilog HDL进行了RTL(Register Transfer Level)级别的硬件描述。仲裁器设计采用了两种不同的算法:固定优先级算法和LRU(Least Recently Used)算法。固定优先级算法根据预设的优先级顺序分配总线使用权,而LRU算法则基于最近使用频率来决定资源分配,通常能够提供更好的资源利用率。

在Verilog HDL中对这两种算法进行硬件建模后,将设计在FPGA(Field-Programmable Gate Array)上实现。通过仿真和综合,验证了这两种算法在RTL级和网表级的正确性,确保了设计的可靠性。形式验证的通过是设计验证的重要步骤,它能确保设计在实际硬件上运行时的预期行为。

OPB总线仲裁器的设计是一个复杂的过程,需要考虑的因素包括仲裁策略、性能优化以及功耗管理。固定优先级算法简单直观,但可能产生某些主设备长期无法获得总线使用权的情况;而LRU算法虽然相对复杂,但能更好地平衡各设备的访问需求。对比这两种算法的综合结果,可以为实际系统设计提供决策依据,帮助开发者选择更适合特定应用场景的仲裁策略。

总结来说,本文提供的OPB总线仲裁器设计与实现方法,不仅展示了EDA工具在SoC设计中的应用,还为FPGA开发者提供了实际的实现案例和理论基础。通过深入理解这些设计细节,开发者可以更好地理解和优化自己的SoC系统,提高系统的整体性能和效率。

2023-08-18 上传

2024-06-30 上传

2023-06-08 上传

2023-08-25 上传

2023-05-05 上传

2023-06-03 上传

weixin_38631599

- 粉丝: 9

- 资源: 944

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展