FPGA多时钟域数据同步技术及应用

需积分: 23 8 浏览量

更新于2024-09-08

1

收藏 309KB PDF 举报

FPGA跨时钟多时钟域数据同步是一种关键的信号处理技术,用于确保在不同时钟域之间可靠地交换数据,避免亚稳态问题和其他潜在的逻辑错误。在电子设计中,时钟域指的是由独立时钟信号驱动的不同部分,这些部分可能具有不同的工作频率。

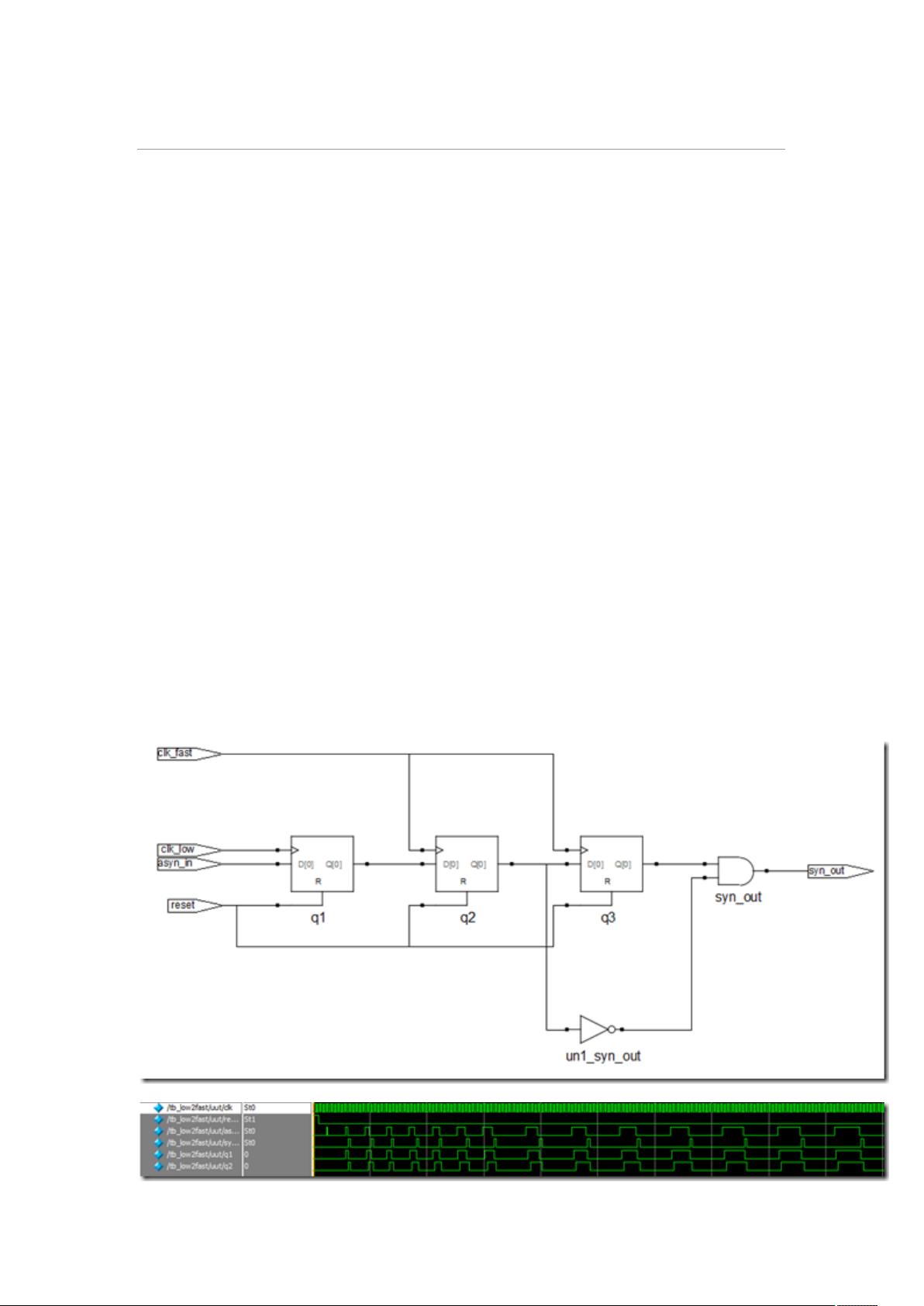

首先,当我们从慢时钟域(较低频率)向快时钟域(较高频率)传递数据时,常见的策略是通过级联延迟线和边缘检测电路。如所示的模块中,使用寄存器(q1和q2)进行两次捕捉,确保数据在适当的时间窗口内被正确采样。对于短暂的脉冲,需要确保其持续时间足够长,以便于被快速时钟域捕获。如果数据是控制信号,可以调整电路以检测特定的信号边沿,如下降沿。

然而,这种方法在处理多位数据时会遇到挑战。因为每个数据位可能需要不同长度的延迟才能达到正确的同步,如果某个数据位的到达时间不符合寄存器的建立时间,就可能导致数据之间的乱序。因此,这种方法并不适用于多路数据同步。

相反,当从快时钟域向慢时钟域传递数据时,单个数据可以通过锁存反馈机制来实现同步。例如,模块中的q1和q2通过异步触发来确保窄脉冲信号被正确地锁定并传递到慢时钟域。

在实际应用中,为了更有效地处理多位数据,特别是在时钟间存在固定频率倍数的情况下,通常采用异步FIFO(First-In First-Out,先进先出队列)来同步数据。FIFO可以保持数据的顺序,并且能适应不同时钟速度,减少采样率误差。这种方法更适用于大规模的数据传输,因为它能够处理任意时钟域间的数据流,确保数据的一致性和准确性。

FPGA跨时钟多时钟域数据同步是一项复杂的技术,它涉及选择合适的同步机制(如级联延迟线、锁存反馈或FIFO),以确保在速度和时间上匹配的条件下,数据能在不同时钟域间正确无误地传输。理解这些原理和方法对于设计高性能和低错误率的嵌入式系统至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-09 上传

2016-12-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

qq_21539875

- 粉丝: 2

- 资源: 17

最新资源

- SieveProject

- getmail-xoauth-git

- Java项目:共享自习室预约管理系统(java+SpringBoot+Thymeleaf+html+maven+mysql)

- Xshell+XFtp.zip

- MyYES ShopTool-crx插件

- AMQPStorm_Pool-1.0-py2.py3-none-any.whl.zip

- MySQL BIND SDB Driver-开源

- webscrap:网页的信息选择器

- lhyunited.github.io:主页

- hex转换成bin文件的工具

- AMQPStorm-2.4.0-py2.py3-none-any.whl.zip

- DistilBert:DistilBERT for Chinese 海量中文预训练蒸馏bert模型

- ProScheduler

- GoogleIABSampleApp

- aplica-o-de-transfer-ncias-banc-rias:.NET NET的紧急情况

- survey:AppSumo