STM32F205/STM32F207:ARM Cortex-M3 MCU,高性能,低功耗特性详解

"STM32F205 STM32F207 数据手册提供了关于STM32F2系列微控制器的初步信息,该产品正在开发或评估中,详细规格可能未最终确定。STM32F205和STM32F207是基于ARM Cortex-M3内核的32位微控制器,拥有高性能、低功耗的特点,适用于各种嵌入式应用。"

STM32F205和STM32F207是意法半导体(STMicroelectronics)推出的微控制器,它们属于STM32F2系列。这些微控制器的核心是32位ARM Cortex-M3处理器,集成了一个自适应实时加速器(ART Accelerator),使得在Flash内存中执行程序时可以实现0等待状态,最高工作频率可达120MHz。这使得STM32F205和STM32F207能够提供高达150DMIPS的性能(按Dhrystone 2.1基准测试,即1.25 DMIPS/MHz)。

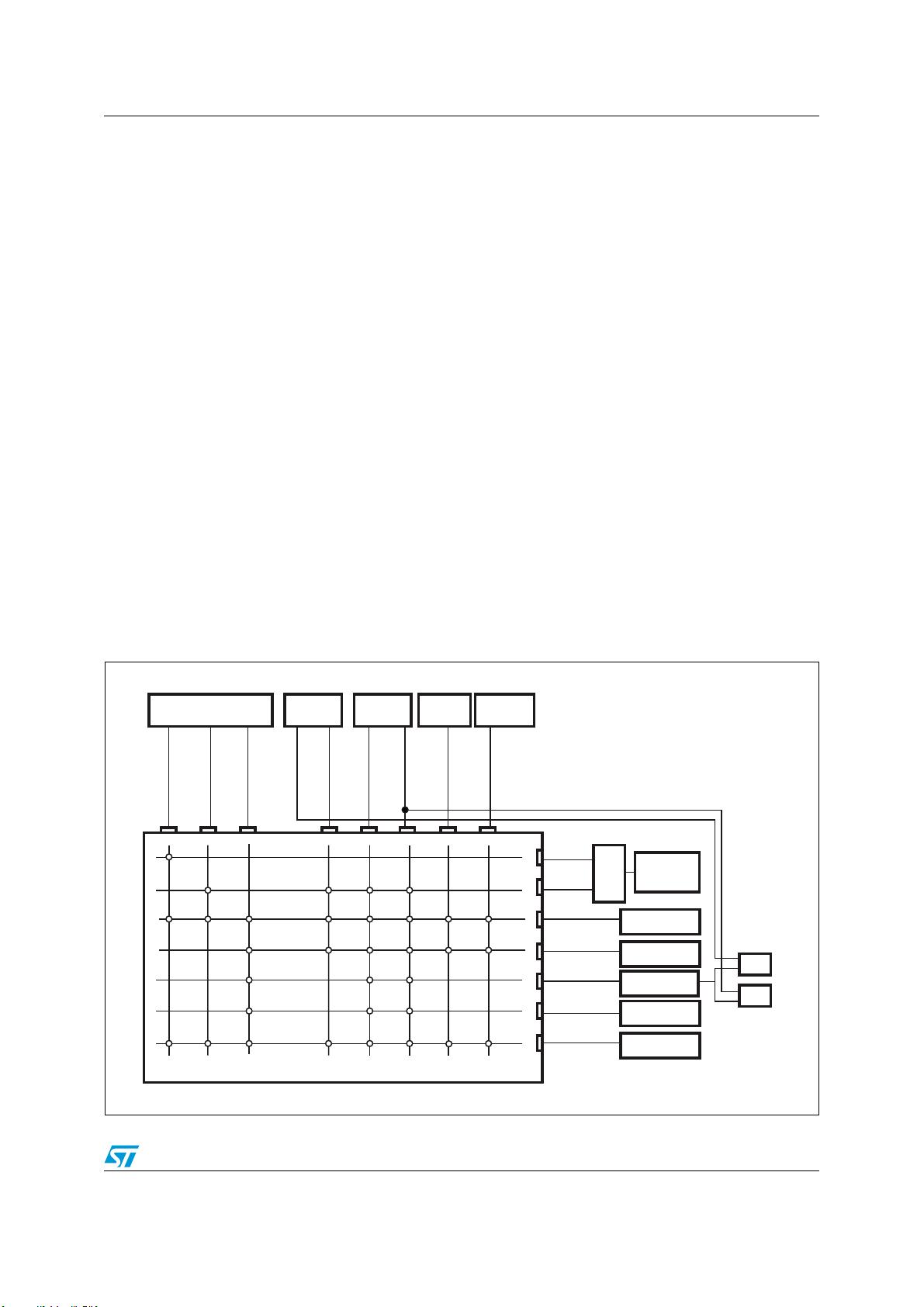

在存储方面,STM32F205和STM32F207提供最大1MB的Flash内存和最多128+4KB的SRAM。此外,还有一个灵活的静态存储器控制器,支持CompactFlash、SRAM、PSRAM、NOR和NAND等多种类型的外部存储器。它们还配备了LCD并行接口,兼容8080和6800模式,方便连接各种显示屏。

在时钟、复位和电源管理上,STM32F205和STM32F207的工作电压范围为1.8V到3.6V,支持自动复位(POR)、电源掉电复位(PDR)、电源电压检测(PVD)和过压保护(BOR)。设备内置4到26MHz的晶体振荡器,一个16MHz的工厂校准RC振荡器(精度±1%),以及一个用于RTC的32kHz振荡器,可进行校准。此外,还有一个内部32kHz RC振荡器,同样可以进行校准。

在低功耗特性上,STM32F205和STM32F207支持睡眠、停止和待机三种模式,以适应不同应用场景下的节能需求。在通信接口方面,它们提供多达17个定时器和3个ADC,以及15种不同的通信接口,包括USB OTG HS/FS(高速/全速)和以太网,这使得它们能广泛应用于需要高速数据传输和网络连接的场合。

STM32F205和STM32F207是针对高性能、低功耗应用设计的微控制器,适合于工业控制、物联网设备、消费电子等多个领域。其强大的处理能力、丰富的外设接口和灵活的电源管理方案,使得它们成为嵌入式系统设计的理想选择。

142 浏览量

296 浏览量

点击了解资源详情

519 浏览量

538 浏览量

142 浏览量

296 浏览量

103 浏览量

2019-09-05 上传

wuguoyana

- 粉丝: 30

最新资源

- 微软发布VS2008编译错误C1859修复补丁KB976656

- VR_audioscape:Google Summer of Code 2017的VR音频应用开发

- 一键优化系统性能:高效卸载与清理

- NumSharp让.NET开发人员享受NumPy语法与高效内存访问

- 检测普通对象的JavaScript库:is-plain-obj

- 前端至全栈技术项目源码合集 - 学习与实践资源包

- 解决Tomcat启动异常:未找到APR库tcnative-1.dll

- 深入解析HTML5: 语义、标准与样式指南

- Carpeaqua模板:构建与部署Ghost主题指南

- 腾达BCM5357C0芯片固件救砖教程

- React与Rust编译WebAssembly的样板应用实践

- UBOOT 1.1.6下SDHC和MMC驱动支持实现

- React Native滑动按钮组件RNSwipeButton的功能与应用

- 一键修复IE错误 强力回归原始主页

- 全面技术覆盖的vc商城v1.30源代码及学习指南

- WC-Fontawesome:简化Font Awesome v5的Web组件集成