XILINX FPGA AXI开发全面指南

需积分: 14 112 浏览量

更新于2024-07-19

3

收藏 5.34MB PDF 举报

"XILINX FPGA AXI开发 参考文档"

Xilinx FPGA AXI(Advanced eXtensible Interface)开发参考文档是针对基于Xilinx FPGA的系统设计者的重要参考资料,该文档通常会涵盖AXI协议的详细信息,以及如何在Xilinx FPGA平台上实现和优化AXI接口的设计。AXI是业界广泛采用的一种高性能、高带宽的片上互连协议,它允许不同的处理元素,如处理器、存储器和外设之间高效地交换数据。

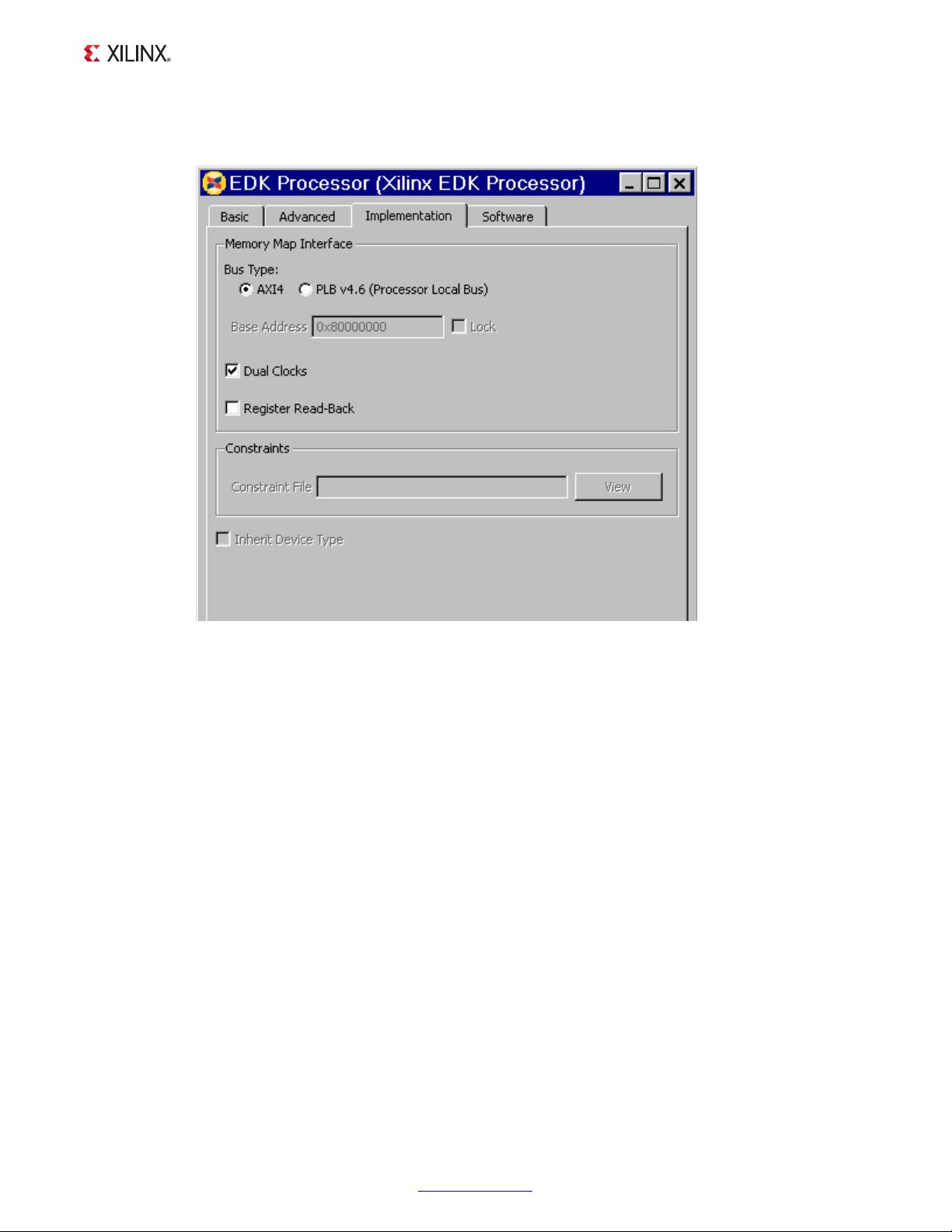

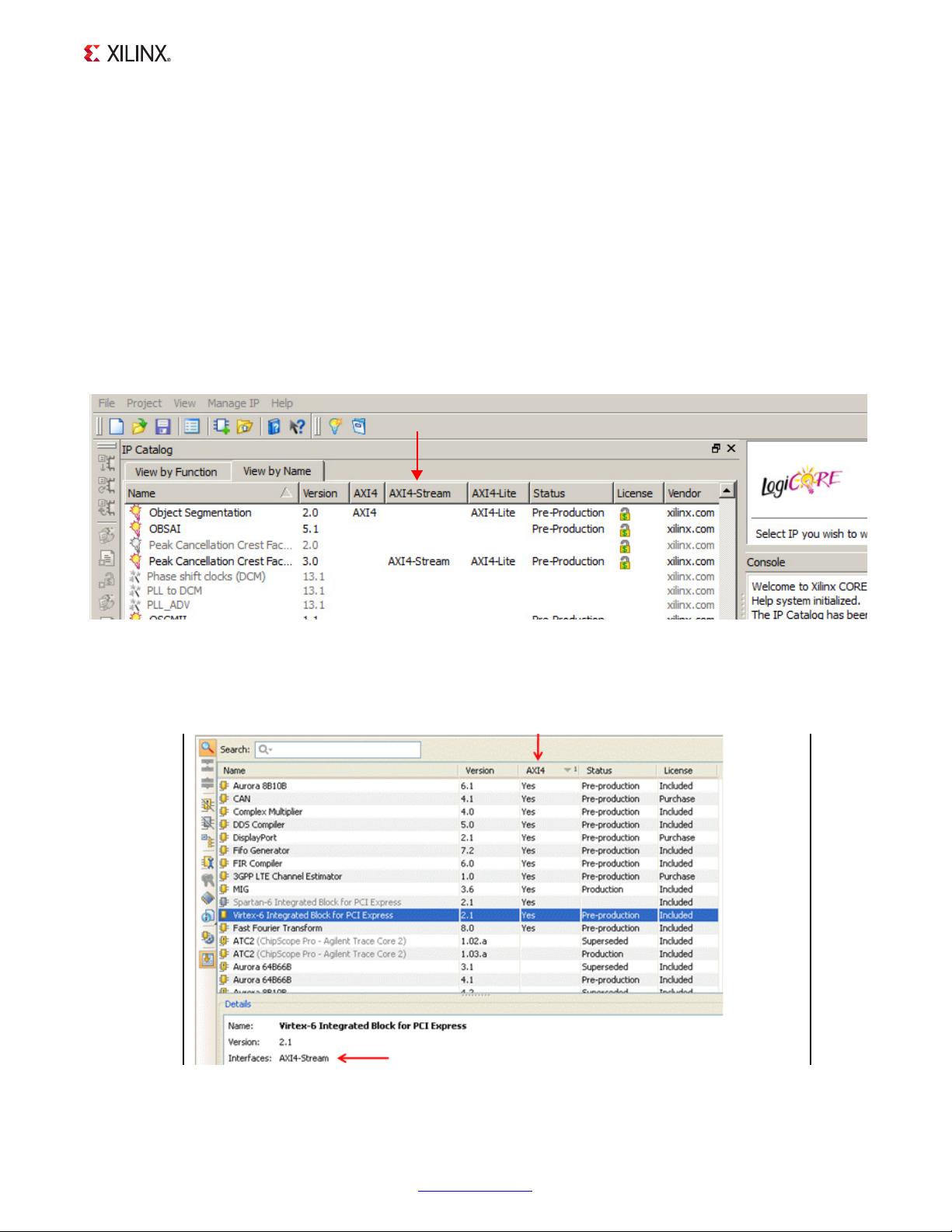

文档版本为UG761(v14.3),发布于2012年11月15日,提供了对AXI协议的全面指南,包括基础概念、架构、时序、协议规范和设计实例。AXI协议有多种类型,例如AXI4、AXI4-Lite和AXI4-Stream,每种类型适用于不同的应用场景,如控制平面和数据平面通信。

在该文档中,你可能会找到以下关键知识点:

1. **AXI协议概述**:AXI协议的核心特性,包括写和读事务的流程,总线宽度(数据通道和地址通道),以及仲裁机制。

2. **AXI组件**:包括主设备(Master)、从设备(Slave)、仲裁器(Arbiter)和桥接器(Bridge)等,它们如何协同工作以实现高效的通信。

3. **AXI接口信号**:详细说明了地址、数据、控制和响应信号的定义和使用,这些信号定义了AXI接口的电气特性。

4. **AXI4与AXI4-Lite的区别**:AXI4-Lite是AXI4的一个简化版本,主要用于轻量级控制信号传输,没有独立的写应答和读应答通道。

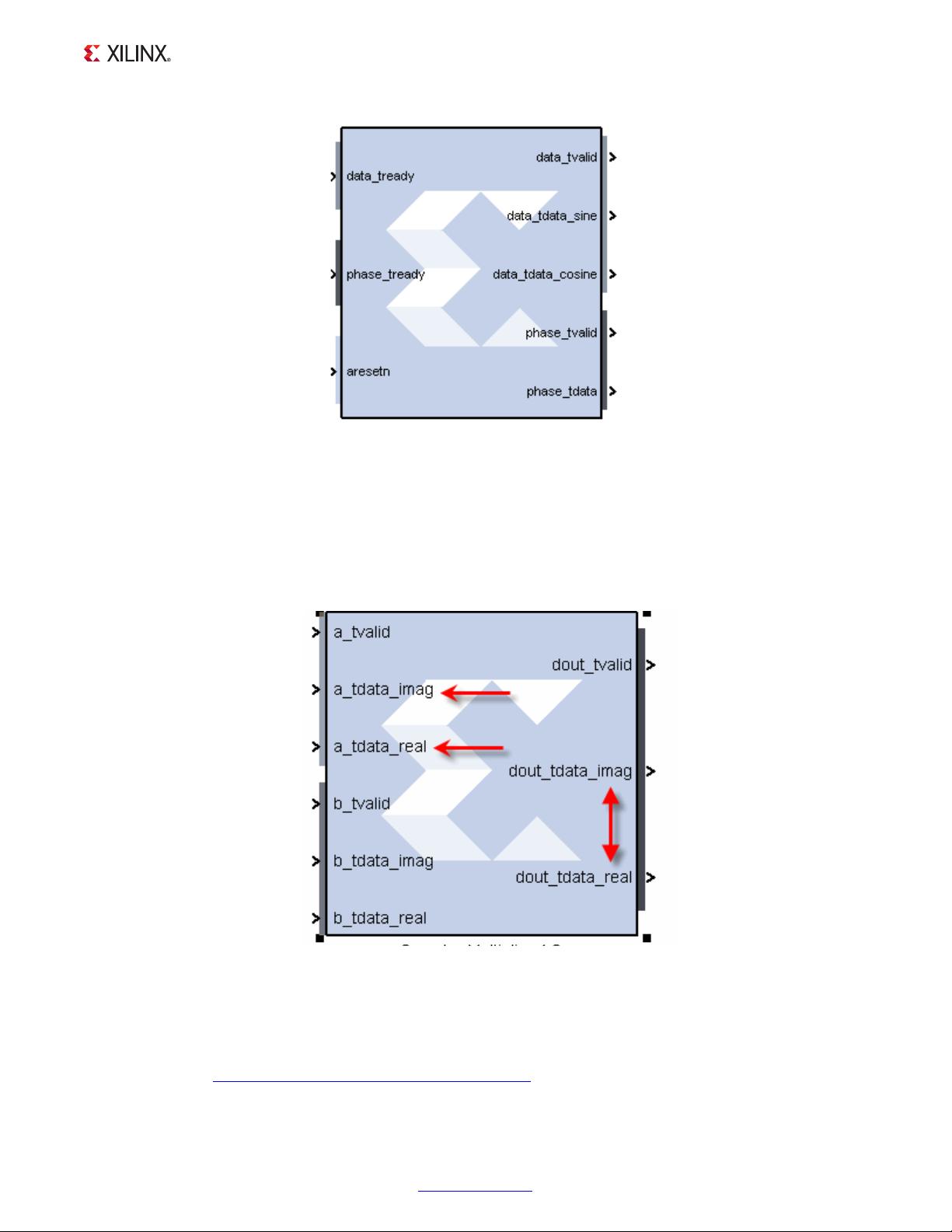

5. **AXI4-Stream**:用于无缓冲的数据流传输,常用于高速信号处理和DMA(直接内存访问)应用。

6. **设计实例**:文档可能包含具体的硬件描述语言(如VHDL或Verilog)代码示例,展示了如何在FPGA设计中集成和配置AXI接口。

7. **性能优化**:指导如何通过参数化、流水线设计和时序分析来提高AXI接口的性能。

8. **工具支持**:可能涵盖Xilinx的Vivado或其他设计工具如何支持AXI设计,包括IP核集成、仿真和验证。

9. **故障排查**:提供常见问题和解决方案,帮助开发者解决在实现AXI接口时遇到的问题。

10. **知识产权(IP)核**:Xilinx提供的预配置AXI IP核,如DMA控制器、AXI交叉开关等,以及如何将这些IP核集成到设计中。

尽管Xilinx提供这些材料供选择和使用,但文档明确指出,所有信息都是“按原样”提供,不提供任何明示或暗示的保修,包括但不限于适销性、非侵权性和特定目的适用性的保修。同时,Xilinx对因使用这些材料而产生的任何损失或损害不承担法律责任。

请注意,由于没有提供具体内容,以上解释是基于一般AXI开发文档的典型内容。在实际文档中,会有更详细的描述和技术细节。

575 浏览量

2023-06-29 上传

179 浏览量

441 浏览量

点击了解资源详情

126 浏览量

qq_16739273

- 粉丝: 0

- 资源: 1

最新资源

- 10-Days-of-[removed]该存储库包含针对Hackerrank的10天Javascript挑战的代码解决方案

- 初级java笔试题-jwasham:杰瓦萨姆

- commons-net-jar包.zip

- seed-datepicker:Seed框架的可自定义的datepicker组件

- Bloc_Api_token

- lxdfile:LXD容器的类似于Dockerfile的文件格式

- 蔬菜品种的分类——果菜类

- Unity 2018.1 中文手册 中文文档

- pugsql:一个受HugSQL启发的Python数据库库

- 人机交互项目

- abpMVC.zip

- 生鲜商品:超市生鲜食品经营要求

- Shipped.io Iraq-crx插件

- Machine-Learning-Project:机器学习天气对酒点的影响

- ENV Alert - 本番環境で警告表示-crx插件

- lain:Rust内置的Fuzzer框架