基于Verilog HDL的十进制计数器设计与实现

版权申诉

188 浏览量

更新于2024-06-11

1

收藏 1.79MB DOCX 举报

"基于HDL十进制计数器设计概要"

本资源主要介绍了基于HDL的十进制计数器设计,涵盖了FPGA实验报告、VerilogHDL语言描述数字电路、组合和时序逻辑电路设计方法、LED七段码波形仿真分析、译码器设计、HDL语言判断CLK上升沿信号、计数器值加一并显示在数码管上等知识点。

**一、FPGA实验**

FPGA实验是基于HDL的十进制计数器设计的基础实验,实验名称为基于HDL十进制计数器设计,实验步骤包括设计准备、十进制计数器设计、驱动七段数码管模块设计、消抖模块设计等。

**二、VerilogHDL语言描述数字电路**

VerilogHDL语言是描述数字电路的主要语言,本实验中使用VerilogHDL语言描述了十进制计数器的设计,包括输入信号、输出信号、计数器值加一并显示在数码管上等。

**三、组合和时序逻辑电路设计方法**

组合和时序逻辑电路设计方法是数字电路设计的主要方法,本实验中使用了组合和时序逻辑电路设计方法设计了十进制计数器,包括输入信号、输出信号、计数器值加一并显示在数码管上等。

**四、LED七段码波形仿真分析**

LED七段码波形仿真分析是本实验的主要内容之一,通过仿真分析,可以了解到十进制计数器的工作原理和显示结果。

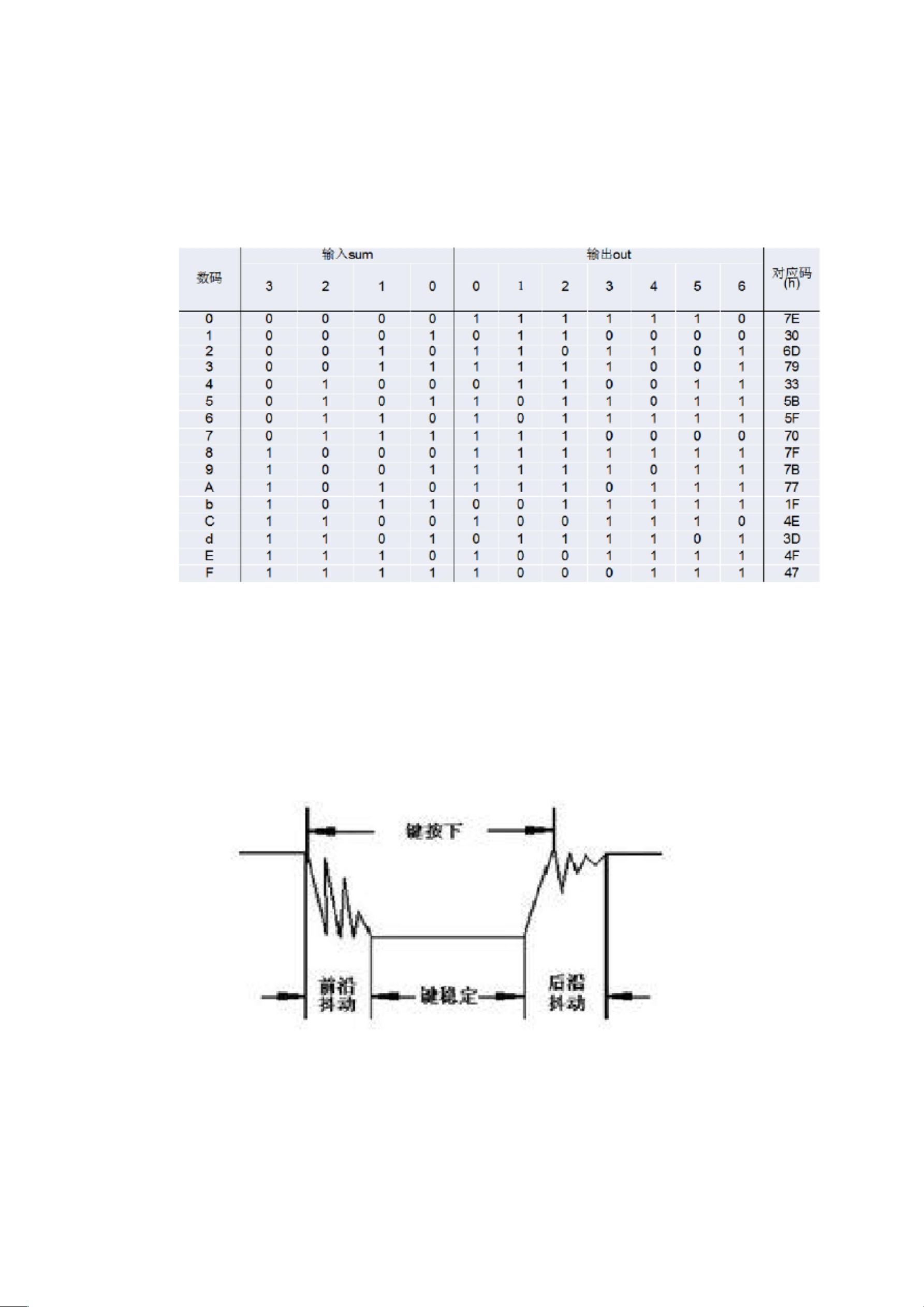

**五、译码器设计**

译码器设计是本实验的主要内容之一,通过译码器设计,可以将十进制计数器的值显示在七段数码管上。

**六、HDL语言判断CLK上升沿信号**

HDL语言判断CLK上升沿信号是本实验的主要内容之一,通过HDL语言可以判断CLK上升沿信号,并将计数器值加一并显示在数码管上。

**七、计数器值加一并显示在数码管上**

计数器值加一并显示在数码管上是本实验的主要内容之一,通过计数器值加一并显示在数码管上,可以了解到十进制计数器的工作原理和显示结果。

**八、消抖模块设计**

消抖模块设计是本实验的主要内容之一,通过消抖模块设计,可以对按键输入信号进行消抖处理,避免按键抖动对实验结果的影响。

本资源主要介绍了基于HDL的十进制计数器设计,涵盖了FPGA实验报告、VerilogHDL语言描述数字电路、组合和时序逻辑电路设计方法、LED七段码波形仿真分析、译码器设计、HDL语言判断CLK上升沿信号、计数器值加一并显示在数码管上等知识点。

173 浏览量

143 浏览量

2022-11-07 上传

2022-11-01 上传

104 浏览量

130 浏览量

171 浏览量

358 浏览量

xxpr_ybgg

- 粉丝: 6806

- 资源: 3万+

最新资源

- 教育组织领导与激励

- visual c++ vc++收发电子邮件.zip

- easy-location-br:轻松查找巴西各州和城市

- 电子-IAR工程模板.zip

- 易语言源码易语言监视热键例程源码.rar

- SQLite-1.0.65.0-setup.exe

- GenAlgo.zip_matlab例程_matlab_

- 模仿华丽彩虹音频播放器程序源代码,打造炫彩视听体验

- 教育科研课题的全程管理

- AndroidBackBlazeHelper:Android BackBlaze Helper是一个android库,可让Backblaze功能易于使用

- 检测图像偏斜角和偏斜图像

- hsms:HSMS协议JavaScript驱动程序

- 易语言源码易语言监视文件夹源码.rar

- 电子-16液晶屏LCD1602.zip

- 上汽大众天宝869主机5111升级固件

- dpd.zip_matlab例程_matlab_