VHDL实现:4位电子密码锁设计与分析

版权申诉

36 浏览量

更新于2024-06-25

收藏 153KB DOCX 举报

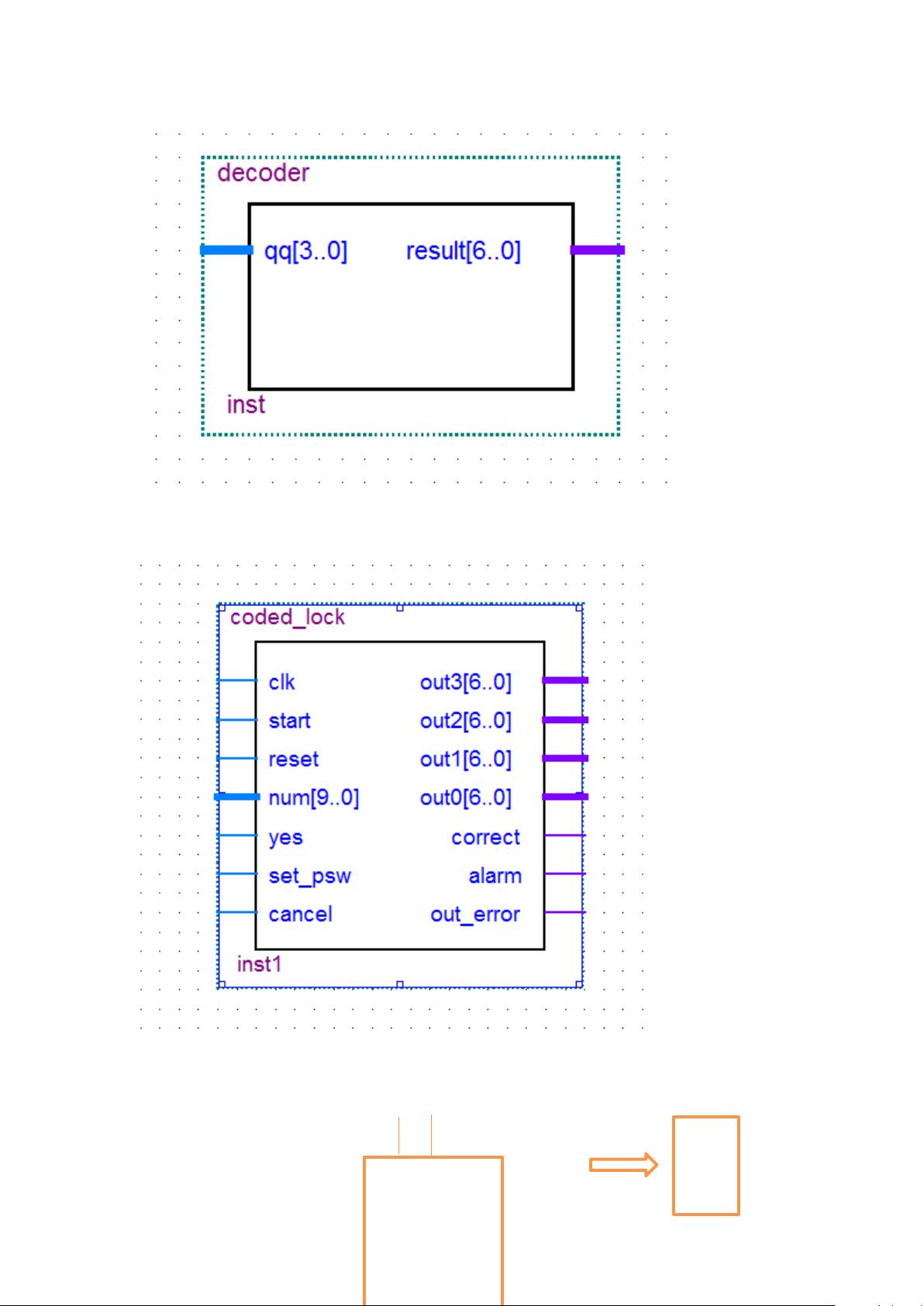

该文档是大连理工大学本科实验报告,涉及基于VHDL的4位电子密码锁设计。实验目标是设计一个能接受4位8421BCD码的密码锁,具有错误输入提示、三次输入机会、报警功能以及密码重置功能。密码输入通过DE2开发板上的switch实现,显示部分采用7段数码管。系统由输入译码、显示、控制、比较和重置以及LED显示等模块组成。

1. 设计要求:

- 密码锁为4位,超过4位时只取前4位有效数字。

- 错误输入时,系统提供三次重试机会,三次都错则触发报警。

- 输入正确后,用户可重新设置密码。

- 每次输入一个数字,会在7段数码管上显示并左移。

- 可通过取消键清除当前输入,重新开始输入密码。

2. 设计分析与系统方案:

- 使用DE2开发板的switch作为输入,通过译码模块转换成8421BCD码以驱动7段数码管。

- 通过模4计数器限制输入密码的长度,模3计数器跟踪输入次数。

- 密码比较模块比较输入密码与预设密码,匹配则解锁,不匹配则锁定。

- LED显示模块提供视觉反馈,正确密码显示绿色,错误显示红色。

3. 硬件电路设计:

- 显示模块: 采用共阳极型四段数码管,用于显示输入密码和状态。

- 输入译码模块: 利用switch[9]至switch[0]模拟数字键,通过译码器转换成BCD码。

- 控制模块: 实现输入控制,包括输入计数和错误计数。

- 比较和重置模块: 对比输入密码与预设密码,匹配时允许重置密码。

- LED显示模块: 输出高电平控制LEDG(绿灯)或LEDR(红灯),表示密码状态。

4. VHDL编程实现:

- 在VHDL中,需要定义各个模块的接口,如输入信号 clkClk_in、Out_q、Psw 和输出信号等。

- 设计和编写密码输入模块、译码模块、计数器模块、比较模块和LED控制模块的VHDL代码。

- 通过综合和仿真工具验证各个模块的功能,确保设计正确无误。

5. 实验步骤与注意事项:

- 实验前理解8421BCD码原理和7段数码管显示逻辑。

- 编写并测试VHDL代码,确保每个模块功能独立且正确。

- 集成所有模块,进行系统级仿真,检查整个密码锁系统的完整性和功能。

- 实际硬件验证,调试可能存在的硬件连接或逻辑问题。

6. 总结:

这个实验项目旨在提升学生的数字电路设计能力和VHDL编程技巧,通过实际操作加深对数字逻辑系统设计的理解,为将来更复杂的系统设计打下基础。

2023-02-27 上传

2023-02-27 上传

2023-02-27 上传

2023-02-27 上传

2021-12-11 上传

2024-11-30 上传

2022-10-14 上传

2023-04-26 上传

2011-07-08 上传

老帽爬新坡

- 粉丝: 97

- 资源: 2万+

最新资源

- Accuinsight-1.0.4-py2.py3-none-any.whl.zip

- yama:Yama的编译器,一种面向对象的微控制器语言,例如ARM Cortex-M和AVR

- ap-event-lib:事件框架库

- 队列分析

- docker-compose2.172下载后拷贝到/usr/local/bin下

- webstore

- Employee-Summary

- media-source-demo:媒体源演示

- 家:普拉特姆学院

- LilSteve:第175章

- tilde-world

- Accuinsight-1.0.25-py2.py3-none-any.whl.zip

- 标题栏随着RecyclerView滚动背景渐变

- 浏览器自定义查看pdf文件.rar

- 直接序列扩频(DS SS):这是直接序列扩频的代码。-matlab开发

- flutter_dylinkios_sample:使用Dart的示例项目