and is much better than that of DRAM. However, the write latency

of MRAM is much larger than that of SRAM and DRAM. The coming

generation [53] of MTJ devices will reduce the energy consumption

for per-switching to be values around 1 fJ, which is in the same

order as the CMOS switching energy.

In [54], Dong et al. introduce and evaluate stacking MRAM on

top of a microprocessor as a 3D IC. The simulation results show

that though the performance benefit of MRAM is not obvious, the

real benefit of MRAM is the power consumption. Using MRAM

caches to implement L2 caches can save total power by 89% com-

pared with SRAM caches and by 70% compared with DRAM caches.

It is also attractive to build buffers in on-chip routers by scalable

MTJ devices which can save the dynamic power [55].

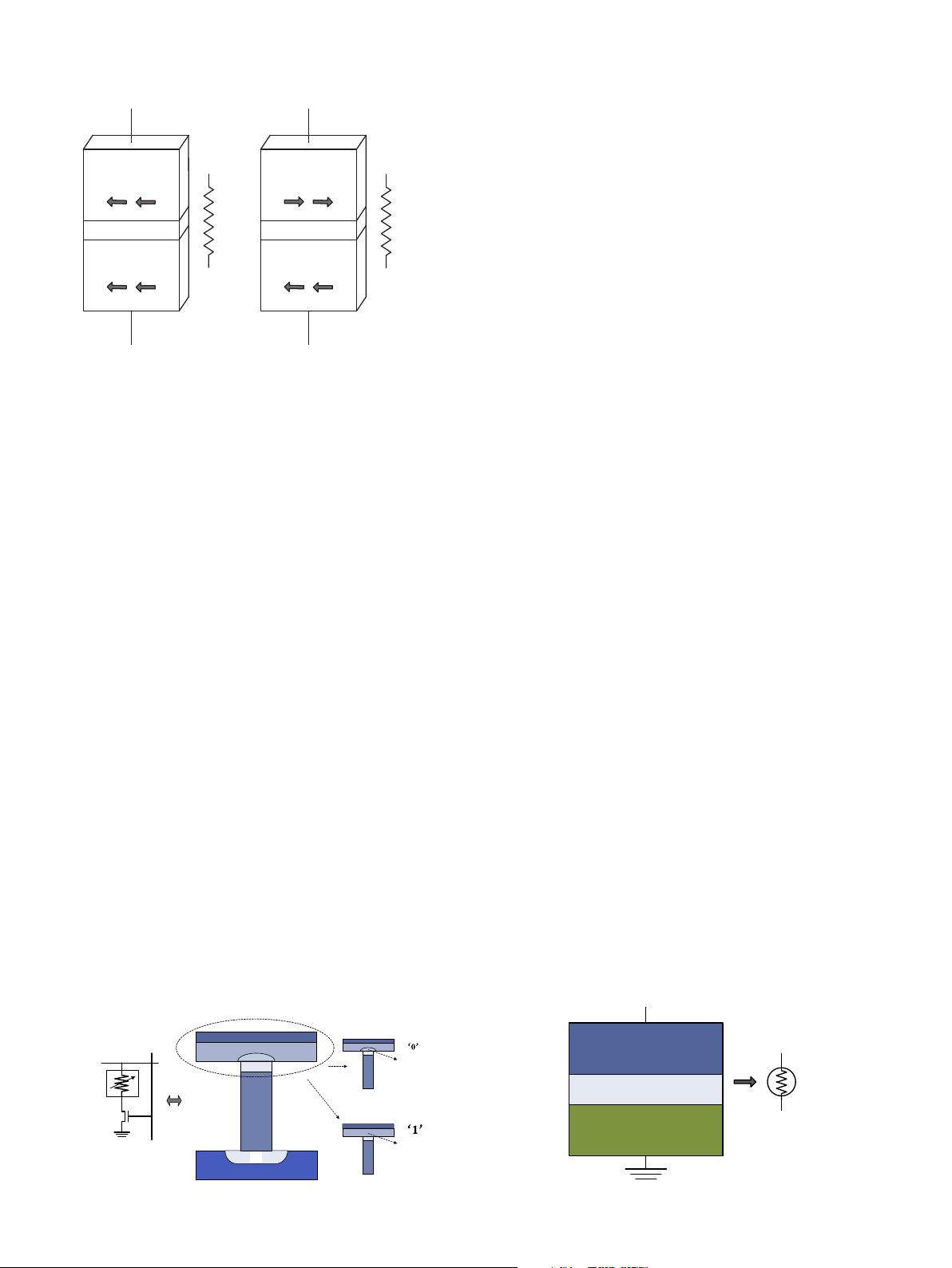

2.3.2. PCRAM

Phase-change RAM (PCRAM) [56,57] is a kind of non-volatile

memory that exploits the property of chalcogenide glass, typically

Ge

2

Sb

2

Te

5

(GST) material. PCRAM can be switched between two

states, amorphous and crystalline. Fig. 6 gives a basic structure of

PCRAM cell.

The amorphous phase has low optical reflexivity and high elec-

trical resistivity. The crystalline phase shows high reflectivity and

low resistivity. The difference in resistance of the two states can

be used to present logical states of binary data. During writes, an

access transistor injects current into the storage material and ther-

mally induces phase change, which is detected during reads. A

phase-change material can be switched from one phase to another

reliably, quickly, and a large number of times. For instance, 420 nm

diameter Ge

2

Sb

2

Te

5

devices can be SET/RESET (recrystallized/rea-

morphized) in 90/1.5 ns, and 19 nm diameter devices can be

switched in 2.5/0.4 ns [58]. PCRAM write endurance, which is the

number of writes performed before the cell cannot be programmed

reliably, is about 10

8

cycles [59] and is expected to be 10

15

in 2015

[60]. PCRAM can act as a scalable DRAM alternative solution for

increasing main memory density and capacity.

Lee et al. [61] propose a memory architecture that lays the

foundation for exploiting PCRAM scalability and non-volatility as

main memory. Energy of PCRAM scales down 1.6 times more

quickly than that of DRAM. At 40 nm, PCRAM system energy is

61.3% that of DRAM on averaged. In [62], Qureshi et al. analyze a

PCRAM-based hybrid main memory system using an architecture

level model of PCRAM. They explore the trade-offs for a main

memory system consisting of PCRAM storage coupled with a small

DRAM buffer. Dong et al. [63] present a PCRAM model, called

PCRAMsim, to bridge the gap between the device-level and sys-

tem-level research on PCRAM technology. In [64], Joo et al. study

a set of techniques to design an energy- and endurance-aware

PCRAM cache. The timing, energy, endurance, and area of PCRAM

caches are molded and integrated into a PCRAM cache simulator.

Readers can refer to [65], which gives a very good overview on

MRAM and PCRAM memories.

2.3.3. RRAM

Memristor-based resistive RAM (RRAM, also known as OxRAM,

ReRAM) [66–69] has the property of fast access, zero standby leak-

age, non-volatility, multilevel capability, and relatively small write

power consumption. Hence RRAM becomes one of the most prom-

ising next-generation universal memory candidates. Most of

metal-oxide RRAM cell structures are composed of vertically

stacked metal/metal-oxide/metal layers. The metal-oxide can be

NiO [70], TiON [71], TiO

2

[72], etc. RRAM stores data based on

resistance difference. The high resistance state (HRS) represents

logic ‘0’ and low resistance state (LRS) denotes ‘1’. Fig. 7 shows a

simplified schematic of the conventional structure for RRAM. A

voltage larger than the set voltage is needed to trigger on the resis-

tive switching behaviors for the subsequent cycles. The RRAM can

be stacked in 3D as a crosspoint architecture. The memory cell area

can be 4 F

2

/n, where F is the minimum feature size and n is the

number of 3D stacked memory layers [66].

Lewis and Lee [73] give an overview of the memristors that

have been produced by a number of different research teams and

propose a point-by-point comparison between DRAM and RRAM,

based on both existing and expected near-term memristor devices.

The density of RRAM is about 10 times higher than that of DRAM.

Though still suffering from a few shortcomings, RRAM shows itself

to be a potential design alternative to well-established DRAM tech-

nology. Chang et al. [74] survey design challenges associated with

low-voltage SRAM, memristor logic, and RRAM. The authors study

integrating low-voltage RAM, RRAM and memristor logic in 3D ICs.

The power consumption and thermal stress can be reduced. In [75],

Chen et al. propose a RRAM based FPGA. Comparing with modern

FPGA with SRAM, RRAM-based FPGA shows benefits of non-volatil-

ity, smaller area, and flexibility of configuration.

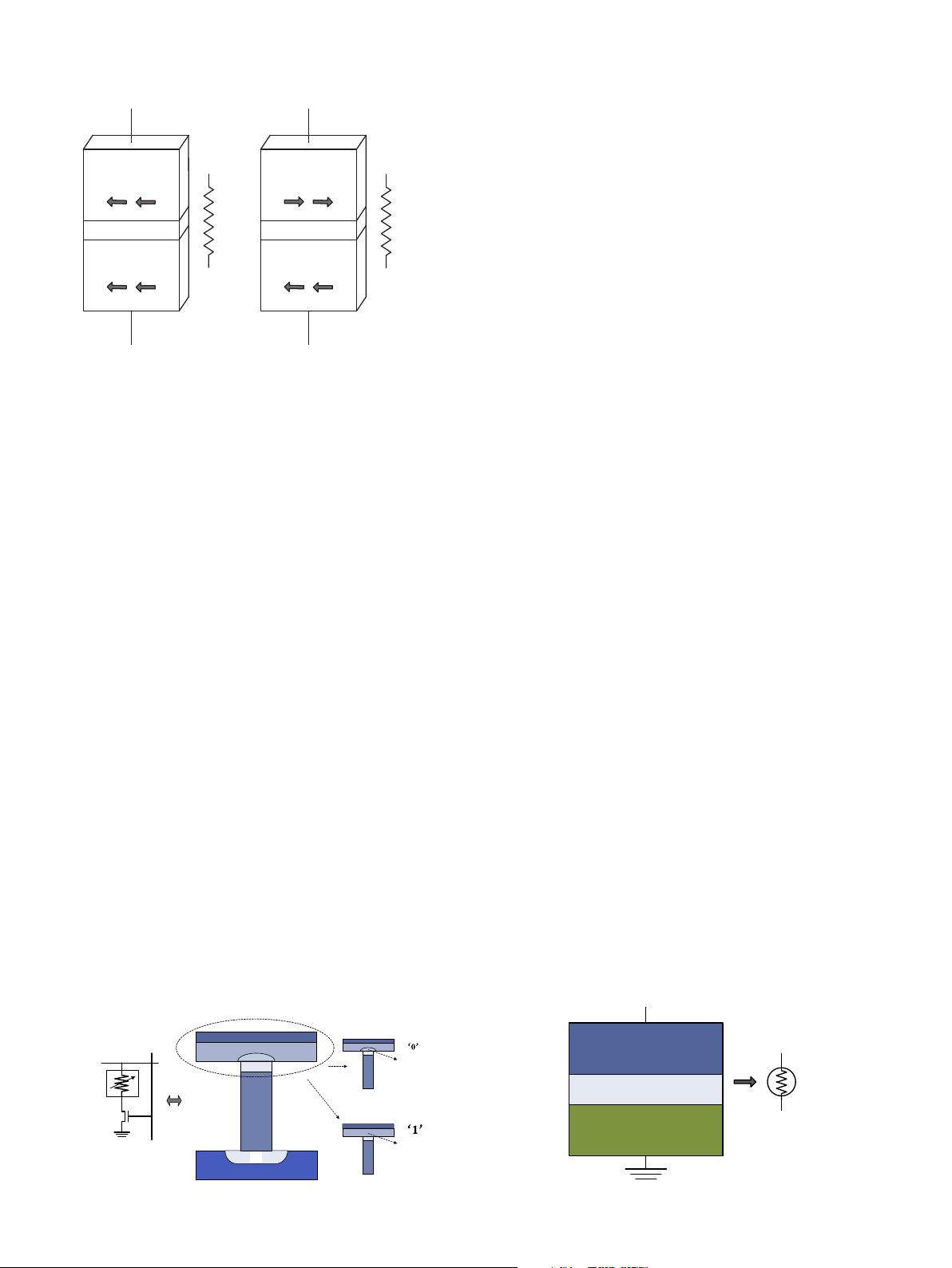

Fixed Layer

Free Layer

Tunnel Barrier

Fixed Layer

Free Layer

Tunnel Barrier

R

LOW

R

HIGH

(a) (b)

Fig. 5. MTJ structure in its two states (a) parallel and (b) anti-parallel.

Substrate

N+

Heater

GST

Top Electrode

amorphous

state

crystalline

state

Bitline

Wordline

Storage

Bottom

Electrode

Fig. 6. The basic structure of a PCRAM cell.

Top Electrode

Bottom Electrode

Metal Oxide

Voltage

Fig. 7. Structure schematic for metal-oxide RRAM.

418 Y. Zhang et al. / Microprocessors and Microsystems 38 (2014) 415–430

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功